Устройство для формирования адресов при выполнении быстрого преобразования фурье

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ ПРИ ВЫПОЛНЕНИИ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее счетчик итераций и счетчик адресов, причем вход счетчика адресов является тактовым входом устройства по входу счетчика итераций, о т л и .чающееся тем, что, с целью повьшения быстродействия устройо тва. введены R коммутаторов (R - разрядность формируемого адреса), причем первый информационный вход первого коммутатора подключен к выходу первого разряда (со стороны младших разрядов) счетчика адреса, первьй информационный вход, а также информационные входы с (R +3-0-го по ()-й i -го (-i 2-R) коммутатора подключены к выходу ij -го разряда счетчика адреса, информационные входы со второго по (Я-|-2-))-й j -го (j 1-R) коммутатора подключены к выходам разрядов счетчика адреса с (R+1-})-ro по первый соответственно , выход счетчика итераций подклюk чен к управляющим входам всех коммутаторов , выход j -го коммутатора является выходом j-го разряда адреса устройства.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (и) Зсю C 06 F 15/332

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2,1) 3429806/18-24 (22) 21.01.82 (46) 07.04.84. Бюл. В 13 (72) Н.И. Козленко, А.Ю. Ядрихинский и Ю.В. Левченко (53) 681.3(088.8) (56) 1. Авторское свидетельство СССР

В 548863, кл. G 06 F 15/332, 1975.

2. Авторское свидетельство СССР

В 877555, кл. С 06 F 15/332, 1979 (прототип}. ,(54)(57) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ ПРИ ВЫПОЛНЕНИИ БЫСТРОГО

ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее счетчик итераций и счетчик адресов, причем вход счетчика адресов являет ся тактовым входом устройства по входу счетчика итераций, о т л и.ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, введены R коммутаторов (Н вЂ” разрядность формируемого адреса), причем первый информационный вход первого коммутатора подключен к выходу первого разряда (со стороны младших разрядов) счетчика адреса, первый информационный вход, а также информационные входы с (R +3-1)-го по (Я+1)-й 1 -го (= 2-R) коммутатора подключены к выходу q --ro разряда счетчика адреса, информационные входы со второго по (К+2-j)-й j -ro (j= 1-Й) коммутатора подключены к выходам разрядов счетчика адреса с (R+1-))-го по первый соответственно, выход счетчика итераций подключен к управляющим входам всех коммутаторов, выход 1 -го коммутатора является выходом 1 -го разряда адреса устройства.

1084808

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств, реализующих быстрое преобразование, Фурье. 5

Известно устройство для формирования адресов, содержащее счетчик адресов, узел реконфигурации счетчика адресов, регистр, группу элементов ИЛИ, блок выдачи адресов (1) .

Наиболее близким к изобретению по технической сущности является устройство для формирования адресов в составе Фурье-преобразователя, содержащее счетчик итерации, счетчик 15 адреса и дешифратор, причем счетный вход счетчика адресов является тактовым входом устройства, выход переполнения

I счетчика адресов подключен к входу счетчика итераций, выход которого 20 через дешифратор подключен к управляющему входу реконфигурации счетчика адресов (2) .

Недостатком известных устройств является низкое быстродействие.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для формирования адресов при выполнении быстрого

30 преобразования Фурье, содержащее счетчик итераций и счетчик адресов, причем вход счетчика адресов является тактовым входом устройства, а выход переполнения счетчика адресов подключен к входу счетчика итераций, введены R коммутаторов (R -разрядность формируемого адреса), причем первый информационный вход первого коммутатора подключен к выходу первого разряда (со стороны мяадших разрядов) счетчика адреса, первый информационный вход, а также информационные входы с (R +3- )-го по (Я +1)-й -ro (4 = 2-К) коммутатора 45 подключены к выходу -го разряда счетчика адреса, информационные входы со второго по (Я +2-j)-й j --го (= 1-R) коммутатора подключены к выходам разрядов счетчика адреса®с 50 (1+1-))-го по первый соответственно, выход счетчика итераций подключен к управляющим входам всех коммутаторов, выход -го коммутатора является выходом -го разряда адреса устрой- 55

1 ства.

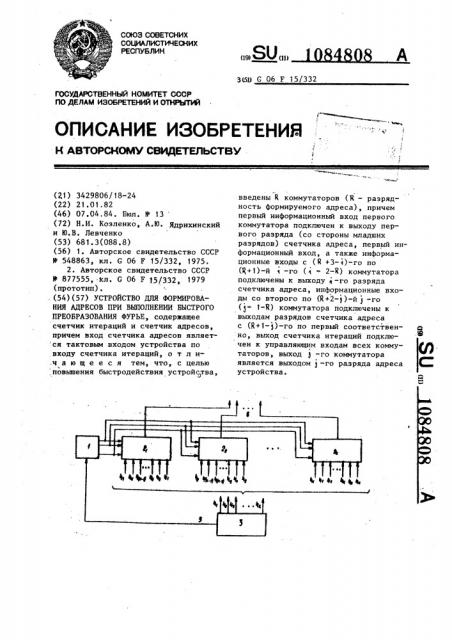

На чертеже представлена функциональная схема устройства для формировання адресов при выполнении быстрого преобразования Фурье.

Устройство содержит счетчик 1 итераций, коммутаторы 2 -21,, счетчик

3 ðåñoà, в йоды 4 i 4К разрядов счетчика адресов, выход 5 переполнения счетчика адресов, выходы б устройства.

Устройство работает следующим образом.

Начальное состояние счетчика итераций соответствует формированию адресов, по которым записываются отсчеты анализируемого входного сигнала. Эти адреса равны номерам отсчетов и задаются счетчиком 3 адресов, разряды которого через соответствующие коммутаторы 2 в порядке возрастания номера разряда подключаются к выходам 6 устройства.

Последующие состояния счетчика1 итераций соответствуют номерам выполненных итераций.

На первой итерации для выполнения базовой операции "бабочки" достаточно инвертировать порядок следо вания разрядов счетчика 3 адреса для полученич соответствующего адреса.

На второй итерации необходимо осуществить инверсию только первых -1 разрядов счетчика 3 адреса не меняя положения Я -го разряда счетчика 3 адреса. На третьей итерации инвертируются только первые 1 -2 разря.да счетчика 3 адреса без изменения положения двух последних старших разрядов и т.д. Таким образом, на

Я -м этапе преобразования порядок следования разрядов счетчика 3 адреса оказывается первоначальным (как при записи входной информации).

Описанная перегруппировка адресов происходит с помощью коммутаторов 2, на выходе каждого из которых появляется последовательно один из Я +1 входных сигналов коммутатора. При этом управление переключением входных сигналов осуществляется счетчиком 1 с частотой, равной частоте переполнения счетчика 3 адреса.

Быстродействие предлагаемого устройства ограничивается в основном задержками в коммутаторах. Эти saдержки могут быть достаточно малыми ввиду того, что каждое соединение в коммутаторе, может быть осуществлено, например, двухвходовым элеменз 1084808 том И. В известном устройстве требуется значительно большее время формирования адреса, так как оно определяется задержками в дешифраторе и последовательно соединенных с ним сложных внутренних логических цепях перестройки внутренней структуры счетчика адреса.

Заказ 2012/44 Тираж 699 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель В. Байков

Редактор. О. Бугир Техред M.Тепер КорректорМ.Шарощи