Усилитель считывания

Иллюстрации

Показать всеРеферат

УСИЛИТЕЛЬ СЧИТЫВАНИЯ, содержащий два переключающих транзистора, сток первого из которых соединен с затвором второго переключающего транзистора, сток которого соединен с затвором первого переключающего транзистора, истоки переключающих транзисторов объединены и подключены к первой шине управления, два нагрузочных транзистора, стоки которых объединены , а истоки подключены к стокам переключающих транзисторов, балансный транзистор , исток которого соединен с истоком первого нагрузочного транзистора, сток - с истоком второго нагрузочного транзистора , а затвор - с затворами нагрузочных транзисторов и второй шиной управления, конденсаторы, транзисторы регенерации, затворы которых объединены и подключены к третьей щине управления, а истоки соединены с одними обкладками конденсаторов, другие обкладки которых подключены к четвертой шине управления, отличающийся тем, что, с целью повышения степени интеграции устройства, в него введены четыре разделяющих транзистора, причем истоки первого и второго разделяющих транзисторов подключены к стоку первого переключающего транзистора, а истоки третьего и четвертого разделяющих транзисторов подключены к стоку второго переключающего транзистора, стоки первого и третьего разделяющих тран 2 @ зисторов подключены соответственно к стокам первого и второго транзисторов регене (Л рации, затворы первого и третьего, второго и четвертого разделяющих транзисторов подключены соответственно к пятой и щестой щинам управления, истоки разделяющих транзисторов являются информационными входами усилителя считывания. ас 4 00 00 со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1084889 A

3(5D G 11 С 700

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

) ф » 1 i: c:.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3532148/18-24 (22) 30.12.82 (46) 07.04.84. Бюл. № 13 (72) А. С. Ильюшенков, А. И. Макаров, В. Д. Мешанов и Н. А. Телицын (53) 681.327.6 (088.8) (56) 1. Патент США № 4158241, кл. G 11 С 7/06, опублик. 1981.

2. Авторское свидетельство СССР № 769617, кл. G 11 С 7/00, 1980 (прототип). (54) (57) УСИЛИТЕЛЬ СЧИТЫВАНИЯ, содержащий два переключающих транзистора, сток первого из которых соединен с затвором второго переключающего транзистора, сток которого соедлнен с затвором первого переключающего транзистора, истоки переключающих транзисторов объединены и подключены к первой шине управления, два нагрузочных транзистора, стоки которых объединены, а истоки подключены к стокам переключающих транзисторов, балансный транзистор, исток которого соединен с истоком первого нагрузочного транзистора, сток— с истоком второго нагрузочного транзистора, а затвор — с затворами нагрузочных транзисторов и второй шиной управления, конденсаторы, транзисторы регенерации, затворы которых объединены и подключены к третьей шине управления, а истоки соединены с одними обкладками конденсаторов, другие обкладки которых подключены к четвертой шине управления, отличающийся тем, что, с целью повышения степени интеграции устройства, в него введены четыре разделяющих транзистора, причем истоки первого и второго разделяющих транзисторов подключены к стоку первого переключающего транзистора, а истоки третьего и четвертого разделяющих транзисторов подключены к стоку второго переключающего транзистора, стоки первого и третьего разделяющих транзисторов подключены соответственно к сто- @ кам первого и второго транзисторов регенерации, затворы первого и третьего, второго и четвертого разделяющих транзисторов подключены соответственно к пятой и шестой шинам управления, истоки разделяющих транзисторов являются информационными входами усилителя считывания.

1084889

Изобретение относится к вычислительной технике, а именно к усилителю считывания, который может быть использован в интегральном полупроводниковом МДП динамическом запоминающем устройстве на однотранзисторных элементах памяти.

Известен усилитель считывания, выполненный на основе триггера динамического типа, плечи которого образуют информационные входы усилителя считывания, к каждому из которых подключены транзисторы предзаряда и через соответствующие разрядные шины однотранзисторные элементы памяти и один опорный элемент (1).

При работе такого усилителя íà его информационные входы поступает дифференциальный сигнал. Поступивший из элемента памяти сигнал усиливается усилителем считывания и снова записывается в этот же элемент памяти. При усилении, из-за емкостной связи между входами усилителя и частичного разряда плеча триггера с большим потенциалом, происходит частичная потеря уровня логической единицы, которая достигает 20О/р от его максимального значения.

В результате после усиления в элемент памяти записывается уменьшенный уровень логической единицы, который составляет всего

80О/0 его номинального значения, равного напряжению питания. Потеря уровня логической единицы приводит к снижению надежности работы усилителя считывания и создает возможность считывания ложной информации при последующих обращениях к этому элементу памяти, что является недостатком этого усилителя считывания.

Наиболее близким по технической сущности к изобретению является усилитель считывания, содержащий два переключающих транзистора, сток первого из которых соединен с затвором второго, сток которого соединен с затвором первого переключающего транзистора, истоки переключающих транзисторов объединены, два нагрузочных транзистора, стоки которых объединены, а истоки подключены к стокам переключающих транзисторов, балансный транзистор, исток которого соединен с истоком первого нагрузочного транзистора, сток — с истоком второго нагрузочного транзистора, а затвор— с затворами нагрузочных транзисторов и пер. вой шиной управления, конденсаторы и тран зисторы регенерации, затворы которых подключены ко второй шине управления, истоки транзисторов регенерации подключены к стокам переключающих транзисторов, а стоки— к одним обкладкам конденсаторов, другие обкладки которых подключены к третьей шине управления (2).

Известны усилитель считывания позволяет благодаря наличию блоков восстановления уровня логической единицы восстановить уровень логической единицы после усиления информации до его номинальной ве55 ки которых подключены к четвертои шине управления, введены четыре разделяющих транзистора, причем истоки первого и второго разделяющих транзисторов подключены личины, равной напряжению питания, что существенно увеличивает надежность работы.

При работе усилителя в начальный момент усиления на его информационных входах установлен дифференциальный сигнал

AU, поступивший из элемента памяти: где Cxp — емкость хранения элемента памяти;

10 C — емкость разрядной шины;

Сву — емкость информационных входов усилителя;

E< — напряжение питания.

Элемент памяти должен облада- : величиной емкости С которая при да.-,.ой ве15 личине емкости разряднои шины С оЬеспечит (минимальную) необходимую величину информационного сигнала, достаточную для правильного считывания и усиления.

При этом, как следует из выражения (1), уменьшение величины емкости разрядной шины С, подключенной к информационным входам усилителя считывания в момент опроса элемента памяти, позволит для получения необходимой величины дифференциального сигнала ь 3 использовать меньшую величину емкости хранения элемента памяти

С р и тем самым уменьшить площадь элемента хранения. Поскольку элементы хранения занимают более. 90О/о площади усилителя считывания, это дает возможность уменьшения его площади.

Недостатком известного усилителя считывания является большая площадь, требуемаяя для получения необходимой вел и чи ны дифференциального сигнала.

Цель изобретения — повышение степени

35 интеграции устройства

Поставленная цель достигается тем, что в усилитель считывания, содержащий два переключаюгцих транзистора, сток первого из которых соединен с затвором второго переключающего транзистора, сток которого соединен с затвором первого переключающего транзистора, истоки переключающих транзисторов объединены и подключены к первой шине управления, два нагрузочных транзистора, стоки которых объединены, а

45 истоки подключены к стокам переключаюIllHx транзисторов, балансный транзистор, исток которого соединен с истоком первого нагрузочного транзистора, сток — с истоком второго нагрузочного транзистора, а затвор — с затворами нагрузочных транзисторов и второй шиной управления, конденсаторы, транзисторы регенерации, затворы кото.рых объединены и подключены к третьей шине управления, а истоки соединены с одними обкладками конденсаторов, другие обклад1084889 к стоку первого переключающего транзистора, а истоки третьего и четвертого разделяющих транзисторов подключены к стоку второго переключающего транзистора, стоки первого и третьего разделяющих транзисторов подключены соответственно к стокам первого и второго транзисторов регенерации, затворы первого и третьего, второго и четвертого разделяющих транзисторов подключены соответственно к пятой и шестой шинам управления, истоки разделяющих транзисTQpoB являются информационными входами усилителя считывания.

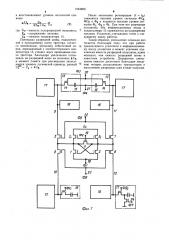

На фиг. 1 дана схема усилителя считывания; на фиг. 2 — временные диаграммы

10 работы устройства.

Устройство содержит первый 1 и второй 2 переключающие транзисторы, два нагрузочных транзистора 3» и 3>, балансный транзистор 4, первый 5, второй 6, третий 7 и четвертый 8 разделяющие транзисторы, первую 9, вторую 10, третью 11 и четвертую 12 разрядные полушины, два блока 13 восстановления уровня логической единицы, каждый из которых содержит транзистор 14 регенерации и конденсатор 15, однотранзисторные элементы 16 памяти, соединенные с разрядными полушинами и четыре опорных 25 элемента 17, подключенные к каждой разрядной полушине, шины 18 — 24 управления.

Стоки разделяющих транзисторов соединены с разрядными полушинами, а истоки — с информационными входами усилителя считывания. Стоки транзисторов регенерации соединены соответственно с первой 9 и третьей 11 разрядными полушинами.

Однотранзисторные элементы 16 памяти

-имеют входы включения ФС» — ФС», опорные элементы 17 имеют входы включения ФЭ,—

ФВ и вход установки опорного напряжения Ф .

В исходном состоянии (t c t ) на шинах 18 и 24 установлен высокий уровень сигналов Ф, и Ф„на шинах 19 — 23 установлен высокий уровень напряжения U 4 сигналов Ф, Ф, Ф и Ф, превышающий уровень найряжения питания как минимум на величину порогового напряжения транзисторов (Us> Е, + И.), на шине 21 установлен низкий уровень сигнала aid, на вхо- 45 дах включения однотранзисторных элементов памяти и опорных элементов установлены низкие уровни сигналов ФС; и 4>D>. При этом все четыре разрядные полушины и оба конденсатора 15 блоков восстановления уровня логической единицы заряжены до напря- 50 жения питания. В опорных элементах сигналом Ф» установлен опорный уровень напряжения. В элементе памяти хранится записанная туда ранее информация. В начале рабочего интервала (t = t.) снимаются высокие уровни сигналов Ф, Ф и Ф и одного из сигналов Ф или Ф . Допустим снимается высокий уровень сигнала Ф . Тран4 зисторы 14 регенерации и разделяющие транзисторы 6 и 8 переходят в закрытое состояние и отключают от информационных входов усилителя емкости разрядных полушин

10 и 12 и конденсаторы 15. К информационным входам остаются подключенными только разрядные полушины 9 и 11.

После этого в момент времени t = t производится обращение к одному из элементов памяти, подключенному к разрядной полушине 9 или 11, допустим к полушине 9, для чего подается высокий уровень сигнала ФС». Одновременно с этим производится обращение к опорному элементу, подключенному к противоположной разрядной полушине, в данном случае к полушине 11 (подается высокий уровень сигнала ФВ„.). В результате на информационных входах устанавливается дифференциальный сигнал

4U, соответствующий информации, хранящейся в выбранном элементе памяти:

hU = U< — U, если хранилась единица;

AU = — (Б» — Uz), если хранился нуль, где U» и U< — потенциалы на первом и втором информационных входах, соответственно. Для определенности будем считать, что в элементе памяти хранилась единица, т.е.

U»>11 . Так как разделяющие транзисторы 6 и 8 находятся в закрытом состоянии и отключают от информационных входов разрядные полушины 10 и 12, в предлагаемом усилителе дифференциальный сигнал ЬU такой же величины, как и в известном усилителе, получается при меньшей площади элемента памяти. Это приводит к уменьшению площади усилителя считывания.

После установления на информационных входах дифференциального сигнала

aU(t = t ) подается низкий уровень сигнал Ф» включения усиления. При этом второе плечо триггера (с меньшим установившимся уровнем потенциала Uz) переходит в проводящее состояние и потенциал на втором информационном входе уменьшается до нуля, а на первом плече (с большим установившимся уровнем потенциала U, ) происходит лишь частичная потеря уровня напряжения из-за емкостной связи и небольшого приоткрывания этого плеча.

В момент времени t = t подаются высокие уровни сигналов Ф, и Ф, при этом транзисторы 14 регенерации и разделяющие транзисторы 6 и 8 переходят в проводящее состояние. Разрядная полушина 12, конденсатор 15, соединенный с полушиной

11, разряжаются через проводящее плечо триггера. После этого в момент времени подается высокий уровень сигнала Ф . В результате заряд с конденсаторов 15 передается на соответствующие разрядные полушины 9 и 11. При этом потенциал разрядной шины, подключенной к закрытому плечу триггера, увеличивается на величину b Uq

1084889

5 и восстанавливает уровень логической единицы (2} где Cw — емкость полуразрядной полушины;

Kä -напряжение питания;

Ся -емкость конденсатора 15.

Потенциал разрядной шины, подключенной к проводящему плечу триггера, остается неизменным, поскольку избыточный заряд, передаваемый с соответствующего конденсатора 15, стекает через проводящее плечо триггера. Благодаря увеличению потенциала на разрядной шине на величину hU в элемент памяти при регенерации записывается уровень логической единицы, равный

1- л = Ц + а - и а

После окончания регенерации (t = tq) снимаются высокие уровни сигналов ФС, Ф0 и Ф и подаются высокие уровни сигналов Ф, Ф и Фт. При этом все разрядные полушины, оба информационных входа и конденсаторы 15 заряжаются до напряжения питания. Усилитель считывания готов к следующему циклу работы.

Таким образом, уменьшение площади достигается благодаря тому, что при работе

10 предлагаемого усилителя к информационному входу усилителя в момент усиления подключена емкость разрядной полушины, вдвое меньшая, чем емкость разрядной шины в известном устройстве. Двукратное уменьшение емкости достигнуто благодаря введению четырех разделяющих транзисторов и выполнению разрядных шин в виде полушин.!

084889

Ф2

1

1 о у 4 б 4 4 фиг. Г

Составитель О. Кулаков

Редактор С. Саенко Техред И. Верес Корректор В. Бутяга

Заказ 2023/48 Тираж 575 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытии

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4