Постоянное запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее блок постоянной памяти, первый дешифратор адреса, блок свертки по модулю два, элемент И-НЕ, вход и выход первого дешифратора адреса соединены соответственно с первым и вторым входами блока постоянной памяти, выход которого подключен к входу блока свертки по модулю два, выход которого соединен с первым входом элемента И-НЕ, выход которого является первым контрольным выходом устройства , первый вход блока постоянной па-. мяти является адресным входом устройства , отличающееся тем, что, с целью повышения надежности за счет осуществления контроля его адресной части, в него введены второй дешифратор адреса, блок элементов И, элемент ИЛИ, счетчик, третий дешифратор адреса, причем вход второго дешифратора адреса соединен с первым входом блока постоянной памяти , а выход второго дешифратора адреса подключен к входу элемента ИЛИ, выход которого соединен с первым входом счетчика и вторыми входами элемента И-НЕ и блок элементов И, второй вход счетчика подключен к выходу блока свертки по модулю два, вход которого соединен с первым входом блока (Л элементов И, выход которого является информационным выходом устройства , выход счетчика подключен к первому входу третьего дешифратора адреса , второй вход которого является мА управляющим входом устройства, выО ход третьего дешифратора адреса явэо 4 х ляется вторым контрольным выходом устройства.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (29) (124

3(521 С 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ЧЗ

°,1; 22(< 1 Ч

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3490950/18-24 (22) 10.09.82 (46) 07.04.84. Бюл. N - 13 (72) В.К, Озеран и В.В. Слюсарь (53) 681.317(088.8) (56) 1. Авторское свидетельство СССР

Ф 364967, кл. G 11 С 29/00, 1973, 2. Авторское свидетельство СССР

22 - 723676, кл. G 11 С 29/00, 1980 (прототип) ° (54) (57) ПОСТОЯННОЕ ЗАПОМИНА2(@ЕЕ

УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее блок постоянной памяти, первый дешифратор адреса, блок свертки по модулю два, элемент И-НЕ, вход и выход первого дешифратора адреса соединены соответственно с первым и вторым входами блока постоянной памяти, выход которого подключен к входу блока свертки по модулю два, выход которого соединен с первым входом элемента И-НЕ, выход которого является первым контрольным выходом устройства, первый вход блока постоянной па-. мяти является адресным входом уст/ ройства, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности эа счет осуществления контроля его адресной части, в него .введены второй дешифратор адреса, блок элементов И, элемент ИЛИ, счетчик, третий дешифратор адреса, причем вход второго дешифратора адреса соединен с первым входом блока постоянной памяти, а выход второго дешифратора адреса подключен к входу элемента ИЛИ выход которого соединен с первым входом счетчика и вторыми входами элемента И-НЕ и блок- элементов И, второй вход счетчика подключен к выходу блока свертки по модулю два, вход которого соединен с первым входом блока элементов И, выход которого является информационным выходом устройства, выход счетчика подключен к первому входу третьего дешифратора адреса, второй вход которого является управляющим входом устройства, выход третьего дешифратора адреса является вторым контрольным выходом устройства.

4 1084902

Изобретение относится к автомати- в ке и вычислительной технике, в част- с кости к запоминающим устройствам, в и может быть использовано в устройствах вычислительной техники. в

Известна постоянное запоминающее в устройство (ПЗУ), содержащее блок д памяти, регистр на триггерах со л счетными входами 1).

Недостатком устройства является 1g н невозможность обнаружения отказов типа постоянная единица, чта сни- . т жает надежность устройства.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля постоянной памяти, содержащее блок постоянной памяти, блок свертки по модулю два, счетный триггер, элементы И-НЕ, триггер, причем выход блока постоянной памяти соединен с входом блока свертки по модулю два, выход которого соединен с первыми входами счетного триггера и первого элемента И-НЕ, выход которого соединен с первым входом триггера, второй вход которога соединен с выходом первого элемента И-НЕ, вторые входы элементов И-НЕ являются управляющими входами устройства, выход триггера является вы30 ходом устройства Г2 ).

Недостатком известного устройства является то, что в процессе работы не осуществляется контроль схемы, формирующей адрес ячейки постоянной памяти (например, счетчика адреса) и не полностью охвачены контролем функциональные узлы устройства (например, отказ блока свертки по модулю два может привести к необнаруженному отказу ячейки постоянной памя1 ти) .

Кроме того, в устройстве ке осуществляется контроль непосредственно постоянной памяти по адресным шинам, ".å. отказ пастоянкой памяти па одному из адресных входов данное устройство не обнаружит. Эти недостатки приводят к снижению надежности устрайс.ва, Целью, лзабре:гения является повыше-- О ние надежности за счет осуществления контроля адресной части устройства.

Поставленная цель достигается тем, что в..постоянное запоминающее устройство с самоконтролем, содержа- » щее блок постоянной памяти, первый дешифратор адреса, блок свертки па модулю два, элемент И-HE вход и

ыход первого дешифратора адреса оединены соответственно с первым и торым входами блока постоянной памяти, выход которого подключен к ходу блока свертки по модулю два, ыход которого соединен с первым вхоом элемента И-НЕ, выход которого явяется первым контрольным выходом устройства, первый вход блока постаяной памяти является адресным входом устройства, введены второй дешифраор адреса, блок элементов И, элемент ИЛИ, счетчик, третий. дешифратор адреса, причем вход второго дешифтора адреса соединен с первым входом блока постоянной памяти, а вы ход второго дешифратора адреса подключен к входу элемента ИЛИ, выход которого соединен с первым входом счетчика и вторыми входами элемента И-НЕ и блока элементов И, второй вход счетчика подключен к выходу блока свертки по модулю два, вход которого соединен с первым входом блока элементов И, выход которого является информационным выходом устройства, выход счетчика подключен к первому входу третьего дешифратора адреса, второй вход которого является управляющим входом устройства, выход третьего дешифратора адреса является вторым контрольным выходом устройства.

Второй дешифратор адреса формирует на своих выходах сигналы при наличии на адресных шинах определенных кодовых комбинаций (например, двоичные кодовые комбинации с О-м, 255-м, 256-м, 511-м, 512-м, 767-м, 768-м и

1028-м адресами) и позволяет выйти на контрольные ячейки ПЗУ, соответствующие вышеуказанным адресам, что дает вазможность определить исправность ПЗУ по адресным шинами, а так" же неисправность схемы, формирующей адрес ячейки ПЗУ.

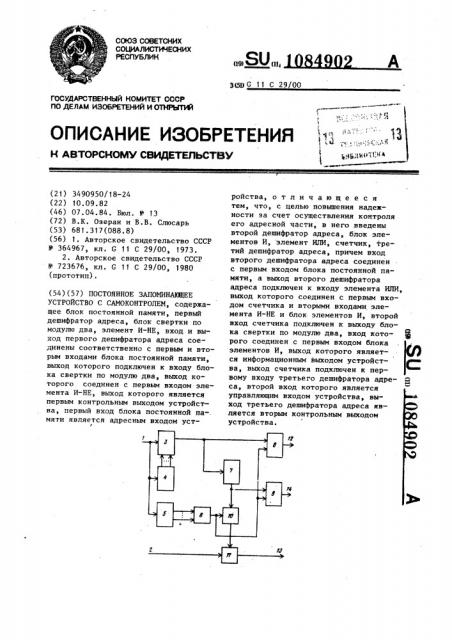

На чертеже представлена структур-ная схема постоянного запоминающего устройства с самоконтролем.

Устройство содержит адресную шину 1, шину 2 управления, блок 3 постоянной ":мяти, первый дешифратор 4 адреса, второй дешифратор ". а;. реса,, элемент ИЛИ 6, блок 7 сверткг па мо-дулю два, блок элементов И 8, элемент

И-НЕ 9, счетчик 10, третий дешифратор адреса 11, информационный вьгход

12, второй контрольный выход 13, первый контрольный выход 14„

3 1084

Работу ПЗУ с самоконтролем рассмотрим на примере полупроводникового ПЗУ емкостью 1 К, построенного на интегральных микросхемах емкостью

256 и-разрядных слов каждая, т.е. в состав ПЗУ будут входить четыре физических страницы памяти емкостью

256 и-разрядных слов каждая.

Заносят в ячейки блока 3 постоянной памяти с О-м, 255-м, 256-м, !

О

511-м, 512-м, 767-м, 768-м и 1023-м адресами искаженную информацию (при контроле считываемой информации на нечетное количество единиц заносят четное количество единиц и наоборот). Выбор указанных ячеек продиктован тем, что ПЗУ содержит всего четыре физические страницы памяти, т.е. в каждой странице памяти содержатся по две искаженные ячейки — в начальном адресе и в конечном.

Так как считывание команды начинается с ячейки с 0-м адресом, то на адресной шине 1 присутствуют все

|нули (т.е. комбинация вида

00.0000.0000), и на одном из выходов первого дешифратора 4 адреса формируется сигнал обращения к нулевой странице блока 3 постоянной памяти.

Поскольку в нулевую ячейку блока 3

30 постоянной памяти занесена искаженная информация, то блок 7 свертки по модулю два сфбрмирует на своем выходе сигнал ошибки. Примем условно уровень данного сигнала равным нулю.

Второй дешифратор 5 адреса, анализируя состояние адресной шины 1, сформирует на одном из своих выходов сигнал нулевого уровня, поступающий через элемент ИЛИ 6 ка первый вход счетчика 10, и блокирует прохождение информации, считанной иэ блока 3 постоянной памяти через блок элементов

И 8 и формирование сигнала "Ошибка" элементом И-HE 9. Сигнал "Ошибка™ в 45 считанной информации, сформированный блоком 7 свертки по модулю два, поступает на второй вход счетчика 10. Наличие сигналов нулевого уровня на первом и втором входах счетчика 10 приводит к разрешению занесения сигнала

"Ошибка" в счетчик 10, т.е. к его модификации.

Таким образом, при чтении информации с нулевой ячейки блока 3 постоянной памяти сигнал "Ошибка на первом контрольном выходе 14 будет отсутствовать, и искаженная информа902 4 ция не выстаивается на выходную информационную шину 12.

При чтении информации по следую" щему адресу на выходе второго дешифратора 5 адреса будет отсутствовать

М сигнал нулевого уровня, а на первых входах блока элементов И 8 и элемента И-НЕ 9 будут присутствовать сигналы единичного уровня; Данные сигналы разрешат прохождение считанной из блока 3 постоянной памяти информации через блок элементов И 8 на информационный выход 12, а также прохождение сигнала "Ошибка" (при наличии данного сигнала на выходе блока 7 свертки по модулю два) на первый контрольный выход 14.

Модификация счетчика 10 осуществляется также при обращении к ячейкам с 255-м, 256-м, 511-м, 512-м, ?67-м, 768-м и 1023-м адресами. После этого дешифратор 11 анализирует состояние счетчика 10 и при наличии на шине 2 управления разрешающего сигнала (сигнал анализа ошибки ПЗУ) формирует на своем выходе сигнал

"Не ошибка", поступающий на второй контрольный выход 13.

Сигнал же "Ошибка" на втором контрольном выходе 13 формируется в следующих случаях: неправильно работает блок 7 свертки по модулю два, т.е. íà его выхо,де постоянно формируется сигнал "He ошибка" (в примере — сигнал единичного уровня). Действительно, при отсутствии сигнала "Ошибка" нулевого уровня на выходе блока 7 свертки по модулю два, состояние счетчика !О не будет изменяться, а это значит, что при наличии сигнала анализа ошибки на шине 2 управления дешифратор 11 сформирует сигнал "Ошибка"; неправильно работает либо первый 4, либо второй 5 дешифраторы адреса.

Действительно, при неправильной работе первого 4 дешифратора адреса будет отсутствовать обращение к какойлибо одной или нескольким страницам блока 3 постоянной памяти, т.е. на выходе блока 7 свертки по модулю два будут отсутствовать один или несколько (по числу искаженных ячеек) сигналов "Ошибка" при обращении к искаженным ячейкам блока 3 постоянной памяти, а значит на выходе дешифратора 11 также сформируется сигнал

"Ошибка" (в примере состояние двоичного счетчика 10 не равно восьми).

3 10В4Я02

При неправильной работе второго 5 дешифратора адреса либо частично, либо полностью не будет осуществляться дешифрация искаженных ячеек, т.е. состояние счетчика 10 не будет равно восьми; неисправна схема, формирующая код адреса; не работоспособны злементы ИЛИ 6, счетчик 10; произошел либо обрыв, либо замыкание на ноль какого-либо адресного входа в микросхеме блока 3 постоянной памяти.

Таким образом, предлагаемое ПЗУ с самоконтролем позволяет в процессе работы проводить контроль информации, записанной в блок постоянной памяти, контроль работоспособности функциональных узлов устройства, схем контроля,а также работоспособности внешних

16 схем, формирующих код адреса ячейки бло" ка постоянной памяти,что значительно повышает надежность ПЗУ с самоконтролем.

Заказ 2024/4Э Тирау Подписное

ВИК4ПИ Государственного комитета СССР го делам изобретений и открытий

113035, Иосква, 5-:5, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород,„, ул. Проектная, 4

Составитель О. Кулаков

:- pp&KTop А. KGHGGp Техред Р, >, е -елева Корректор А. Р, ьик