Формирователь повторяющихся частотно-модулированных сигналов

Иллюстрации

Показать всеРеферат

ФОРШРОВАТЕЛЬ ПОВТОРЯЩИХСЯ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ, содержащий последовательно соединенные первый сумматор, цифроаналоговый преобразователь, фильтр, блок автоподстройки частоты, аналого-цифровой преобразователь, второй сумматор и блок памяти, адресные входы которого соединены с соответствующими выходами блока адресации, а также блок управления, первый и второй выходы которого соединены с соответствующими входами синхронизации блока автоподстройки частоты и соответственно с установочным входом и входом тактирующих импульсов блока адресации , о тличающийся тем, что, с целью уменьшения отклонений от заданного закона модуляции, в него введены последовательно соединенные блок вычисления разностей, входы которого соединены с соответствующими выходами блока памяти, и цифровой интерполятор, выход котороС 9 го соединен с первым входом первого сумматора, при этом установочный и (Л тактирующий входы цифрового интерполятора соединены соответственно с вторым и третьим выходами блока управления, а вторые входы первого и второго сумматоров соединены с первым выходом блока памяти. о 00 4 СО 4;;

СОЮЗ СОВЕТСНИК

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„Я0„„1084940

3(50 Н 03 В 23 00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

А

ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3382995/18-09 (22) 06.01.82 (46) 07.04,84. Бюл. 9 13 (72) В.H. Кочемасов, А.Д. Ревун и А.Н. Фадеев (71) Всесоюзный заочный электротехнический институт связи (53) 621.376.3(088.8) (56) 1. Патент США - 3621450, кл. 331-10, опублик. 1972.

2 ° Авторское свидетельство СССР

Ф 790102, кл. Н 03 В 23/00, 1979 (прототип). (54)(57) ФОРМИРОВАТГЛЬ ПОВТОРЯЮЩИХСЯ

ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ, содержащий последовательно соединенные первый сумматор, цифроаналоговый преобразователь, фильтр, блок автоподстройки частоты, аналого-цифровой преобразователь, второй сумматор и блок памяти, адресные входы которого соединены с соответствующими выходами блока адресации, а также блок управления, первый и второй выходы которого соединены с соответствующими входами синхронизации блока автоподстройки частоты и соответственно с установочным входом и входом тактирующих импульсов блока адресации, отличающийся тем, что, с целью уменьшения отклонений от заданного закона модуляции, в него введены последовательно соединенные блок вычисления разностей, входы которого соединены с соответствующими выходами блока памяти, и цифровой интерполятор, выход которого соединен с первым входом первого сумматора, при этом установочный и тактирующий входы цифрового интерполятора соединены соответственно с вторым и третьим выходами блока управления, а вторые входы первого и второго сумматоров соединены с первым выходом блока памяти.

1084940

30

Изобретение относится к радиотехнике и может использоваться для формирования повторяющихся частотномодулированных сигналов в радиолокации, технике связи, измерительной технике в системах автоматической подстройки.

Известен формирователь повторяющихся частотно-модулированных сигналов с автоматической компенсацией регулярных искажений, определяемых нелинейностью характеристик упгавляемого генератора и модулятора P1 ).

Однако этот формирователь повторяющихся частотно-модулированных сигналов не обеспечивает достаточной точности передачи заданного закона модуляции и надежности.

Наиболее близким к предлагаемому является формирователь повторяющихся частотно-модулированных сигналов, содержащий последовательно соединенные первый сумматор, цифроаналоговый преобразователь, фильтр, блок автоподстройки частоты, аналого-цифровой преобразователь, второй сумматор и блок памяти, адресные входы которого соединены с соответствующими вьгходами блока адресации„ блок управления, первый и второй выходы которого соединены с соответствующими входами синхронизации блока автоподстройки частоты и соответственно с установочным входом и входом тактирующих импульсов блока адресации, а также регистр, блоки коррекции и сглаживающий фильтр.

В известном формирователе повторяющихся частотно-модулированных сигналов на выходе цифроаналогового преобразователя формируется ступенчатое напряжение, компенсирующее регулярные, т.е. повторяющиеся от периода к периоду, искажения. Точность аппроксимации регулярных искажений,при этом зависит как от числа разрядов цифроаналогового преобразователя, так и от длительности ступенек на его выходе f2g.

Недостатком известного формирователя повторяющихся частотно-модулированных сигналов являются относит тельно большие отклонения выходного сигнала от заданного закона модуляции, т.е. относительно невысокая точность формирования сигналов из-за ограничений на минимальную длительность ступенек напряжения на выходе циф1о-аналогового преобразователя, возникающих из-за значительного времени, затрачиваемого на считывание и запись информации в блок памяти. В результате точность аппроксимации реальной регулярной помехи напряжением, формируемым на вьгходе цифроаналогового преобразователя, оказывается невысокой, а ошибки аппроксимации, поступающие на вход управления блока автопоцстройки часToTbI — большими. Использование на выходе цифроаналогового преобразователя фильтра с большой постоянной времени с целью сглаживания ступенчатого напряжения, а значит и уменьшения ошибок аппроксимации приводит к нарушению устойчивой работы устройства. Этот недостаток становится еще более существенным, если измерение ошибок в блоке автоподстройки частоты осуществляется дискретно и в период,дискретизации значительно превышает время, требуемое для считывания и записи информации в блок памяти.

Цель изобретения — уменьшение отклонений от заданного закона модуляции.

Эта цель достигается тем, что в формирователь повторяющихся частотно-модулированных сигналов, содержащий последовательно соединенные первый сумматор, цифроаналоговый преобразователь, фильтр, блок автоподстройки частоты, аналого-цифровой преобразователь, второй сумматор и блок памяти, адресные входы которого соединены с соответствующими выходами блока адресации, а также блок управления,, первый и второй выходы которого соединены с соответствующими входами синхронизации блока автоподстройки частоты и соответственно с установочным входом и входом тактирующих импульсов блока адресации, введены последовательно соединенные блок вычисления разностей, входы которого соединены с соответствующими выходами блока памяти, и цифровой интерполятор, выход ксторого соединен с первым входом нервого сумматора, при этом установочный и тактирующий =ходы цифрового интерполятора соединены соответственно с вторым и третьим выходами блока управления, а вторые входы первого и второго сумматоров соединены с первым выходом блока памяти.

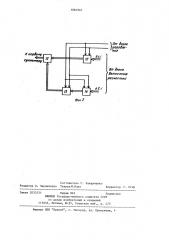

На фиг.1 представлена структурная электрическая схема предлагаемого формирователя; на фиг.2 — пример выполнения цифрового интерполятора, входящего в него.

Формирователь повторяющихся частотно-модулированных сигналов содержит первый сумматор 1, цифроаналоговый преобразователь (ЦАП) 2, фильтр 3, блок 4 автоподстройкй частоты„ аналого-цифровой преобразователь (АЦП) 5, второй сумматор 6, блок 7 памяти, блок 8 управления, блок 9 адресации, блок 10 вычисления разностей, цифровой интерполятор 11.

Формирователь работает следующим образом.

Сигнал ошибки иэ блока 4 автоподстройки частоты после преобразования к цифровому виду используется для формирования компенсирующего напряжения, подаваемого на управляющий вход блока 4 автоподстройки. частоты. Воэможность применения такого компенсирующего напряжения основывается на повторяемости ошибок в блоке 4 автоподстройки частоты от одного периода к другому.

При рассмотрении процесса формирования компенсирующего напряжения е (t) будем считать, что на вход к

АЦП 5 поступает дискретный сигнал ошибки е(т,) с периодом дискретизации

Т . Через такое же время осуществляются считывание и запись ин,!!ормации

4 ( в блоке 7 памяти. Порядок считывани и записи определяется командами, поступающими с блока 9 адресации, тактируемого импульсами с второго выхода блока 8 управления, следующими с периодом Т . По сигналу с второго выхода блока 8 управления в блоке 9 адресации осуществляется установка начальных условий. Для работы цифрового интерполятора 11 наряду с импульсами, поступающими с второго выхода блока 8 управления, используются тактовые импульсы повышенной частоты следования, период ,которьгх i = Т /2, где . — целое

Д число. Эти импульсы подаются на цифровой интерполятор 11 с третьего выхода блока 8 управления.

Код e>,(q,), используемый для компенсации регулярной помехи, формируется на выходе первого сумматора

84940 4

1 в соответствии с интерполяционной формулой (- J

Я,(Я;1).-. (+-!!+1) л.„„., () !

1,=1,...,(Т, / ) — целые числа,формируемые по импульсам, поступающим с третьего выхода блока

8 управления. ,= Р . — Е . — конечные разнос1,1 П,1+1 tl,1 ти первого пог рядка,, = д — д . — конечные разносZi 1 !+1 1 j ти второго порядка;

20 д „: = д л 7111-д „1 1 конечные разнос ти И-го порядка.

Коды Ь 1 y dg 1ю d$1j ° °, эйп форми г (! руются в блоке 10 вычисления разнос25 тей по значениям е„ .,е„,,е ...,е ., извлекаемым из блока 7 э П,1+П э памяти.

Цифровой интерполятор 11 (фиг.2) вьп!олняется в виде вычислительного устройства, содержащего сумматоры, умножители и делители кодов. В то же время при линейной или квадратичной интерполяции он реализуется существенно проще.

Цифровой интерполятор содержит сумматор 12, первый, второй и третий накопители 13 — 15. Код сф„; формиI руется на выходе первого накопителя

13, а на выходе третьего накопителя

15 формируется код 0,5 (,-1) и, .

Тактирование накопителей 13 — 15 осуществляется импульсами, следующими с периодом !. повторения, а импульсы с второго выхода блока 8 управления обеспечивают установку их начальных условий.

Предлагаемый формирователь позволяет существенно повысить точность аппроксимации регулярной помехи и применить для сглаживания фильтр с меньшей постоянной вРемени, что делает более устойчивой работу блока автоподстройки частоты и в конечном счете приводит к значительному уменьшению отклонений от заданного закона

SS модуляции.

- 1084940

Составитель Г. Захарченко

Редактор О. Черниченко ТехредИ.Надь

Корректор Г. Огар

Заказ 2033/51

Тираж 862 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауновская наб., д, 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Р л ей/

PwAtnt

0m Ъвча увра&г6 &юла Ь Юис жж РЮ,У Ж СЛ рр