Цифровой частотный модулятор

Иллюстрации

Показать всеРеферат

ЦЙФРОВ(Й ЧАСТОТНЫЙ МОДУЛЯТОР , содержаар1й эадаюощй кварцевый генератор, а также последовательно .соединенные первый блок постоянной памяти, цифроаналоговЕой преобразователь и фильтр нижних чартот, о тличающийся тем, что, с целью повышения точности передачи закона модуляции, в него введены последовательно соединенные второй блок постоянной памяти, двоичный сумматор и регистр, выходы всех разрядов которого соединены с вторым входом двоичного сумматора, а выходы п старших разрядов соединены также с адресным входом первого блока Постоянной памяти, при этом выход задающего кварцевого генератора подключен к входу записи регистра, один вход второго блока постоянной 5 памяти является входом информационных данщох, а другой вход является входом сигнала управления скоростью передачи информации. л f 00 4 4

СОЮЗ COBETGHHX

ЦН ВЮМ

РЕСПУБЛИН дц Н ОЭ С 3/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3362280/18-09 (22) 04. 12, 81 (46) 07.04.84. Бюл. Ф 13 (72) К.Ф. Астапкович, В.ф. Буянов и В.А. Жаренов (71) Ленинградский электротехнический институт связи им. проф.

И.А. Вонч-Бруевича (53) 621. 376. 32 (088. 8) (56) 1. Jungnickel Horst. Entwurt

eines Daten senders fur freqenzmodulierte signsle.-"Ràdio-FernsehenRlectronik", 1977, т. 26, Р 6.

2. Патент Японии I 52-4148, кл. Н 03 С 3/00, опублик. 1977 {прототип). (54)(57) ЦИФРОВОЙ ЧАСТОТНЫЙ МОДУЛЯТОР, содержащий эадаюадй кварцевый генератор, а также последовательно .соединенные первый блок постоянной

„.Я0„„1084944 A памяти, цифроаналоговый преобразователь и фильтр нижних частот, о тл и ч а ю шийся тем, что, с целью повьппения точности передачи закона модуляции, в него введены последовательно соединенные второй блок постоянной памяти, двоичный сумматор и регистр, выходы всех разрядов которого соединены с вторым входом двоичного сумматора, а выходы и старших разрядов соединены также с адресным входом первого блока постоянной памяти, при этом выход задающего кварцевого генератора подключен к входу записи регистра, один вход второго блока постоянной памяти является входом информационных данных, а другой вход является входом сигнала управления скоростью передачи информации. гт гт

Mз о -.: —,; —-гг

TeXHттКt= фОУ Мтгт (1, —., - гсигн ало :. г цатт(T(.г-„= г=.; ; » г

К=в та таКтат((тт (HMji« .(, -..:":=:- .: (t-,(-(1 Л

ОЕКЛ(Ютгаг(ТТ((Е; О т„.= тг(:,:.-;г.(.;а(-:, — .*,: —,; —,,;. Е"

T (1 фаэу (:ггл-:,:(ТО,"=,t -(б(:.» . „- -» ( рв3 д) Ил(= i

ПрЕОбраэ.".:":.„ -таЛ т-...:.,; .;::: . о Л(;. г ()гг(.г (тгО 1; »(г Г(.,гт., гт(.Г

:I;t!! t(((ГГ:Лгт(модуля-о(э 1 it (»; . ния вы:,*. лг (О о (ЧаСтОт Л-;1(;IП,НЛ.; : ".Т(ТЧ . ((ЧаСтОтЫ К 1(1(»((тай(;:(гбг):: т.-((.. Г(11(- (:: ной (- коро..

ГОИ ттртс(т гтг (. ив- р г к -((t.!;» ."::;;: =,:

ИГ ПОЯ1Ь„ . !11.; г-, (", дерет(и)- .

1 тор, (.О!" г: -",:(!;(J

ГЕ (-(срс-, »(1 (1 о Е (г г."„-; (, -;., - . -zМл тВа тгг" - . IT» 1 г ", т

) . г также,1(=-:: (а к (" л

Згз(у Г 1 (г . г

-"..r I =I rг, ! I т., ВОдс ТГ 1(Х tг,тl.T -l вь.дающн ; т:.: и-.:- и жающттт(гтЮ) -гт)(-.- (-1((г-.;-:-»;-t!!; -,,-.г г((—:,.-... -.,-.;г(.-На НЕ(тг,»т((,Лг.тт(гт .; -,гг. (Тт(Н,"; то "-1;ТЭ-т; =:, . -, 1,1- ° т(ОСтг» Лг»ро Л . -;,., "г 1 ....»т,;;.;т;, (т

1 I Р Л;:: Т :;,:: Тт (-, .:" I t = .; c ) 1 (. ((- ":.;ОР, т ОЦ г).,;:--.ЛП;:,г;: т; г -l!-!I!l .;,: =; =:-l";(:11(!(.,".(Г(ЭЧЕрд T ..Тт ° г .... ";:: -- ° . ».. (, Т) г:гг», (ттЛятОр С т,гг;гг-; г.тг.(г

С КВартгв(1()1г (.; )-;: .:, г 1 "т,. -. г .т —.

ЦЕЛИ (и ТТ Т-,: Та С -" г-, ; -, (. (1 т» т,-. ((г -т:,; о —,.;; —.,=: -- — С -Т . ! г

СИГНаЛОм 1агттттт гт г г " : г — г т.; г \тт г»;г ляющкм корость гг =1(1(, т*: ((-(г)1(11)((,,ттт, .", а такж(» ТТ (, О;.=, Тт,. *(Ijt. Г tl ..t : т . l: (:-ОЕЛГ((-.H(Tb(Å ПЕрВЫй бЛОК ПОСтОяННОй лагг(в(((, цифроаналоговый преобразоват;(.- и фильтр нижних частот, введе;: последовательно соединенные вто-;ой блок г(остоянной памяти, двоич:.1(г(й сумматор и регистр, выходы всех †.азрядов которого соединены с вто1oIt! входом двоичного сумматора, а ((...)(оды ((старших разрядов соединены также с адресным входом первого блока постоянной памяти, при этом

=-,-(хогг(задающего кварцевого генератора подключен к входу записи регистра, один вход второго блока постоянной памяти является входом информационных .«,= нных, а другой вход является входом

-.(гнала управления скоростью переда" н(-:фор(гацин.

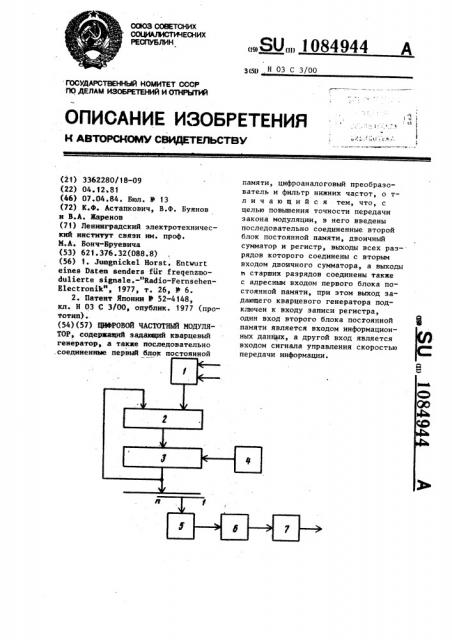

Н г чертеже изображена блок-схема иттфрового частотного модулятора.

Цифровой частотный модулятор со1: ;;(jт второй блок постоянной памя.-и, двоичный сумматор 2, регистр зада(ощтгй кварцевый генератор 4, первый блок 5 постоянной памяти, .:,нфроаналоговый преобразователь

,.T;n, 6, фильтр 7 нижних частот (ФИЧ).

У..тройство работает следующим

:.(((формационные данные совместно сигиалогг угтравления скоростью пе

:. -еда(и данных поступают на входы второго блока 1 постоянной памяти, в котором храп-..òся численные значения ..абега фазы характеристических частот

=1ë период частоты задающего кварцевого генератора 4. Численное значение (†:«б.=- ;-;, фазы поступает на первый вход

- (;лтгт(((ого =умматора 2, выход которого

r;!(-ци(e((с входом регистра 3, где

-(грап(тся текущее значение фазы характ".îèстического колебания. Выходы ..::ех разрядов регистра 3 подключены †;:.îðoìó зходу двоичного сумматора 2. вход записи регистра 3 подается последовательность импульсов с выхода

; †.ацающего кварцевого генератора 4.

Кат((дьтй период частоты задающего квар-..:евого генератора 4 в регистр 3 записывается вновь вычисленное значение ф«зы характеристического колебания.

Т;:к,гг(образом, номинал генерируемой .:-(стоты определяется численным значет(ием ;.оответствующего набега фазы, « точность ее представления обеспечи; вЂ.-:.::ется выбором разрядности второго

:-j((jêë 1 постоянной памяти двоичного ..-;мг.;атора 2 и регистра 3. Из регистра

944

1084

Составитель Г. Захарченко

Редактор С. Саенко Техред Л.Коцюбияк Корректор Г. Огар, Тираж 862 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 2033/51

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

3 сигналы с выхода и старших разрядов подаются на адресный выход первого блока 5 постоянной памяти, в котором записаны выборки из одного периода сииусоидального колебания. Эти выборки последовательно поступают на вход цифроаналогового преобразователя 6, с выхода которого сформированный аналоговый сигнал через фильтр 7 нижних частот подается на выход цифрового 10 частотного модулятора.

При представлении текущего значения фазы характеристического колебания

20-разрядным двоичным числом отклоне- 15 ние характеристической частоты от номинального значения составляет О, 10,3 Гц, что примерно на порядок лучше, чем у известного устройства.

Скачок фазы при переходе от одной ха- 20 рактеристической частоты к другой в предложенном цифровом частном модуляторе определяется числом старших разрядов регистра 3, используемых для адресации к первому блоку 5 постоянной25 памяти, а также числом разрядов, ие4 обходимых для представления значения набега фазы характеристического коле- бания. При частоте задающего генератора 1 МГц и представлении текущего значения фазы характеристического колебания 20 двоичными разрядами для представления набега фазы любой из характеристических частот достаточно I

10-11 двоичных разрядов. Таким образом, для адресации к первому блоку 5 постоянной памяти можно использовать"

9-10 разрядов, что эквивалентно скачку фазы 0,18-0,35о, в то время как известное устройство обеспечивает минимальный скачок фазы 11,25.

Таким образом, в предложенном цифровом частном модуляторе значительно повышается точность передачи закона модуляции. Кроме того, при переходе от одной скорости передачи информации к другой не требуется дополнительных затрат, поскольку смена характеристических частот в данном случае приводит лишь к записи во второй блок постоянной памяти новых значений набега фазы.