Аналоговое мажоритарное устройство

Иллюстрации

Показать всеРеферат

АНАЛОГОВОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО, содержащее по числу каналов входные, ключи, блок выделения среднего арифметического сигнала, отличающееся тем, что, с целью расширения области применения и повышения достоверности его работы, оно содержит блок аналоговой памяти, компаратор знака, блок вьщеления разности, блок вьщеления модулясигнала, блок задания порога, блок компараторов сигналов и дешифратор неисправного канала, выходы 9ХОДНЫХ ключей соединены соответственно с входами-блока выделения среднего арифметического си нала, выход которого соединен с входами блока аналоговой памяти и с входами блока вьщеления разности, выходы которого, соединены с соответствующими сигнальными входами блока компараторов сигналов, выходы блока аналоговой памяти соединены с входом компаратора знака и с входом блока вьщеления модуля сигнала, управляющий вход которого соединен с выходом компаратора знака, а выход через блок зада (Л ния порога - с задающими входами блока компараторов сигналов, выходы которых через дешифратор неисправного канала соединены с управляющими входами соответствующих входных ключей . СХ) 4 Х 00 ;о

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOIVIV СВИДЕТЕЛЬСТВУ (21) 3428896/18-24 .(22) 20.04.82 (46) 07.04.84. Бюл. В 13 (72) П.И. Бородин, Д.Н. Дудин и С.Н. Дылдин (53) 681.396(088.8) (56) 1. Авторское свидетельство СССР

В 720841, кл. Н 05 К 10/00, 1977.

2. Золотова Т.И. и др. Резервирование аналоговых устройств автоматики. И., "Энергия", 1975, с. 57, рис. 13 (прототип). (54) (57) АНАЛОГОВОЕ МАЖОРИТАРНОЕ

УСТРОЙСТВО, содержащее по числу каналов входные, ключи, блок выделения среднего арифметического сигнала, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения и повышения достоверности его работы, оно содержит блок аналоговой памяти, компаратор знака, блок выделения разности, блок вьщеления (19) (11)

3(б)) Н 03 К 19/23 ° Н 05 К 10/00 модуля сигнала, блок задания порога, блок компараторов сигналов и дешифратор неисправного канала, выходы входных ключей соединены соответственно с входами-блока выделения среднего арифметического сигнала, выход которого соединен с входами блока аналоговой памяти и с входами блока выделения разности, выходы которого соединены с соответствующими сигнальными входами блока компараторов сигналов, выходы блока аналоговой памяти соединены с входом компаратора знака и с входом блока вьщеления модуля сигнала, управляющий вход .которого соединен с выходом компаратора знака, а выход через блок задания порога — с задающими входами блока компараторов сигналов, выходы которых через дешифратор неисправного канала соединены с управляющими входами соответствующих входных ключей.

1 108

Изобретение относитея к автоматике и может быть использовано при построении высоконадежных резервированных систем управления.

Известно аналоговое мажоритарное устройство, содержащее компараторы, входы, которых соединены с входами коммутатора, а выходы — с входами дешифратора, выходы которого через ключи соединены с управляющими входами коммутатора, выход которого соединен с входом усилителя 1 1 .

Наиболее близким к изобретению является аналоговое мажоритарное устройство, содержащее .по числу каналов сумматоры, соединенные через нелинейные элементы и входные ключи с входами блока выделения среднего арифметического сигнала, выход которого подключен к входам сумматоров, выходы которых через пороговые и накопительные элементы соединены с управляющими входами входных ключей и входами релейного элемента, выход которого подключен к индикаторам 12 ).

Недостаток известных устройств заключается в отсутствии адаптации к уровням входных сигналов.

Цель изобретения — расширение области применения и повышение достоверности работы устройства за счет реализации в нем алгоритма усреднения с управляемым порогом.

Поставленная цель достигается тем, что аналоговое мажоритарное устройство, содержащее по числу каналов входные ключи, блок выделения среднего арифметического сигнала, содержит блок аналоговой памяти, компаратор знака, блок выделения разности, блок выделения модуля сигнала, блок задания порога блок

У

6 компараторов сигналов и дешифратор неисправного канала, выходы входных ключей соединены соответственно с входами блока вьделения среднего арифметического сигнала, выход которого соединен с входами блока аналоговой памяти и с входами блока выде.ления разности, выходы которого соединены с соответствующими сигнальными входами блока компараторов сигналов, выходы блока аналоговой памяти соединены с входами компаратора и с входом блока выделения модуля сигнала, управляющий вход которого соединен с выходом компаратора знака, а выход через блок задания порога — с задающими входами блока

3S

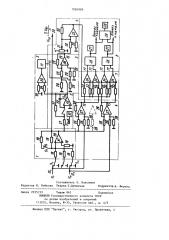

55 компараторов сигналов, выходы которых через дешифратор неисправного канала соединены с управляющими вхо- дами соответствующих входных ключей, . На чертеже приведена блок-схема аналогового мажоритарного устройства.

Устройство содержит блок 1 выделения среднего арифметического сигнала„ блок 2 аналоговой памяти, компаратор 3 знака, блок 4 выделения разности, блок 5 вьделения модуля сигнала, блок 6 задания порога, блок 7 компараторов сигналов, дешифратор 8 неисправного канала, входные ключи 9 -9„, переключатель 10 режима, переключатель 11 знака, выходы 12.-12, каналов, выходы 13 блока выделения разности, выход 14 блока аналоговой памяти, выход 15 компаратора знака, выход 16 блока вьделения модуля сигнала, выходы 17 бло ка компараторов сигналов. Блок 1 содержит резисторы 18, ключ 19, операционный усилитель 20; в блок 2 — резисторы 21, конденсатор 22, операционный усилитель 23; блок 3 — резисторы 24, операционный усилитель 25; блок 4 — резисторы 26, операционные усилители 27; блок 5 — резисторы 28, операционный усилитель 29; ,блок 6 — резисторы 30, переменный резистор 31, операционный усилитель 32; блок 7 — резисторы 33, операционные усилители 34; блок 8 — первые 35 и вторые 36 элементы ИЛИ, первые 37 и вторые 38 ключи, выход 39 устройства. Выходы 12>-12„ каналов через входные ключи 91-9 соединены с входами блока 1 выделения среднего арифметического сигнала, выход которого соединен с входом блока 2 аналоговой памяти и с входами блока 4 выделения разности, выходы 13 которого соединены с сигнальными входами блока компаратора 3 знака и с входами блока 5 вьделения модуля сигнала, а выход 15 компаратора знака через контакты переключателя 11 знака соединены с входом блока 5 вьделения модуля сигнала, выход 16 которого через блок б задания порога соединен с опорными входами блока 7 компараторов, выходы 17 последних через дешифратор отказавшего канала 8 посредством контактов ключей 9 -9

1 Il включены в выходные цепи каналов.

Аналоговое мажоритарное устройство работает следуюшим образом.

1084989

XUsx сР

+KU ворог о порог ср

50 р"де

Выходные напряжения U -U канаи лов поступают на блок 1, где на выходе операционного усилителя 20 получается среднее арифметическое значение входных напряжений

Это напряжение является выходным и !О поступает на выход 39 устройства потребителям. Одновременно оно поступает на блок аналоговой памяти, где запоминается с частотой выборки, определяемой внешним генератором 15 (не показан). Такое решение определяется динамическими характеристиками системы и сделано из соображений того, что наличие среднего значения из предыдущего такта устраняет лож- 2О ные срабатывания из-за запаздывания формирования среднего значения относительно текущих значений сигналов, а также для того, чтобы повысить безотказность по отношению к быст- 25 рым" отказам.

Блок 2 имеет два режима: режим записи (переключатель 10 замкнут) и режим хранения или фиксации (ключ I0 разомкнут). Напряжение с выхода блока 2 поступает на блок 5 выделения модуля сигнала, который управляется компаратором 3 знака так, что выходное напряжение усилителя 29 имеет одну полярность и не зависит от знака усредненного и запомненного сигнала. Для этого переключатель 11 подключает запомненный сигнал на прямой или инверсный входы усилителя 29 в зависимости от полярности 4О сигнала. После выделения модуля сигнала к нему добавляется пороговое напряжение Ua, а напряжение модуля сигнала умножается на К, где К— относительный коэффициент, определяющий зависимость переменной части порога от величины запомненного среднего сигнала. Таким образом

U величина постоянная, g порог равная

4Д rra вь|Ь

+В Т

hU — допустимая ошибка сис<д* темы, аддитивная составпяющая;

В максимально вс зможная мс(кс кр гизна сигналов нор мально работающеи сис темы;

Т вЂ” период выборки, за вревыб мя которого сигнал может измениться.

Полученное таким образом итоговое пороговое напряжение используется в качестве опорного в блоке 7 компараторов. Среднее арифметическое значение ранее полученного напряжения с усилителя 20 вычитается алгебраически из текущего значения напряжения каждого канала на вычитающих усилителях 27, с выходов которых напряжения поступают как сигнальные в блок.7 компапаторов. На выходах 13 усилителей 27 напряжения могут иметь разный знак, поэтому к выходу каждого усилителя 27 подключены два комI паратора, по одному на каждый знак.

В случае превышения разностным напряжением величины У по любому каПорог налу и по любому знаку срабатывает соответствующий компаратор и через элементь1 ИЛИ блока 8 выдается сигнал отказа соответствующего канала, причем с помощью ключей 371-37 „ отказавший канал исключается из усреднения с одновременным изменением коэффициента передачи усилителя 20 посредством ключа 38, контакты которого включены в цепь обратной связи усилителя 20. Сам ключ 38 включается через элемент ИЛИ 36 при отказе любого канала. При отказе следующего канала также происходит изменение коэффициента передачи усилителя 20 (не показано) аналогичным образом.

Аналоговое мажоритарное устройство позволяет создать систему с адаптацией к уровню входных сигналов, без которой работа в зоне значений сигналов, близкой к нулю, приводит к пропуску сигналов (если порог выбран по максимуму входного сигнала), если порог выбран по минимуму входного сигнала, то при максимальном сигнале возможны случаи выдачи ложных сигналов. Изменение величины порога в предлагаемом устройстве достигается простым поворотом движка потенциометра переменного резистора 33 а в устройствах с параметрическими мажоритарными устройствами приходится изменять по отдельности коэффициенты усиления отдельно взятых блоков системы.

1084989

Составитель В. Максимов

Редактор Н. Бобкова Техред Т.Дубинчак Корректор.А. ференц

Заказ 2035!53 Тираж 862 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r, Ужгород, ул. Проектная, 4