Устройство для цикловой синхронизации

Иллюстрации

Показать всеРеферат

Устройство для цикловой синхро-г нйзацйй .св. 873445, -о т л ич а-ю щ е е с я тем, что, с целью повыиения помехоустойчивости путем исключеиия ложных откликов, в него введены дополнительный регистр сдвига и два элемента К, при этом выход дешифратора синхрогруппы подсоединен к входу элемента ИЛИ через последовательно соединенные дополнительный регистр сдвига и первый элемент И, второй вход которого объединен с первым входом второго элемента И и под ключен к второму выходу дополнительного регистра сдвига, третий выход которого подсоединен к второму входу второго элемента И, выход которого подсоединен к дополнительному входу элемента ИЛИ, причем второй вход дополнительного регистра сдвига подключен к тактовой шине устройства. Q л tltf. LR-St эо У1 С7Г

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (191 (И) 3(5р Н 0 4 L 7/08

АНИЕ ИЗОБРЕТЕНИЯ /

OllM0

Тамг

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ (61) 873445, {211 3524458/18-09 (22! 20.12.82 (461 07.04.84, Бюл. 9 13 (721 В.М.Модринский и 6.A.È1ëûê (53i 621.394.662(088 ° 8! (561 1. Авторское, свидетельство СССР

9 873445, кл. Н 04 L 7/08, 1979 (прототип) . (54{ УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ

ПО ЦИКЛАМ.

- (571 устройство для цикловой синхро-., нйзации по авт.св. 9 873445, о т л ич а.ю щ е е с я тем, что, с целью повыаения помехоустойчивости путем исключения ложных откликов, в него введены дополнительный регистр сдвига и два элемента И, при этом выход дешифратора синхрогруппы подсоединен и входу элемента ИЛИ через последовательно соединенные дополнительный регистр сдвига и первый элемент И, второй вход которого обьединен с йервым входом второго элемента И и под" ключен к второму выходу дополнительного регистра сдвига, третий выход которого подсоединен к второму входу . второго элемента И, выход которого подсоединен к дополнительному входу элемента ИЛИ., причем второй вход дополнительного регистра сдвига подключен к тактовой шине устройства.

1085005

Изобретение относится к связи и может использоваться в приемных устройствах синхронизации по циклам систем передачи дискретной информации.

По основному авт.св. 9 873445 5 известно устройство для синхронизации по циклам, содержащее последовательно соединенные дешифратор синхрогруппы, элемент ИЛИ, регистр сдвига и дешифратор заданного состояния, 10 счетчик циклов, при этом выход регистра сдвига подключен к другому входу элемента ИЛИ, выход дешифратора заданного состояния подключен к входам "Сброс" регистра сдвига и 15 счетчика циклов, причем на счетные входы дешифратора синхрогруппы и счетчика циклов и на тактовый вход .регистра сдвига подана последовательность тактовых импульсов. 20

Однако известное устройство для цикловой синхронизации имеет сравнительно невысокую помехоустойчивость, так как все ложные отклики, генерируемые дешифратором синхрогруппы, поступают на вход регистра сдвига и, циркулируя в нем вместе с истинными откликами, могут дать на выходах первых разрядов регистра сдвига требуемое число "единиц", расположен-, .ных в порядке и количестве, определяемыми решающим правилом вхождения в синхронизм, что приводит к сбоям.

Цель изобретения — повышение помехоустойчивости путем исключения ложных откликов.

Поставленная цель достигается тем, что в устройство для цикловой синхронизации, содержащее последовательно соединенные дешифратор синхрогруппы, 4р элемент ИЛИ, регистр сдвига и дешифратор заданного состояния, счетчик циклов, при этом выход регистра сдвига подключен к другому входу элемента ИЛИ, выход дешифратора заданного 45 состояния подключен к входам "Сброс" регистра сдвига и счетчика циклов, причем на счетные входы дешифратора синхрогруппы и счетчика циклов и на тактовый вход регистра сдвига подана последовательность тактовых импульсов, введены дополнительный регистр сдвига и два элемента И, при этом выход дешифратора синхрогруппы подсоединен к входу элемента ИЛИ через последовательно соединенные дополни- 55 тельный регистр сдвига и первый элемент И, второй вход .которого объединен с первым входом второго элемента И и подключен ко второму выходу дополнительного регистра сдвига, тре-50 тий выход которого подсоединен к второму входу второго элемента И, выход которого подсоединен к дополнительному входу элемента ИЛИ, причем второй вход дополнительного регистра 65 сдвига подключен к .тактовой шине устройства.

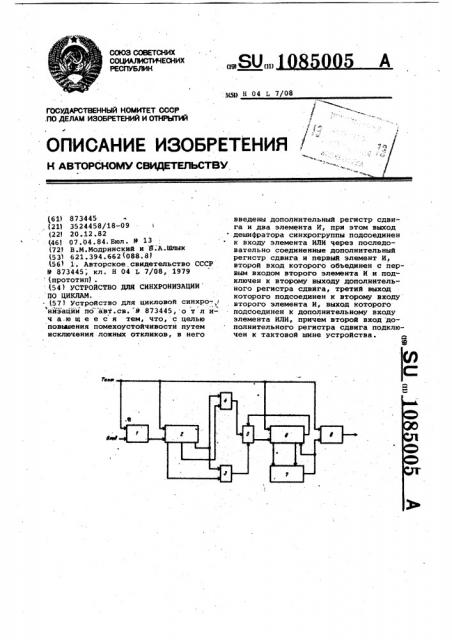

На чертеже представлена структурно-электрическая схема устройства для синхронизации по циклам.

Устройство для синхронизации по циклам содержит дешифратор 1 синхрогруппы, дополнительный регистр 2 сдвига, элементы И 3, 4 элемент

ИЛИ 5, регистр б сдвига, дешифратор

7 заданного состояния, счетчик 8 циклов

Устройство для синхронизации по циклам работает следующим образом.

Импульсно-кодовый сигнал, поступающий на вход дешифрируется дешифратором 1, котоРнй при получении комбинации типа синхрогруппы генерирует на выходе отклик в виде "единичного" импульса, поступающего на вход дополнительного регистра 2 и записывающегося в,его первом разряде. На тактовый вход регистра.2 поступает последовательность тактовых импульсов, которые продвигают записанную в регистр

2 "единицу". При одновременном появлении "единиц" на выходах первого, .и+1-го, 2п+1-ro или первого и 2n+1ro, n+1-го н 2п+1-го ра,зрядов регистра 2, а это произойдет только в том случае, если на вход регистра 2 по- . ступям отклики, интервал между которыми равен и или 2п тактам "един

t ничный импульс поступит через элемент ИЛИ 5 на вход регистра 6 и за,писывается s его первом разряде. Записанная в регистре б "единица" продвигается тактовыми импульсами, поступающими на его тактовый вход.

Поскольку длина цикла синхронизации равна и разрядам, а длина регистра б равна и-1 разрядам, то через цикл первая записанная в регистр б "единица", пройдя с выхода регистра б через элемент ИЛИ 5 на его вход, оказывается во втором .разряде регистра б, а в первый разряд его записывается "единица", соответствующая отклику, следующему через и тактов.

Теперь по регистру б двигаются две единицы подряд. Дешифратор 7 выдает сигнал, когда на выходах первых разрядов регистра 6 появляется требуемое число "единиц", расположенных в порядке и количестве, определяемыми решающим правилом вхождения в синхронизм. Сигнал с выхода дешифратора 7 поступает на вхоц "Сброс" регистра 6 и на вход "Сброс" счетчика 8, на счетный вход которого поступают тактовые импульсы. В результате действия этого сигнала регистр 6 обнуляется и накопление "единиц" начинается в нем сначала, а счетчик 8 фаэируется, после чего на выход уст: 1085005

Составитель Т.Поддубняк

Редактор Н.Пушненкова Техред Т,Дубинчак

Корректор Л.Пилипенко

Заказ 2037/.54 Тираж 635

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж- 35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", r.Óæãoðoä, ул. Проектная, 4 ройства для синхронизации по циклам начинают регулярно поступать импульсы цикловой синхронизации. Последующие сигналы с выхода дешифратора 7 подтверждают фазу начальной установ ки счетчика 8. 5

Технико-экономическая эффективность устройства для синхронизации по циклам заключается в повышении помехоустойиивости за счет исключения ложных откликов, которые приводят к сбоямъ