Устройство для преобразования частоты

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ, содержащее последовательно соединенные опорный -генератор , многоотводный делитель частоты , первый и второй выходы опорного сигнала которого соединены соответственно с первыми и вторыми входами Н блоков добавления-исключения импульсов, управлягацие входы которых подключены к шинам команд управления , последовательно соединенные делитель частоты и полосовой фильтр, выход которого является выходом устройства ,отличающееся тем, что, с целью увеличения частотного диапазона и -снижения уровня паразитных спектральных составляющих выходного сигнала, в него введены К блоков приоритета, первый выход каждого из которых соединен с третьим входом соответствующего блока добавления-исключения импульсов, инвертор и 12VJ+1) - входовой элемент И-НЕ, первый вход которого через инвертор соединен с первым выходом опорного сигнала многоотводного делителя частоты, остальные входы - с 2Ы выходами блоков добавления-исключения импульсов, а выход - с входом .-j делителя частоты, при этом выходы S многоотводного делителя частоты сое-1 динены с первыми входами блоков прио- Гу ритета, второй вход каждого из кото-j JP, рых соединен с первым выходом опор- {|«ш ного сигнала многоотводного делителя частоты, а входы блокировки - с S вторыми выходами остальных блоков приоритета.

сООЗ сОВетсних

СОЦИАЛИСТИЧЕСКИХ

РЕСЙУ БЛИН

3(59 Н 03 К 1 156

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬС ГВУ (ьыь.нн". ." авивf

ГОСУДАРСТ8ЕИНЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИй И ОТНРЫТИй

{ 21 ) 34 42673/18-21 (22) 24.05.82 (46) 15.04.84. Бюл. 9 14

{ 72} В.С.Будяк, IO.A.Попов и Я.Ç.Ягуд .(53) 621,374(088.8) (56) 1. Авторское свидетельство СССР

9 579683, кл. Н 03 К 5/156, 1977..

2. Авторское свидетельство СССР

Ф 571927, кл. Н 04 К 27/26, 1977 (прототип).

{54)(57) 1. УСТРОИСТВО ДЛЯ ПРЕОБРА ЗОВАНИЯ ЧАСТОТЫ, содержащее последовательно соединенные опорный генератор, многоотводный делитель частоты, первый и второй выходы опор ного сигнала которого соединены соответственно с первыми и вторыми входами Й блоков добавления-исключения импульсов, управляющие входы которых подключены к шинам команд управления, последовательно соединенные делитель частоты и полосовой фильтр, выход которого является выходом

„.SU„„A устройства, о т л и ч а ю щ е е с я тем, что, с целью увеличения частотного диапазона и снижения уровня паразитных спектральных составляющих выходного сигнала, в него введены И блоков приоритета, первый выход каждого из которых соединен с третьим входом соответствующего блока добавления-исключения импульсов, инвертор и (2Ч+1) — входовой элемент

И-НЕ, первый вход которого через инвертор соединен с первым выходом опорного сигнала многоотводного делителя частоты, остальные входы — с

2К выходами блоков добавления-исклю- чения импульсов, а выход — с входом делителя частоты, при этом выходы 3< многоотводного делителя частоты сое-) динены с первыми входами блоков прио-, ритета, второй вход каждого из которых соединен с первым выходом опор- С ного сигнала многоотводного делителя частоты, а входы блокировки — с Я вторыми выходами остальных блоков приоритета..

1086553

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок приоритета состоит из двух2-триггеров, К-входового элемента И и(II+1)-входового элемента И-НЕ, причем первый вход блока. приоритета соединен с первыми входами hl -входового,элемента И и () +1) -входового элемента И-НЕ, каждый из остальных iJ-1 входов Н -входового .элемента И соединен с соответствующим входом (И+1) -входового элемента И-НЕ и через элемент задержки входом блокировки блока приоритета .выход и -входового элемента И соеди. нен с Р -входом первого Р -триггера, 5-вход которого соединен с выходом (Й +1) -входового элемента И-НЕ и

5-входом второгоЗ -триггера, С-вход с вторым входом блока приоритета и С -входом второго Э -триггера, Э-вход которого соединен с общей шиной и вторым входом блока приорите- та, инверсный выход †(с К +1)-м входом (N+1) -входового элемента И-НЕ, прямой выход -второго 2 -триггера сое

Изобретение Относится к импульсной технике и может использоваться в устройствах для синтеза дискретной сетки частот и в устройствах формирования телеграфных сигналов.

Известно устройство для импульсного преобразования частоты, содержащее последовательно соединенные генератор опорной частоты, первый дели . тель частоты, импульсный преобразователь (блок добавления-исключения), i0 второй делитель частоты .и частотный селектор (1) .

Недостатками данного устройства являются снижение частотного „циапа- с зона преобразователя частоты в случае, . 5 если устройство преобразует несколько (больше двух) импульсных последовательностей и повышенные уровни паразитных спектральных*составляющих сигнала на выходе устройства. 20

Наиболее близким к предлагаемому по технической сущности является устройство для преобразования импульсных последовательностей, содержащее последовательно соединенные 25 опорный генератор, многоотводный делитель частоты; два дополнительных блока добавления-исключения импульсов, дополнительный делитель частоты, основной блок добавления-исклю чения, основной целитель частоты и полосовой фильтр, причем выход опорного сигнала многоотводного делителя частоты соединен с вторыми динен с первым выходом, а инверсный выход — с вторым выходом блока приоритета.

3. Устройство по п. 1, о т л и-. ч а ю щ е е, с я тем, что блок добавления-исключения импульсов состоит из 3 -триггера, логических элементов

И-НЕ и инвертора, причем первый вход блока добавления-исключения импульсов соединен с С-входом, а третий вход — с 3 --входомЭ-триггера, прямой .выход которого соединен с первыми входами первого и второго элементов

И- НЕ, выходы которых являются выходами блока добавления-исключения импульсов, второй вход первого элемента И-НЕ соединен с входом инвертора, . выход которого соединен с вторым входом. второго элемента И-НЕ, причем .вход Инвертора является управляющим входом блока добавления-исключения импульсов, второй вход которого сое:динен с третьим входом второго,элемента И-НЕ... 2 входами блоков добавления-исключения импульсов, управляющие входы которых являются управляющими входами устройства, а выход делителя частоты соединен с входом йолосового фильтра, выход которого является выходом устройства (2) .

Недостатками этого устройства являются узкий частотный диапазон и высокий уровень паразитных спектральных составляющих на выходе устройства из-за наличия промежуточного делителя частоты.

Цель изобретения — увеличение частотного диапазона устройства и снижение уровня паразитных спект- 4 ральных составляющих выходного сигнала (отношение полезный сигнал/паразитная составляющая) при преобразовании в общем случае нескольких импульсных последовательностей.

Поставленная цель достигается тем, что в устройство для преобразования частоты, содержащее последовательно соединенные опорный генератор, многоотводный делитель частоты, первый и второй выходы опорного. сигнала которого соединены соответственно с первыми и вторыми входами блоков добавления-исключения импульсов, управляющие входы которых подключены к шинам команд управления, последовательно соединенные де. литель частоты и полосовой фильтр, 1086553 выход которого является выходом уст4, ройства, введены Й блоков приоритета, первый выход каждого из которых соединен с.третьим входом соответст-, вующего блока добавления-исключения импульсов, инвертор и (2К+1) -входовой элемент И-НЕ, первый вход которого через инвертор соединен с пер,вым выходом опорного сигнала много отводного делителя частоты, осталь ные входы - с 2 М выходами блоков добавления-исключения импульсов, а выход — с входом делителя частоты, при этом выходы многоотводного делителя частоты соединены с первыми входами блоков приоритета, второй 35 вход каждого из которых соединен с первым выходом опорного сигнала многоотводного делителя частоты, а входы блокировки -.с вторыми выходами остальных блоков приоритета.. 20 . При этом блок приоритета состоит из двух2 -триггеров, К -входового элемента И и (К+11 -входового элемента И- НЕ, причем первый вход блока приоритета соединен с первыми входами М -входового элемента И и (Я+1} «« входового элемента И-НЕ, каждый из остальных К -1 входов 8 -входового элемента li соединен с соответствующим входом (К+1) -входового элемента

И-НЕ и через элемент задержки с вхоgloM блокировки блока приоритета, выход К -входового элемента И соединен с 9 -входом первогоЗ -триггера, 5-вход которого соединен с выходом (К +11 -входового элемента И-НЕ и

5-входом второго D -триггера, С-вход соединен с вторыл входом блока прио- . ритета и С-входом второго2 -триггера, 3 -вход которого соединен с. общей шиной и вторым входом блока 40 приоритета, инверсный выход — с (К +1)-м входом (К+11 -входового элемента И-НЕ, прямой выход второго

9-триггера соединен с первым выходом, а инверсный выход — с вторым выходом блока приоритета.

Крселе того, блок добавления-исключения импульсов состоит из D --триггера, логических элементов И-НЕ и инвер; тора, причем первый вход блока добав- ления-исключения импульсов соединен с С-входом, а третий вход — сЗ -входомЭ -триггера, прямой выход которого соединен с первыми входами пер- . вого и второго элементов И-НЙ, выходы которых являются выходами блока добавления-исключения импульсов, вто,рой вход первого элемента И-НЕ соеди.нен с входом инвертора, выход которого соединен с вторым входом второ- 60

ro элемента И-НЕ, причем вход инвер-. тора является управляющим входом блока, добавления-исключения импульсов, второй вход которого соединен с третьим входом второго элемента И-НЕ.

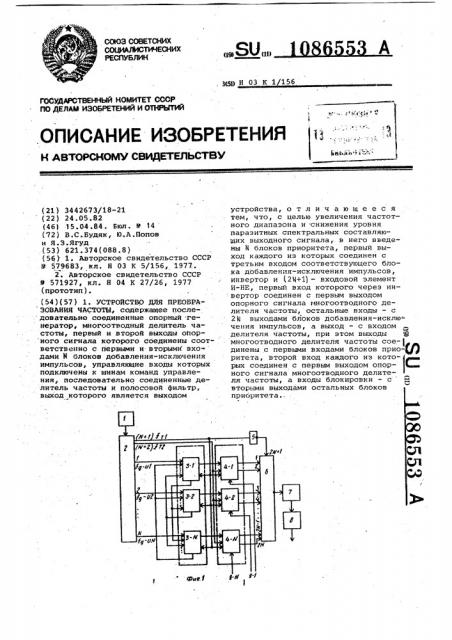

На фиг. 1 представлена структурная электрическая схема устройства для преобразования частоты; на фиг.2принципиальная электрическая схема блоков приоритете и блоков добавле" ния-исключения импульсов (для К-3); на фиг. 3 - временные диаграммы, поясняющие работу устройства.

Устройство для преобразования частоты (фиг. 11 состоит из опорного генератора 1, многоотводного делителя 2 частоты, H блоков приоритета 3-1,,..., З-К, М блоков добавления исключения импульсов 4-1, ..., 4-М, инвертора 5, (2И+1) -входового элемента И-НЕ б, делителя 7 частоты, поло сового фильтра 8, причем выход опор.ного генератора 1 соединен с входом многоотводного делителя 2 частоты, Я-выходов которого соединены соответственно с первыми входами К бло-. ков 3-1, ..., З-Я, выходы блоков

4-1 — 4-М соответственно соединены с 2М-входами элемента И-НЕ б, (ЯЙ+Ц -й вход которого соединен с выходом инвертора 5, вход которого соединен с первыми входами блоков

4-1, ..., 4-К добавления-исключения импульсов, вторыми входами блоков 3-1, ..., 3- К и первым выходом опорного сигнала многоотводного делителя 2 частоты, второй выход котОрого соединен с вторыми входами блоков 4-1-4-К„ а входы блокировки каждого иэ блоков 3-1, ..., 3-К соединены с вторыми выходами остальных блоков приоритета 3-1, ..., 3-Р, управляющие входы блоков 4-1, ..., 4- К соединены соответственно с шина ми 9-1 - 9-N команд управления -01, ...,g -0М, выход элемента И-НЕ б через делитель 7 соединен с полосовыь фильтром 8, выход которого являетс.я. выходом устройства.

Блок приоритета 3-К 1 фиг. 2 1 содержит К -входовой Логический элемент

И 10-Й, (Й +1) -входовой элемент ИНЕ 11-К,Я-триггеры 12-Я, второй 13-К, (К -11 элементов задержки 14-1, 14(К-1) причем первый вход блока приоритета 3-К соединен с первыми входами К входового элемента И 10-К и (К+11-входового элемента H-H8 11-Й остальные К-1 входов К -входового элемента И 10- К соединены с соответствующими входами (К +11-входового элемента И-НЕ 11-Я и через элементы задержки 14-1, ...,141К-1) с входами блокировки блока приофйтета З-Н, выход К -входового элемента И 10-Й соединен c D -входом первого 3-триггера 12-8, 6 -вход которого соединен с выходом (К +11-входового элемента

И"НЕ 11"М и 5 -входом второго

Э-триггера 13-К, С-вход соединен с

С-входом второго З -триггера 13-К, 1086553

9-вход которого соединен с общей шиной, и вторым входом блока приоритета, инверсный выход — с (8+1) -м входом(8+1) -входового элемента И-НЕ

11-К, прямой выход второго 9-триггера 13-й соединен с первым выходом, а инверсный выход — с вторым выходом блока приоритета З-М.

Блок добавления-исключения импульсов 4- К (фиг. 2) содержит 3-триггер

15-.Ц, первый, второй логические элементы 1б-й, Й-RE 17-Н и инвертор .

18-К, причем третий вход блока добавления-исключения импульсов соединен с 2 -входом, а первый вход - с С-входом З-триггера 15-К, прямой выход которого соединен с первыми входами первого 16-й и второго 17- и элементов И-НЕ, выходы которых являются выходами блока добавления-исключения импульсов 4-Й, второй вход первого.

20 элемента И-НЕ 16-Й соединен с входом инвертора 18-Й, выход которого соединен с вторым входом второго элемента И-НЕ 17 N, третий вход которого соединен с вторым входом блока 4-N.

Устройство для преобразования частоты на примере преобразования четырех импульсных последовательностей

1Т1, fg -01 ... Я вЂ” 0 3 работает согласно импульсной диаграмме, приведенной на фиг. 3.

30

С выходов опорного сигнала многоотводного делителя 2 -частоты поступают .актовые импульсные последователь ности 1 7 1 (фиг. 3.1) с первого иЮТЯ 35 (фиг. 3.2) с второго, которая сдвинута на 180 относительно f T1, и. три импульсные последовательности с чаСтотами добавления-исключения -01 (фиг. 3. 3),f g -02 (фиг. 3. 5) и fg -0 3 40 (фиг. 3.7), кроме того, на вход уп- равления устройства поступают коканды добавления-исключения импульсов

g-Ц1 (фиг. 3.4), Я - ц2 (фиг. 3.6) и

g-

11-1 логическая "1" (фиг. 3.9), на выходе элемента 10-1 логический ™О", на выходе 9 первого 3 -триггера 12-1 ° логический "0" (фиг. 3.10). В момент пр.хода переднего фронта импульса

1 -О1 Я,) на выходе элемента И-HE

1 -1 (фиг. 3.9) появляется короткий отрицательный импульс, который перебрасывает второйП -триггер 13-1 в логическую "1" и Q выход первого

3-триггера 12-1 в логический "0", запирая вход элемента И-НЕ 11-1 и перебрасывая его выход в логическую 60

"1". Отрицательный импульс (логический "0") с выхода g2 -триггера 13-1 запирает с момента k, блокирующие входы fg -02 и kg -ц 3 элементов И-НЕ

11-2 и 11-3 и элементов И 10-2 и 10-3. 65

С приходом переднего фронта следующего тактового импульса последовательности 1 Т 1 (момент f, q) выход Я второго 9-триггера 13-1 перебрасывается в логический "0", а ч 2 -триггера

12-1 — в логическую "1", отпирая блокирующие входы fg.-02 и fg 03 блоков 3-2:и 3-3. В мрмент 1д логическая "1" на выходе Я второго0-триг. гера 13-1 переписывается в 3 - триггер 15-1 (фиг. 3.12), а с приходом следующего тактового импульса f T1 (момент t3) выход ЦП -триггера 15-1 перебрасывается в логический "0", сформировав положительный импульс, который инвертируется элементом И-НЕ

16-1 (фиг. 3.13), когда на входе (-01 логическая "1". Далее этот отрицательный импульс поступает на вход элемента И-НЕ 6, формируя на выходе элемента (фиг. 3.20) в момент 1 -1 один широкий импульс взамен двух входных импульсов. последовательности

1Т1 (операция исключения). В момент, когда на входе (-U1 присутствует логический "0", на выход элемента И-НЕ

17-1 проходит один отрицательный импульс из последовательности Т2 (фиг. 3.14), который образует на выходе элемента б (фиг. 3.20) один дополнительный импульс в выходной импульсной последовательности (операция добавления) .

Рассмотрим случай, когда в промежутке между двумя тактовыми ймнульсами последовательности f T1 (момент

t4 -tg) поступают -на вход блоков приоритета передние фронты трех импульсов последовательностей 1g --01 fg -ц2, fg-u3.

Первым поступает импульс kg -02,,который перебрасывает выход0 второго g -триггера 13-2 в логическую "1" (фиг. 3.15), а выход Я вЂ” в логиче ский "0", запирая блокирующие входы

fg-. Ц1 иff -03 блоков 3-1 и 3-3, блокируя входы элементов И-,НЕ 11-1, 11-3 и элементов 10-1, 10-3. В мо- мент 3< D .-триггер 13-2 перебрасывается и снимает блокировку (логический

"О") входов1 -ц1 и fg о3. Так как блок 3-1 имеет большими приоритет (на входах нет- элементов задержки), то в момент времени 4g -t6 формируется импульс на выходе q D -триггер

13-1 (логическая "1") и на выходе Я второго 2-триггера 13-1 (лог. "0"), который блокирует вход fg -03 блока

3-3,. В этот же момент на выходе

g-триггера 15-2 (фиг. 3.17) формируется переписанный с второго П-триггера 13-2 импульс, который образует импульс добавления (или исключения) на выходах элементов И-НЕ 16-2 и с

17-2. С приходом следующего тактового импульса т Т1 (момент f6) 9-триг1086553

40 гер 13- 1 опрокид 1вается, блокировка

tg-Î3 снимается.,0 -триггер 13-3 формирует импульс (фиг. 3.18), который с приходом следующего тактового импульса g Т1 переписывается в 9 -триггер 15-3 (фиг. 3.19) и формирует

5 импульс исключения (добавления) на выходах элементов И-НЕ 16-3 и 17-3.

Назначение Э-триггеров 12-1, 12-2, 12-3, ° ., 12- H в блоках приоритетаформировать короткие отрицательные импульсы на выходах элементов И-Н3

11-1, 11-2, ..., 11- N и запирать входы ig -0 блоков приоритета во время поступления импульсов fg -U на соответствующий вход с лока (фиг.3.11, 5

1с фиг. 3.16). По заднему фронту импульсов kg -О первые D-триггеры 12-1, 12-2, ..., 12-H фиксируют готовность входов fg -U, отпирая элементы

И-НЕ 11-1, 11-2, ..., 11-N. Назначе- 20 ние элементов И 10-1, 10-2, 10- М вЂ” фиксировать выход.Ц D тригге- ров 12-1, 12-2, ..., 12-N в состоянии (логической "1") отпирания (готовностн1 входов fg — 0 соответствующе-25

1О блока приоритета во время одновре- менр.ого поступления на входы всех трех импульсов fg -U (момент tg -tgt6) . Время задержки элементов 14-1,:

14-М выбирается с учетом степе- Зр ни приоритета блоков добавления исключения 4-1...4-H в зависимости от длительности импульсов последовательностей fa -0.

В предлагаемом устройстве (фиг. 2) 35 . принята следующая степень приоритета блоков 3-1, 3-2, 3-3. Элементы задержки могут выполняться на обычных логических элементах. В описанном примере длительность импульсов

kg-01 не должна быть меньше 2Т1, где Т1 — период следования тактовой. последовательности fT1.

Таким образом, при рассмотрении принципа работы предлагаемого устройства для преобразования частоты становится очевидным, что частота выходной импульсной последовательности в общем случае равна

1, tg.uiikg Ы+.„ fg-0Н вен и где rl - коэффициент деления делите-. ля 7 частоты.

Преимуществом предлагаемого уст-. ройства по сравнению с известными является расширение частотного диапа-; зона и снижение уровня паразитных составляющих, образующихся за счет дискретных преобразований импульсных последовательностей в 4Н раза,. где и — число преобразований импульс ных последовательностей, так как использование блоков. добавления-исключения импульсов для преобразования нескольких импульсных последователь- ностей предполагает наличие промежуточных делителей частоты с коэффи. циентом деления в лучшем случае 4.

Кроме того, предлагаемый блок.добавления-исключения импульсов проще, чем известные, что приводит к повы- шению надежности работы ус ройства и уменьшению количества используемых элементов при реализации количества преобразований N v 1. Также экономическая эффективность определяется уменьшением количества фильтрующих элементОв, снижением требований к крутизне скатов АЧХ. выходного фильт ра, что в свою очередь обуславливает снижение затрат на изготовление и настройку этого фильтра. Устройство достаточно просто, надежно в работе, выполнено целиком на элементах цифровой техники, ехнологично.

1086553

108655З

1У 575

70 И5

«! «Ф «5

4 «у«ф

Фиг. 3

Составитель М.Фирстова

Техред Л.Иикеш

Редактор А;Гулько

Корректор.Л.Пилипенк .

Филиал ППП "Патент"; г.ужгород, ул.Проектная., 4

Заказ 2266/52 Тираж- 8б2 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб;, д. 4/5