Преобразователь кода грея в двоичный код

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ КОДА ГРЕЯ В ДВОИЧНЫЙ КОД, содержащий триггеры, установочные входы которых являются информационными входами преобразователя , вход синхронизации которого соединен с синхровходами триггеров, выходы которых являются выходами преобразователя, отличающийс я тем, что, с целью повышения быстродействия и расширения функциональных возможностей путем обеспечения обратного преобразования, в него введены (п-1) группа элементов И, где п - число разрядов входного кода, группа элементов ИЛИ, четыре элемента И, два элемента ИЛИ и элемент НЕ, вход которого соединен с выходом первого элемента ИЛИ группы и с первыми входами первого и второго элементов И, выходы элементов И ,1-й группы fi 1-(п-1) соединены с входами i-ro элемента ИЛИ группы, выход которого соединен с управляющим входом (i+l)-ro триггера, прямой выход которого соединен с первым входом первого элемента И i-й группы , второй вход которого соединен с инверсным выходом i-ro триггера, прямой выход которого, кроме п-го; соединен с первым входом второго элемента И i-й группы, второй вход которого соединен с инверсным выходом (i+l)-ro триггера, третьи входы первого и второго элементов И J-й группы t,.3 соединены с первыг. управляющим входом преобразователя , второй управляющий вход которого соединен с первыми входами третьего и четвертого элементов И j-й группы, вторые входы которых соединены соответственно с прягФпи и инверсным выходами (J+l)-ro триггера, третьи входы третьего и четвертого элементов И (п-1)-и группы соединены I соответственно с выходами первого (Л и второго элементов ИЛИ, третьи выходы третьего и четвертого элементов И (п-2)-й группы соединены соответственно с выходом первого элемента ИЛИ группы и выходом элемента НЕ, прямой выход (п-1)-го триггера - с первыми входами третьего и четвертого элементов И, вторые -входы которых соединены соответственно с выоо ходом элемента НЕ и выходом первого элемента ИЛИ группы, вторые входы Ni первого и второго элементов И сое динены с инверсным выходом (п-2)-го триггера, выходы первого и третьего 00 00 элементов И - с входами первого элемента ИЛИ, выходы второго и четвертого элементов И -,с входами второго элемента ИЛИ, прямой выход первого триггера - с управляющигл входом первого триггера.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬП ИЙ (21) 3567732/18-.24 (22) 30.12.82 (46) 23 ° 04.84. Бюл. 9 15 (72) A.Ë.Õëþíåâ и A.A.Êóçíåöoâ (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

9 788104, кл. G 06 F 5/02, 1978.

2. Авторское свидетельство СССР

9 658556, кл. G 06 F 5/02, 1977 (прототип). (54)(57) ПРЕОБРАЗОВАТЕЛЬ КОДА ГРЕЯ

В ДВОИЧНЫЯ КОД, содержащий триггеры, установочные входы которых являются информационными входами преобразователя, вход синхронизации которого соединен с синхровходами триггеров, выходы которых являются выходами . преобразователя, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия и расширения функциональных возможностей путем обеспечения обратного преобразования, в него введены (n-1) группа элементов

И, где n - число разрядов входного кода, группа элементов ИЛИ, четыре элемента И, два элемента ИЛИ и элемент НЕ, вход котор >го соединен с выходом первого элемента ИЛИ группы и с первыии входами первого и второго элементов И, выходы элементов И ,i-й группы i =1-(n-1)1 соединены с входами i-ro элемента ИЛИ группы, выход которого соединен с управляюIgHM входом (i+1)-го триггера, прямой выход которого соединен с первым входом первого элемента И i-й группы, второй вход которого соединен

„„SU„„1087983 А с инверсным выходом i-ro триггера, прямой выход которого, кроме и-roð соединен с первым входом второго элемента И i-й группы, второй вход которого соединен с инверсным выходом (i+1)-го триггера, третьи avo - ды первого и второго элементов И

)-й группы f,j=7,-(п-l) ) соединены с первым управляющим входом преобразователя, второй управляющий вход которого соединен с первыми входами третьего и четвертого элементов И ,)-й группы, вторые входы которых соединены соответственно с пряьым и инверсным выходами ()+1)-ro триггера, третьи входы третьего и четвертого элементов И (и-1)-й группы соединены,р

O соответственно с выходами первого и второго элементов ИЛИ, третьи выходы третьего и четвертого элементов

И (и-2)-й группы соединены соответственно с выходом первого элемента

ИЛИ группы и выходом элемента НЕ, прямой выход (n-1)-ro триггера - с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с выходом элемента НЕ и выходом первого элемента ИЛИ группы, вторые входы первого и второго элементов И соединены с инверсным выходом (и-2)-го триггера, выходы первого и третьего элементов И вЂ” с входами первого элемента ИЛИ, выходы второго и четвертого элементов И вЂ .с входами второго элемента ИЛИ, прямой выход первого триггера — с управляющим входом первого триггера.

1087983

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах ввода и вывода и преобразования вычислительных, управляющих и измерительных систем для преобразования как кода Грея в двоичный код, так и для преобразования двоичного кода в код Грея.

Известен преобразователь кода Грея в двоичный код, содержащий распре- t0 делитель, выходной регистр, элемент задержки, счетный триггер, элементы

И, элементы ИЛИ (1).

Недостатки известного преобразователя состоят в низком быстродействии, 35 что обусловлено последовательной обработкой разрядов входного кода, и невозможность обратного преобразования.

Наиболее близким к предЛагаемому з0 по технической сущности и схеМному построению является преобразователь кода Грея в двоичный код, содержащий элементы И-НЕ, элементы ИЛИ-НЕ, триггеры, входы которых соединены с информационными входами преобразователя, а выходы янляются выходами преобразователя, вход синхронизации которого соединен с синхровходами триггеров (23.

Недостатки известного преобразователя состоят в относительно. низком быстродействии и невозможности обратного преобразования.

Целью изобретения является повышение быстродействия и расширение функциональных возможностей путем обеспечения обратного преобразования.

Поставленная цель достигается тем, что в преобразователь кода

Грея н двоичный код, содержащий триггеры, установочные входы которых являются информационными нходами преобразователя,.вход синхронизации которого соединен с синхровходами триггеров, выходы которых являются выходами преобразователя, дополнительно введены (и-1) группа элемен° тон И, где n — число разрядов входного кода, группа элементов ИЛИ, четыре элемента И, дна элемента ИЛИ и элемент НЕ, вход которого соединен с выходом первого элемента ИЛИ группы и с первыми входами первого,55 и второго элементов И, выходы элементов И i-й группы (i=1 (fl-1)) соединены с входами i-ro элемента

ИЛИ группы, выход которого соединен с управляющий входом (>+11 -го 60 триггера, прямой выход которого соединен с первым входом первого элемента И i-й группы, второй вход которого соединен с инверсным выходом 1-гo триг-. гера, прямой выход которого кроме и-го, соединен с первым входом второго элемента И i-й группы, второй вход которого соединен с инверсным выходом (i +1)-r» триггера, третьи входы первого и второго элементов

И 3-й группы (3=2-(и-1)7 соединены с первым управляющим входом преобразователя, второй управляющий вход которого соединен с первыми входами третьего и четвертого элементов

И J-й группы, вторые входы которых соединены соответственно с прямым и инверсным ныходами ()+1 )-rо триггера, третьи входы третьего и четвертого элементов И (и-1)-й группы соединены соответственно с выходами первого и второго элементов ИЛИ < третьи входы третьего и четвертого элементов И (и-2)-й группы соединены соответственно с выходом первого® элемента ИЛИ группы и выходом элемента НЕ, прямой выход (n-1)-го триггера — с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с выходом элемента НЕ и выходом первого элемента ИЛИ группы, вторые нходы первого .и второго элементов И соединены с инверсным выходом (n-2)-го триггера, выходы первого и третьего элементов И вЂ” с входами первого элемента ИЛИ, выходы второго и четвертого элементов И вЂ” с входами второго элемента ИЛИ, прямой выход первого триггера — с управляющим нходом первого триггера.

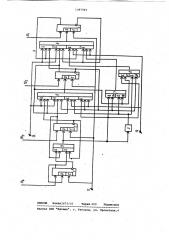

На чертеже приведена блок-схема предлагаемого преобразователя.

Преобразователь содержит триггеры 1-4, элемент HE 5, группу элементов ИЛИ б, первый и второй элементы

ИЛИ 7 и 8, группы элементов И 9, информационные входы 10 преобразователя, вход 11 синхронизации преобразонателя, первый и второй управляющие входы 12 и 13 преобразова-. теля, элементы И 14-17.

Преобразователь имеет два режима работы: режим преобразования кода

Грея в двоичный код; режим преобразования двоичного кода в код

Грея.

Режим работы определяется управляющим сигналом на входах 12 и 13.

В режиме преобразования кода Грея в двоичный код триггерам 1-4 присваивается значение кода Грея, поступающее на информационные входы 10.

Сигнал, поступающий на управляющий вход 12, разрешает преобразование кода Грея в двоичный код.

Элементы И 9 первой группы совместно с первым элементом ИЛИ б группы реализуют функцию у, =Х Х ч

1087983

15

35 и по формуле = -Т вЂ - . 1оо%

Т ч Х„Х2, элемент НЕ реализует

Функцию

У =X,Х l9„X, на выходе элемента ИЛИ 7 реализуется.

Функци У =У2 ХЭ У2 . _#_3=(XYX t X2) ,R> v (X 1 Xz v i X2 Х, на выходе элемента ИЛИ 8 реализуется функция У4 = v x3×Ó Х = (Х„Х Ч Х., Х2)

«Х> V(X1 X> Y Х Х ) Х> ходе второго элемента ИЛИ 6 группы реализуется функция У =У„ Х> (при преобразовании кода Грэя ) ч У Х> (при преобразовании кода Грея ), на выходе третьего элемента ИЛИ б группы реализуется функция у =уз Х+ (при преобразовании кода

Грея ) v у < Х (при преобразовании кода Грея ). 20

П р и и е р 1. Пусть триггерам 1-4 присвоено значение 1011 (код Грея). Тогда У1=1, У2 =О, У3 =О, У4 =1, У =О, У =1 °

На Д-входе первого триггера 1 при-25 сутствует "1", на Д-входе второго триггера 2 - "1", на Д-входе третьего триггера 3 — "О", на Д-входе четвертого триггера 4 — "1".

С приходом синхроимпульса триггерам 1-4 присвоено значение 1101 (двоичный код }, т.е. осуществлено преобразование кода Грея (1011) в двоичный код (11011 .

В режиме преобразования двоичного кода в код Грея триггерам 1-4 присваивается значение двбичного кода, поступающее на информационные входы 10. Сигнал, поступающий на Уп- 40 управляющий вход 13, разрешает преобразование двоичного кода в код

Грея. При этом У„=Х „X ITX Х, а на выходе второго элемента ИЛИ группы Формируется Функция У =х2х > ч х > 45

3

При преобразовании двоичного кода третий элемент HJIH 9 группы реализует ФУнкцию Уtt=X> Х4 Х Х +..

Пример 2. Пусть триггерам 1-4 присвоено значение 1010 (двоичный код ). Тогда У„.=1, У1=1, Ь

На Д-входе первого триггера 1 присутствует "1", на Д-входе второ« го триггера 2 — "1", на Д-входе третьего триггера 3 — "1", на Двходе четвертого триггера 4 - 1" .

С приходом синхроимпульса триггерам 1-4 присвоено значение 1111 (код Грея), т.е. осуществлено преобразование двоичного кода (1010) в код Грея (1111).

Время занесения числа, поступившего по шинам Й„- I44 раВНО Tу н=

=4t время срабатываний. каждого триггера равно T =6 i, а задержка каждого элементарного логического элемента Т „ = т . Время преобразования определяется временем задержки прохождения сигнала по самой длинной цепи, тогда быстродействие известного преобразователя опре, деляется значением

Т Т9н+Тс+ 2i(И+ НЕ+И+ ИЛИ+ 9a н

+ НЕ + И + НЕ ) = 24т, а быстродействие предлагаемого преобразователя определяется значением

Т = Т34н+ Т + ь (И + ИЛИ + НЕ

+ И + йЛИ + и + HJIH) = 17 Г равно 28% .

Таким образом, предлагаемое изобретение позволяет повысить быстродействие кода Грея в двоичный код на

28%, а также расширяет; функциональные возможности за счет введения режима преобразования двоичного кода в код Грея.

1087983

ВНИИПИ Заказ 2673/45, Тираж 669 Подписное

М I»

Филиал НПП Патеит", r. Ужгород, ул. Проектная,4