Вычислитель разности квадратов двух чисел

Иллюстрации

Показать всеРеферат

ВЫЧИСЛИТЕЛЬ РАЗНОСТИ КВАДРАТОВ ДВУХ ЧИСЕЛ, содержащий элемент ИЛИ, элемент задержки, счетчик, сумматор по модулю два, триггер, группу элементов И, элемент И и накапливающий сумматор, причем первый и второй входы элемента ИЛИ соединен соответственно с первым и вто- ; рым входами сумматора по модулю два и являются информационными входами вьпгислителя, второй вход элемента ИЛИ соединен с первым входом элемента И, -выход которого соединен с входом установки в 1 триггера, выход элемента ИЛИ соединен с входом элемента эадержки, разрядные входы счетчика соединены соответственно с первыми входами элементов И группы, отличающийся тем, что, с целью упрощения вычислителя , выход элемента эадержки соединен с тактовым входом счетчика, выход cjT iMaTopa по модулю два соединен с вторым входом элемента И, с первым разрядным входом накапливаю (/} щего сумматора и с вторыми входами элементов И группы, выходы элементов И группы соединены соответственно с разрядньми BXOja,aMH накапливающего сумматора, начиная с второго. Вшод 00 ;р со {&

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(50 С06Р 7 62

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ЮМУОд

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

FI0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТЮ (2)) 3534080/18-24 (22) 30.11.82 (Аб) 23.04.84. Бюл. -15 (72) В.А. Добрыдень и В.Г. Федоров (71) Харьковский инженерно-строительный институт (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

9 430389, кл.. G 06 F 7/38, 1974..

2. АвтоРско свидетельство СССР

В 780006, кл. G 06 F 7/38, 1980 (прототип). (54)(57) ВЫЧИСЛИТЕЛЬ РАЗНОСТИ КВАД-, РАТОВ ДВУХ ЧИСЕЛ, содержащий элемент ИЛИ, элемент задержки, счетчик, сумматор по модулю два, триггер, группу элементов И, элемент И и накапливающий сумматор, причем первый и второй входы элемента ИЛИ соединен соответственно с первым и вторым входами сумматора по.модулю

„„SU„„1087994 А два и являются информационными входами вычислителя, второй вход элемента ИЛИ соединен с первым входом элемента И, .выход которого соединен с входом установки в "1" триггера, выход элемента ИЛИ соединен с входом элемента задержки, разрядные входы счетчика соединены соответственно с первыми входами элементов И группы, отличающийся тем, что, с целью упрощения вычислителя, выход элемента задержки соединен с тактовым входом счетчика, выход сумматора по модулю два соединен с вторым входом элемента И, с первым разрядным входом накапливающего сумматора и с вторыми входами элементов И группы, выходы элементов И группы соединены соответственно с разрядными входами накапливающего сумматора, начиная с второго.

1087994

Изобретение относится к цифровой вычислительной технике и может быть. . использовано в составе систем обработки информации.

Известно устройство для вычисления разности квадрата двух чисел, содержащее накапливающий сумматор, триггер и элемент И (1 ) °

Недостатком данного устройства является его малое быстродействие 10 при обработке число-импульсных последователей, обусловленное предварительным преобразованием число-импульсного кода в параллельный код.

Наиболее близким по технической 15 сущности к изобретению является устройство для вычисления разности .квадратов двух чисел, содержащее накапливающий сумматор, триггер управления и элемент И, первый вход 2п которого подключен к единичному выходу триггера управления, триггер знака, сумматор по модулю два, групу элементов И, элемент задержки, счетчик и элемент ИЛИ, первый и 25 второй входы которого соединены с соответствующими входами устройства н с соответствующими входами сумматора по модулю два, причем второй вход элемента ИЛЙ соединен с вторым входом элемента И, а выход - с входом элемента задержки и вхо4 дом второго разряда счетчика, разрядные выходы которого соединены с вторыми входами элементов И группы, 35 первые входы которых соединены с выходом элемента задержки, а выходы подключены к разрядным входам накапливающего сумматора, выход сумматора по модулю два подключен к единичному входу триггера управления, единичный выход которого поключен к третьим входам элементов И группы, выход элемента И соединен с единичным входом триггера знака l21 .

Недостатком известного устройства является его сложность.

Целью изобретения является упро-, - щение вычислителя.

Поставленная цель достигается тем, что в вычислителе разности квадратов двух чисел, содержащем элемент ИЛИ, элемент задержки. счет-; чик, сумматор по модулю два, триггер,i группу элементов И, элемент И и наКапливающий сумматор, причем первый 55 и второй входы элемента ИЛИ соеди.ненны соответственно с первым и вторым входами сумматора по модулю два и являются информационными входами.вычислителя, второй вход элемента

ИЛИ соединен с первым входом элемента И, выход которого, соединен с входом установки в "1" триггера, выход элемента.ИЛИ соединен с вхо- дом элемента задержки, разрядные выходи счетчика соединены соответственно с первыми входами элементов 11 группы, выход элемента задержки соединен с тактовым входом счетчика, выход сумматора по модулю два соединен с вторым входом элемента И, с первым разрядным входом накапливака1его сумматора и с вторыми входами элементов И группы, выходы элемен-, тов И группы соединены соответственно с разрядными входами накапливающего сумматора, начиная с второго.

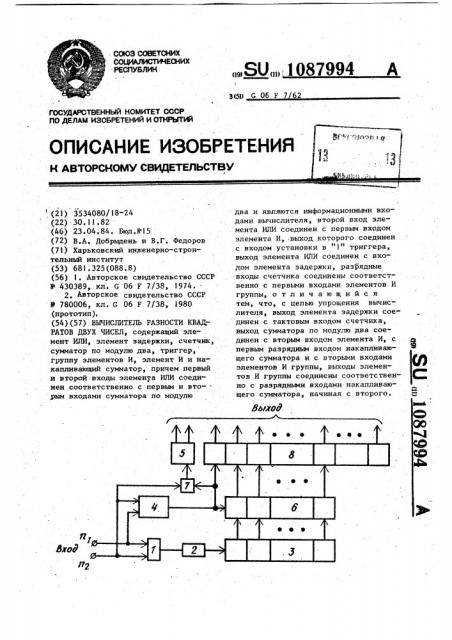

На чертеже представлена функциональная схема вычислителя разности квадратов двух чисел.

Вычислитель разности квадратов двух чисел содержит элемент- ИЛИ 1, элемент 2 задержки, счетчик 3, сумматор 4 по модулю два, триггер 5, группу элементов И 6, элемент И 7 и накапливающий сумматор 8, причем первый и второй входы элемента ИЛИ 1 соединены соответственно с первым и вторым входами сумматора 4 по модулю два и являются информационными входами вычислителя, второй вход элемента ИЛИ 1 соединен с первым входом элемента И 7, выход которого соединен с входом установки в "1". триггера 5,выход элемента

ИЛИ 1 соединен с вхоцом элемента 2 задержки, выход которого соединен с тактовым входом счетчика 3, разрядные выходы счетчика 3 соединены с первыми входами элементов И 6 группы, вторые входы которых соединены с выходом сумматора 4 по модулю два, вторым входом элемента И 7 и с первым разрядным входом накапливающего сумматора 8, выходы элементов И 6 группы соединены соответственио с остальными разрядными входамн накапливающего сумматора 8, начиная с второго.

В вычислителе используется следующее представление квадрата числа

1п1-1

О =0, n2=Z (2 + ) при п1ьО . (1)

1=0

Соответственно разность квадра" . тов двух чисел 61 и п может быть представлена в виде !087994 при)в )7 п !

2 2»

ll1 02 (2) ! и )п„)<1п, Э

В исхоцном состоянии счетчик 3, триггер 5 и накапливающий сумма- . тор 8 установлены в "A".

Необходимым условием нормальной работы вычислителя является синхронность импульсов па обоих входах (эти импульсы могут формироваться одним и тем же генератором ).

При поступлении импульсов на оба входа элемента ИЛИ 1 íà .его выходе (вследствие синхронности входных импульсов ) формируется один импульс.

Импульс на выходе сумматора 4 по модулю два формируется только в том случае, когда импульс поступает на один из его входов, если же импульсы на входах отсутствуют или появляются на обоих входах одновременно, выходной импульс не возникает (сумматор 4 по модулю два представляет собой в данном случае импульсный элемент неравнозначности(Числа п1 и и начинают формиро- ЗО

2 ваться на входах вычислителя одновременно. Пусть n y h

При этом первые h импульсов бу» дут поданы синхронно на оба входа вычислителя. На выходе сумматора 4 з5 по модулю два импульсы в этом режиме не возникают, т.е. триггер 5 и накапливающий сумматор 8 остается в исходном нулевом состоянии. Каждый же импульс с выхода элемента 40

ИЛИ l, проходя через элемент 2 за-" держки, увеличивает содержимое счет" чика 3 на единицу. Следующий (и +1)-й входной импульс подается только на вход п1 устройства. При 45 этом одновременно с ним возникает импульс на выходе сумматора 4 по модулю два, этот импульс не из /

У меняя, состояния триггера 5 (так как отсутствует импульс, на втором входе элемента И 7 ), вызывает прибавление к содержимому накапливающего сумматора 8 числа 2н2+1.

Действительно, в это время на счетчике 3 зафиксировано число 112 (последний входной импульс еще

ВНИИПИ Заказ 2674 46

1Филиал ППП Патент r.Ó

4 не достиг счетчика.З через элемент 2 задержки ) причем разрядные выходы счетчика 3 соединены с pasрядными входами накапливающего сумматора 8 через элементы И 6 группы со сдвигом на один разряд в сторону старших разрядов, а единица в первый (младший ) разряд накапли" вающего сумматора 8 поступает не-,. посредственно с выхода сумматора 4 по модулю два.

Время задержки элемента 2 выбирается достаточным для завершения передачи содержимого счетчика через элементы И 6 группы, но меньшим интервала между входными импульсами.

С приходом последнего h -ro..

;входного импульса содержимое накапливающего сумматора 8 увеличивается, аналогично описанному на 2(п„-T)+1, т.е. результат вычислений форми, руется в соответствии с формулой (2).

Если .h1 g h2 то вычислитель работает точно так же при обработке первых П1 импульсов, поступающих одновременно на, оба входа. Следующий импульс поступает только на вход !1 вычислителя, при этом импульсы возникают одновременно на обоих входах элемента И 7, в результате чего триггер 5 перейдет в единичное, состоя:ние, индицируя этим отрицательный знак результата вычислений, в остальном работа вычислителя протекает совер,шенно аналогично раесмотреному случаю.

Повышение быстродействия обусловлено тем, что в известном устройстве нечетное число, которое необходимо (при поступлении очередного входного импульса только на один из входов ,устройства ) прибавить к содержимому накапливающего сумматора, формируеся только после прихода этого импульса, в то время как в предлагаемом случае оно формируется заранее, в течение предыдущего такта, и при поступлении входного импульса остается лишь прибавить это числс .к предыдущему результату.

Предлагаемыи способ формирования указанных нечетных чисел и состояний триггера знака позволяет упростить вычислитель, исключив из его состава триггер управления и один разряд счетчика, а также соответствующий ему элемент И 6 группы.

Тираж 699 Полисное жгород, ул.Проектная, 4