Распределительное устройство

Иллюстрации

Показать всеРеферат

РАСПРЕДЕЛИТЕЛЬНОЕ УСТРОЙСТВО , содержащее ячейки памяти, каждая из которых состоит из,элементов И и ИЛИ, причем выход элемента И каждой ячейки памяти соединен с первым вхо дом элемента ИЛИ данной ячейки памяти и является выходом распределительного устройства, выход элемента ИЛИ каждойячейки памяти соединен с первым , входом элемента И данной ячейки памяти , и формирователь тактовых импульсов , содержащий Т-триггер и элемент НЕ, отличающийся тем, что, с целью Упрощения устройства, второй вход элемента И каждой ячейки памяти, кроме первой, соединен с выходом элемента И предыдущей ячейки памяти, а второй вход элемента И . первой ячейки памяти является управ . ляющим входом распределительного устройства, прямой и инверсный выходы Т-триггера соединены с вторыми § входами элементов ИЛИ нечетных и четных ячеек памяти Соответственно, (Л Т-вход Т-триггера подключен к выходу элемента НЕ, вход которого является тактовым входом распределительного устройства, а R-вход Т-триггера подключен к управляющему входу распределительного устройства. 00 00 о 4

СОЮЗ СО8ЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

074 А (19) (И) 3(5)) G 11 G 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3511786/18-24 (22) 16. 11.82 (46) 23 ° 04.84. Бюл. ))- 15 (72) M.È. Стальная и Л.П.Лабузова (7i) Алтайский политехнический институт им. И.И. Ползунова (53) 861.327.66(088.8) (56) 1. Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств, M., "Советское радио", 1975, с. 139, рис. 4. 10.

2. Авторское свидетельство СССР

)) 855732, кл. G 11 G 19/00, 1979 (прототип) ° (54)(57) РАСПРЕДЕЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее ячейки памяти, каждая из которых состоит из,элементов И и

ИЛИ, причем выход элемента И каждой ячейки памяти соединен с первым вхо" дом элемента ИЛИ данной ячейки памяти и является выходом распределительного устройства, выход элемента ИЛИ каждой ячейки памяти соединен с первым. входом элемента И данной ячейки памяти,и формирователЬ тактовыхимпульсов, содержащий Т-триггер и элемент

НЕ, отличающийся тем, что, с целью упрощения устройства, второй вход элемен)а И каждой ячейки памяти, кроме первой, соединен с выходом элемента И предыдущей ячейки памяти, а второй вход элемента И первой ячейки памяти является управляющим входом распределительного устройства, прямой и инверсный выходы Т-триггера соединены с вторыми входами элементов ИЛИ нечетных и четных ячеек памяти соответственно, Т-вход Т-триггера подключен к выходу элемента НЕ, вход которого является тактовым входом распределительного устройства, а R-вход Т-триггера подключен к управляющему входу распределительного устройства.

1 10880

Изобретение относится к вычислительной технике может быть использовано как устро"ство управления станками, технологическими процессами и т.п., если ребуется выполнить ряд последовател ных действий, которые завершаются одновременно.

Известен однофазный двухтактный регистр сдвига, содержащий разрядные.ячейки, кажд я из которых состо- 10 ит из двухвходов п элементов И с инвертором на перв м входе, соединенных последовательно с элементом ИЛИ(1).

Этот регистр сдвига может быть использован в каЧестве распредели- 15 тельного устройства.

Недостатком такого регистра сдвига является сложность схемного выполнения.

Наиболее близким по технической 20 сущности к предложенному является регистр сдвига, содержащий ячейки памяти, каждая и которых состоит из последовательно соединенных элементов ИИИ и И, $ Формироветель тектовых импульсов, входы которого соединены с тактовой шиной и шиной сброса, при этом вых д элемента И каждой ячейки памяти со динен с входом элемента ИЛИ данной и последующей ячеек

30 памяти и являетс выходом регистра, вход элемента ИЛИ первой ячейки является входом реги тра, входы элементов И четных и н четных ячеек соеди1 нены с первым и вторым выходами формирователя тактовых импульсов соответственно (.")

Недостатками известного .регистра сдвига при его и пользовании в качестве распределительного устройства для выполнения функций управления являются сложность схемного выполнения формирователя тактовых импульсов, и то, что в 1ходной сигнал каж,дой ячейки (памяти является импульсным сигналом и не может сохраняться в течение всего интервала времени деиствия входног .сигнала.

Целью изобрет ния является упрощение устройства

Поставленная ель достигается тем, что в распр делительном устройстве (регистре с вига), содержащем ячейки памяти, к ждая из которых состоит из элементов И и ИЛИ, причем выход элемен а И каждой ячейки памяти соединен с первым входом элемента ИЛИ данной ячейки памяти и является выходом распределительного (50

74 з устройства, выход элемента ИЛИ каждой ячейки памяти соединен с первым, входом элемента И данной ячейки па мяти, и формирователь тактовых импульсов, содержащий Т-триггер и элемент НЕ, второй вход элемента И каждой ячейки памяти, кроме первой, соединен с выходом элемента И предыдущей ячейки памяти, а второй вход элемента И первой ячейки памяти является управляющим входом распределительного устройства, прямой и инверсный выходы Т-триггера соединены со вторыми входами элементов

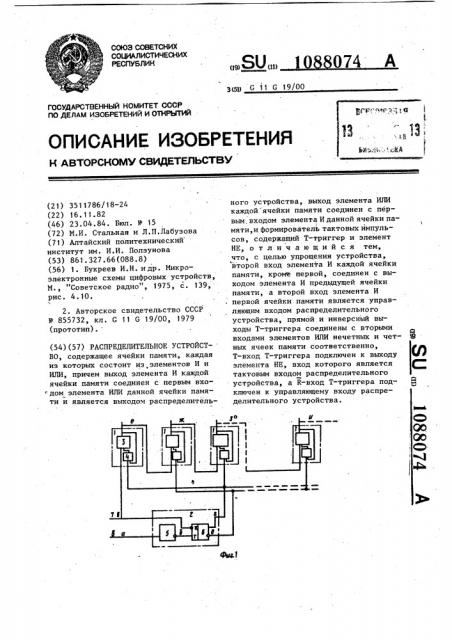

ИЛИ нечетных и четных ячеек памяти соответственно, Т-вход Т-триггера подключен к выходу элемента НЕ, вход которого является тактоьым. входом распределительного устройства, 4» а К-вход Т-триггера подключен к управляющему входу распределительного устройства, На фиг. 1 представлена функциональная схема предложенного рас- пределительного устройства; на фиг. 2 — временная диаграмма, поясняющая его работу.

Распределительное устройство содержит ячейки 1 памяти и формирова-! тель 2 тактовых импульсов. Ячейки памяти состоят из элементов И 3 и

ИЛИ 4, а формирователь тактовых импульсов — из элемента НЕ 5 Т-триггера б. Выход элемента И 3 каждой ячейки памяти 1 соединен с первым входом элемента ИЛИ 4 данной ячейки памяти, со вторым входом элемента И 3 последующей ячейки памяти и является выходом распределительного устройтсва. Второй вход элемента

И 3 первой ячейки памяти является управляющим входом 7 распределитель-. ного устройства, Выход элемента

ИЛИ 4 каждой ячейки памяти соединен с первым входом элемента И 3 данной ячейки памяти. Вторые входы элементов ИЛИ 4 нечетных и четных ячеек памяти соединены с прямым и инверсным выходами Т-триггера 6. Вход элемента НЕ 5 является тактовым входом

8 распределительного устройства, а выход элемента HE 5 соединен с Т-входом Т-триггера 6, R-вход которого подключен к управляющему входу 7 распределительного устройства.

Распределительное устройство работает следующим образом.

В исходном состоянии, т.е. до поступления на управляющий вход 7

1088074 4 пает на второй, вход элемента И 3 третьей ячейки 1 памяти. В момент времени t4 происходит переключение

Т-триггера 6, в результате чего срабатывает третья ячейка 1 памяти !

И ТеДе

Таким образом, на выходе каждой последующей ячейки 1 памяти выходной сигнал появляется с задержкой на один такт и сохраняется до окончания действия сигнала на управляющем . входе 7. В момент t+, когда единичный сигнал снимается с управляющего входа 7, Т-триггер..6 и ячейки 1 памяти возвращаются в исходное состояние.

3 единичного сигнала (фиг. 2в) на прямом выходе Т-триггера 6 и на выходах ячеек 1 памяти присутствует нулевой сигнал (фиг. 2, r, е, ж, з, и). При поступлении в момент t< на управляющий вход 7 и на К-вход

Т-триггера единичного сигнала, Т-триггер подготавливается к переключению тактовыми импульсами, поступающими на тактовый вход 8 (фиг. 2Й). Переключение Т-триггера начинается в момент спада очередного тактового импульсоа (момент t, фиг. 2). Практически одновременно с этим появляется сигнал на выходе первой ячейки 1 памяти (фиг. 2, е), который за счет обратной связи через элемент ИЛИ 4 будет сохраняться до конца действия сигнала на управляющем входе. Этот сигнал поступает на второй вход элемента И 3 второй ячейки памяти. Однако сраба.тывание этой ячейки памяти произойдет только в момент t, т.е. после переключения Т-триггера 6 и появления единичного сигнала на втором . входе элемента HJIH 4. и на первом входе элемента И 3 второй ячейки 1 памяти. Единичный сигнал с выхода элемента И 3 второй ячейки посту-

Заказ 2682/50 .

Подписное

ВНИИПИ

Тираж 575

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Технико-зкономические преимущества предложенного устройства по срав2п нению с известным состоят в более простой реализации формирователя тактовых импульсов, который содержит только два элемента, а в известном устройстве — 10 элементов.

Кроме того, в предложенном распределительном устройстве выходные сигналы ячеек памяти сохраняются до окончания действия сигнала на управляющем входе распределительного устройства.