Цифровой фильтр с ограниченной производной

Иллюстрации

Показать всеРеферат

ЦИФРОВОЙ ФИЛЬТР С ОГРШ1ЧЕИЙ00 ПРОИЗВОДНОЙ содержащий регистр , икформаШ1ояыый вход которого является ияформационнш4 входом фильтра , первый сумматор, о л и ч а ющ и и с я тем, что, с целью повышения точности фильтрации, в Него введены второй, третий и четвертый су й4аторы, первый и второй пороговые блоки, элемент ИЛИ, элемент НЕ и коммутатор, выход которого является информационньн выходом фильтра, информах онный выход регистра подключен к первым входам первого и второго сумматоров, выходы которых подключены соответственно к первому и второму информацнонньм входам коммутатора и соединены с первыми входами соответственно третьего и четвертого сумматоров , выходы которых подключены к входам соответственно первого и второго пороговых блоков, вьподы которых соединены соответственно с первым и вторым входами элемента ЩШ, .выход которого подключен к входу элемента НЕ, вторые входы первого if . второго сумматоров объединены и являются входом эадания параметра фильтi ра, третий информационный вход коммутатора и вторые входы третьего и четвертого с 4маторов объединены и oбpaзyюt информационный вход фильтра, выход эла4ента НЕ и выходы первого и второго пороговых блоков соединены соответственно с раэрядами управляющего взвода коммутатора. .

СОЮЗ СОВЕТСКИХ

ШИ Л

PECflV5ËÈÍ (l% а1i д, ф, 1 4s

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, Н АВТОРСНОМУ СИИДВТВЗЬСТВУ

ГОСУД СТВЕННЫЙ ЙОМИ1 ЕТ СССР

П0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3553832/18-24 (22) 15.02.83 (46) 23.04.84. Вол. М» 15 (72) А.Е.Грицкевич и С.И.Лычагин (53) 681.32(088.8) (56) !. Авторское свидетельство СССР

В 734711, кл. 5j 06 F 15(34, 1978.

2. Гольденберг Л.М, Левчук Ю.П., Поляк M.È. Цифровые фильтры. М., "Связь", -1974, с. 16 (прототип). (54)(57) ЦИЕРОВой ЭИПЬтР С ОГРАНИЧЕННОЙ ПРОИЗВОДНОЙ, содериащий регистр, информационный вход которого. является информационным входом фильтра, первый сумматор, о т л и ч а— ю шийся тем, что, с целью повышения точности фильтрации, в него введены второй, третий и четвертый сумматоры, первый и второй пороговые: блоки, элемент ИЛИ, элемент НЕ и коммутатор, выход которого является . информационным выходом фильтра, ин- формационный выход регистра подклю/ чен к первым входам первого и второго сумматоров, -выходы которых подключе ны соответственно к первому и второму информационньж входам коммутатора и соединены с первыми входами соответственно третьего и четвертого сумматоров, выходы которых подключены к входам соответственно первого и второго пороговых блоков, выходы которых соединены соответственно с первым и вторым входами элемента ИДИ, .выход которого подключен к входу элемента НЕ, вторые входы первого и; второго сумматоров объединены и являются входом задания параметра фильтра, третий информационный вход ком- Я мутатора н вторые входы третьего и четвертого сумматоров объединены и образуют информационный вход фильтра, выход элемента НЕ и выходы первого и второго пороговых блоков соединены соответственно с разрядами управляющего входа коммутатора.

1088100

Изобретение относится к преобразованию в цифровых системах автоматического управления и может быть использовано для подавления аддитивных помех, характеризующихся боль- 5 шой амплитудой и спектром частот, близким к спектру полезного сигнала.

Известен цифровой фильтр, содержащий регистры, блок памяти, умножители и сумматор (1).

Недостатком этого фильтра является вносимый ими фазовый сдвиг и ослабление входного сигнала в области полезных частот.

Наиболее близким к изобретению по технической сущности является фильтр, содержащий регистры, устройства умножения и сумматор, причем выходы регистров соединены с входами соответствующих умножителей, выходы которых подключены к входу сумматора(2).

Недостатком известного фильтра является искажение амплитудно-фазовой характеристики полезного сигнала.

Целью изобретения является порыt шение точности фильтрации, т.е. улучшение амплитудно-фазовой характеристики фильтра в области полезных частот.

Поставленная цель достигается тем, что в цифровой фильтр с ограниченной производной, содержащий регистр, информационный вход которого является информационным входом фильтра, первый сумматор, введены второй, третий и четвертый сумматоры, первый и второй пороговые блоки, элемент

ИЛИ, элемент НЕ и коммутатор, выход

40 которого является информационным вы-. ходом фильтра, информационный выход регистра подключен к первым входам первого и Второго сумматоров, выходы которых подключены соответственно к

45 первому и второму информационным входам коммутатора и соединены с первыми входами соответственно третьего и четвертого сумматоров, выходы которых подключены к входам соответСТвенно первого и второго пороговых

50 блоков, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого подключен к входу элемента НЕ, вторые входы первого и второго сумматоров

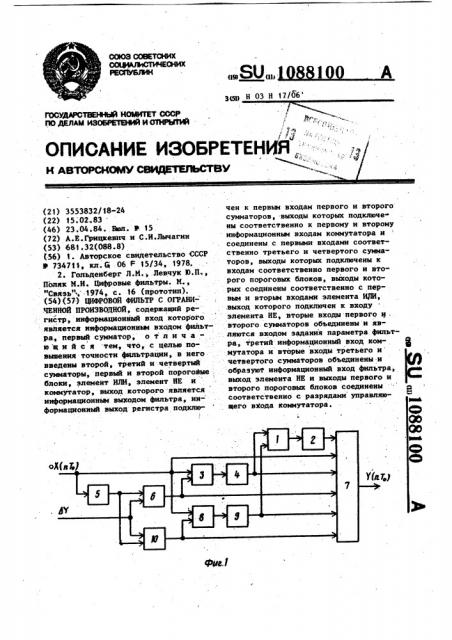

55 объедйнены и являются входами зада.ния параметра фильтра, третий информационный вход коммутатора и вторы входы третьего и четвертого сумматоРов объединены и образуют информационный вход фильтра, выход элемента НЕ и выходы первого и второго пороговых блоков соединены соответственно с разрядами управляющего ввода коммутатора, На фиг. 1 представлена функциональная схема цифрового фильтра; на фиг. 2 — амплитудно-частотные и фазочастотные характеристики фильтра.

Цифровой фильтр содержит элемент

ИЛИ 1, элемент НЕ 2, сумматор 3, пороговый блок 4, регистр 5, сумматор 6, коммутатор. 7, сумматор 8, пороговый блок 9 и сумматор 10.

На фиг. 2 показаны частотные ам- * плитудные и фазовые характеристики; предлагаемого фильтра (сплошной линией) и известного (пунктирной линией) с учетом того, что частота квантования Шо =- 1/2 Т- значительно превышает спектр полезного сигнала и шумов, а параметры известного фильтра выбраны так, чтобы максимально подавить помеху и внести минимальные искажения в полезный сигнал.

На входы регистра 5, сумматора 8 и коммутатора 7 поступает входной сигнал Х (8 Т0), на входы сумматоров

6 и 10 поступает сигнал ЬУ, соответствующий максимально возможной производной выходного сигнала, выход регистра 5 соединен с входами сумматоров 6 и 10, выходы которых соединены с входом коммутатора 7 и входами сумматоров 3 и 8 соответственно, выход сумматора 3 соединен с входом порогового блока 4, а выход сумматора 8 — с входом порогового блока

9, выходы пороговых блоков 4 и 9 соединены с входами коммутатора 7 и элемента ИЛИ 1, выход которого соединен с входом элемента 2, выход которого соединен.с входом коммутатора 7„ с выхода коммутатора 7 снимается выходной сигнал У (П Т0).

Цифровой фильтр работает следующим образом.

Входной сигнал Х (eT+) поступает на вход коммутатора 7 и на вход регистра 5, где запоминается на время такта квантования. Т0 с выхода регистра 5 сигнал, равный входному сигналу на предыдущем такте квантования, поступает на первые. входы сумматора 6 и сумматора 10, на вторые входы которых поступает сигнал .dD

1088100

ВНИИПИ Заквз 2687/51 Т ш 862 lip сное

Фвииаи ППП Потеет", г. Увгоров,ув.Проехтвы, 4 причем второй вход четвертого сумматора 10 является вычитающим. С выхода сумматора 6 сигнал, равный максимально возможному выходному сигналу в данном такте, поступает на вход коммутатор," 7 и на второй вход сумматора 3, на первый вход которого поступает входной сигнал Х(пТ ).

О. первый вход сумматора 3 является зычитающим. Выходной сигнал сумматора 10, равный минимально возможному выходному сигналу в данном такте, поступает на вход коммутатора 7 и на первый вход сумматора 8, на второй вычитающий вход которого посту- 1 пает входной сигнал х(пТо). С выхода сумматора 3 сигнал, равный превыще-. нию входного сигнала над максимально возможным, поступает на вход порогового блока 4, с выхода которого О сигнал поступает на вход коммутато- ра 7 и на вход элемента ИЛИ 1. С выхода сумматора 8 сигнал, равный разнице между минимально возможным и входным сигналами, подается на вход порогового блока 9, с выхода которого сигнал поступает на вход коммутатора 7 и на вход эдемента ИЛИ 1, Первый 4 и второй 9 пороговые блоки формируют выходной логический сигнал при переходе сигнала на входе от отрицательного к попожительному значению. Сигнал с выхода элемента

ИЛИ 1 поступает на вход эдемента

НЕ 2, выход которого поступает на вход коммутатора 7.

Введение в предлагаемое устройство сумматоров, пороговых блоков, логического элемента ИЛИ, элемента

НЕ и коммутатора позволяет подавлять аддитивные помехи со спектром частот, близким к частотам полезного сигнала, без искажения амплитуды и формы последующего.