Цифровой умножитель частоты

Иллюстрации

Показать всеРеферат

и11ФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОТЫ , содержащий последовательно соединенные первый счетчик импульсов, первый буферный каскад, первый счетчик обратного счета, выход которого соединен с выходной шиной умножителя и с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом формирователя им- . пульсов, вход которого подключен к входной шине умножителя с входом элемента задержки и входом записи первого буферного каскада, а выход с входом записи первого летчика об-, ратного счета, последовательно соединенные второй счетчик импульсов, второй буферный каскад и второй счетчик обратного счета, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом формирователя импульсов и входом записи второго буферного каскада, а выход - с входом записи второго счетчика обратного счета, выход элемента задержки подключен к входам установки второго счетчика импульсов и первого делителя частоты, счетный вход которого соединен с выходом генератора тактовых импульсов, а первый выходсо .счетным входом первого счетчика импульсов, отличающийся тем, что, с целью повышения точности умножения, в него ведены инвертор, первый и второй элементы И, триггер , второй делитель частоты, третий счетчик обратного счета и элемент сравнения кодов, вход установки которого соединен с выходом формиро- . вателя импульсов, входом запуска триггера и входом записи третьего счетчика обратного счета, информационный вход которого соединен с первым информапионным выходом первого делителя частоты, счетный вход - с выходом инвертора, вход которого подключен к выходу второго счетчика § обратного счета, и с первым входом (Л первого элемента И, выход которого соединен со счетным входом первого счетчика обратного счета, а второй вход - с выходом генератора тактовых импульсов, счетным входом второго делителя частоты и первым входом второго элемента И, выход которого динен со счетным входом второго счет-, чика обратного счета, второй вход сх .с выходом триггера,, вход сброса ко00 торого соединен с выходом третьего счетчика обратного счета, причем шина установки коэффициента деления соединена с кодовыми входами первого делителя частоты и .элемента сравнения кодов, информационный вход которого соединен с вторым информационным выходом первого дели.теля часто-, . ты, информационный выход - с информационным входом второго делителя частоты, выход которого соединен со счетным входом второго счетчика импульсов , а вход установки - с выходом элемента задержки.

СОЮЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИН.(19) (И) 3(59 Н 03 К 5 156

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3561907/18-21 (.22 1 30. 12. 82 (46) 23. 04.84. Бюл. )) 15 (72) В.И,.Болдин (53) 621 ° 374(088.8) (56) 1. Авторское свидетельство СССР

)) 799146, кл. Н 03 К 23/00, Н 03 В

Н 03 В 19/00, 04.04.79.

2. Авторское свидетельство СССР

)) 843201, кл. Н 03 К 5/01, 04.04.79 (прототип). (54 ) (57 ) ЦИФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОТЫ, содержащий последовательно соединенные первый счетчик импульсов, первый буферный каскад, первый счетчик обратного счета, выход которого соединен с выходной шиной умножителя и с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом формирователя импульсов, вход которого подключен к входной шине умножителя с входом элемента задержки и входом записи первого буферного каскада, а выходс входом записи первого о(етчика обратного счета, последовательно соединенные второй счетчик импульсов, второй буферный каскад и второй счетчик обратного счета, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом формирователя импульсов и входом записи второго буферного каскада, а выход — с входом записи второго счетчика обратного счета, выход элемента задержки подключен к входам установки второго счетчика импульсов и первого делителя частоты, счетный вход которого соединен с выходом генератора тактовых импульсов, а первый выход °со.счетным входом первого счетчика импульсов, отличающийся .тем, что, с целью повышения точности умножения, в него ведены инвертор, первый и второй элементы И, триггер, второй делитель частоты, третий счетчик обратного счета и элемент сравнения кодов, вход установки которого соединен с выходом формиро- . вателя импульсов, входом запуска триггера и входом записи третьего счетчика обратного счета, информационный вход которого соединен с первым информационным выходом первого делителя частоты, счетный вход - с выходом инвертора, вход которого подключен к выходу второго счетчика е обратного счета, и с первым входом первого элемента И, выход которого фф соединен со счетным входом первого счетчика обратного счета, а второй вход — с выходом генератора тактовых! импульсов, счетным входом второго а делителя частоты и йервым входом вто= рого элемента И, выход которого: сое- динен со счетным входом второго счет-(( чика обратного счета, второй вход— с выходом триггера, вход сброса ко- Ф торого соединен с выходом третьего QQ счетчика обратного счета, причем шина установки коэффициента деления соединена с кодовыми входами первого () делителя частоты и элемента сравнения кодов, информационный вход которого соединен с вторым информацион ным выходом первого делителя часто-, ты, информационный выход - с информационным. входом второго делителя частоты, выход которого соединен со,Ф счетным входом второго счетчика импульсов, а вход установки - с выходом элемента задержки.

1088107

Изобретение относится к иьачульсной технике и может быть использовано в измерительных устройствах, например, при измерении частоты, фазы

Формч низкочастотных периодических сигналов. 5

Известен цифровой умножитель частоты, содержащий последовательно соедйненные счетчик импульсов, буферный каскад и счетчик обратного счета, выход которого соединен с нервым ,входом первого .элемента ИЛИ, выход которого соединен с входом записи счетчика обратного счета, а второй вход — с входом записи буферного каскада, первым входом второго элемента ИЛИ, выходом формирователя им- 15 пульсов и входом элемента задержки, выход которого соединен с входом устаустановки счетчика импульсов, счетный вход которого соединен с выходом второго элемента ИЛИ, второй вход:i 0 которого через последовательно соединенные формирователь прямоугольных импульсов и делитель частоты соединен с выходом генератора тактовых импульсов и счетным входом счетчика 25 обфктного счета (1 .

Недостатком этого устройства является низкая точность умножения, проявляющаяся в нарушении периодичности выходного сигнала. 30

Наиболее близким по технической сущности и достигаемому результату к изобретению является цифровой умножителb частоты, содержащий последовательно соединенные первый счетчик импульсов, первый буферный каскад, первый счетчик обратного счета, выход которого соединен с выходной .шиной умножителя и с первым входом первого элемента ИЛИ, второй вход 40 которого соединен с выходом формирователя импульсов, вход которого подключен к входной шине умножителя, с входом элемента задержки и входом записи первого буферного каскада, а выход - с входом записи первого счетЧика обратного счета, последовательно соединенные второй счетчик импульсов, второй буферный каскад и второй счетчик обратного счета, выход ,которого подключен к первому- входу второго элемента ИЛИ, второй вход которого соединен с выходам формиро вателя импульсов и входом записи второго буферного каскада, а выход— с входом записи второго счетчика обратного счета, выход элемента задержки подключен к входам установки первого и второго счетчиков импульсов, счетный вход первого делителя частоты соединен с выходом генерато- 60 ра тактовых импульсов, первый выход - со счетным входом первого счетчика импульсов, а второй выход — со счетным входом второго счетчика импульсов,выход второго счетчика обратного счета соединен с третьим входом, первого элемента ИЛИ Г22.

Недостатком известного устройства является недостаточная точность умножения, проявляющаяся в нарушении периодичности выходного сигнала при больших значениях коэфФициента умножения.

Цель изобретения - повышение точности умножения, поставленная цель достигается тем, что в цифровой умножитель частоты, содержащий последовательно соединенные первый счетчик импульсов, первый буферный каскад, первый счетчик обратного счета, выход которого соединен с выходной шиной умножителя и с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом формирователя импульсов, вход которого подключен к входной шине умножителя, с входом элемента задержки и входом записи первого буферного каскада, а выходс входом записи первого счетчика обратного счета, последовательно соединейные второй счетчик импульсов, второй буферный каскад и второй счетчик обратного счета, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом формирователя импульсов и входом записи второго буферного каскада, а выход. - с входом записи второго счетчика об ратного счета, выход элемента задержки подключен к входам установки второго счетчика, импульсов и первого делителя частоты, счетный вход которого соединен с выходом генератора тактовых импульсов, а первый выходсо счетным входом первого счетчика ймпульсов, введены инвертор, первый и второй элементы И, триггер,- второй делитель частоты, третий счетчик обратного счета и элемент сравнения кодов, вход установкй которого соединен с выходом формирователя импульсов, входом запуска триггера и входом записи третьего счетчика обрат», ного счета,. информационный вход которого соединен с первым информационным выходом первого делителя частоты, счетный вход - с выходом инвертора,, вход которого подключен к выходу второго счетчика обратного счета, и с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика обратного счета, а второй вход - с выходом генератора тактовых импульсов, счетным входом второго делителя частоты и первым входом второго элемента P., выход которого соединен со счетным входом второго счетчика. обратного счета, второй вход — с выходом триггера, вход сброса кото1.ого соединен с выходом третьего счетчика обратного счета, причем

1088107

15

20 прямоугольные импульсы,.период повторения которых равен периоду входного сигнала Т „. Эти импульсы поступают на вход элемента 8, на входы

25 записи буферных каскадов 2 и 10, счетчика 19, установочные входы делителей 13 и 18 и элемента 21, а также на вход запуска триггера 17. На счетный вход счетчика 1 поступают импульсы с выхода делителя 13 с часторой й„= /k, на счетный вход счетчика 9 йоступают импульсы с выхода делителя 18 с частотой Г = Г. /k k/ï, где к - коэффициент деления делите ля 13 или коэффициент умножения устройства, — = 1,2,3,... — коэффициk ент увеличения частоты делителя 18 по сравнению с делителем 13,fT частота повторения импульсов генератора 14; n - остаточное число импульсов в конце периода входного сигнала в делителе .13.

Эа период входного сигнала Тв„в счетчике 1 поступает число импульсов„ равное N„ = Г,./k - Т®,, а в

Чнк 9 -:N2 = f>/k- k/n Твк

8 конце периода входного сигнала импульсом с выхода формирователя 6 эти числа перезаписываются соответственно в буферный каскад 2, счетчик

3 и в буферный каскад 10 и счетчик

11. На счетные входы счетчиков 3 и

11 поступают импульсы с частотой с выхода генератора 14.

В результате этого чиолр N считывается со счетчика 3 после герезаписи через промежуток времени, равный ТЗ,К =Т „/k а счетчика 11 через промежуток времени,,равный Т,„: = /k

На выходах счетчиков 3 и 11 через промежутки времени, равные соответственно Т,,к„и Т к,образуются импульсы, которые через элементы 5 и 1" поступают на входы записи счетчиков 3 и 11 соответственно, благодаря чему, 35

45 вход которого соединен с первым информационным выходом первого делите- . ля 13 частоты, счетный вход — с выхо-5 дом инвертора 20, вход которого подключен к выходу второго .счетчика 11 обратного счета и с первым входом.. первого элемента q5 И, выход которого

60 второго делителя 18 частоты и первым входом второго элемента 16 И, выход 65 шина установки коэффициента деления соединена с кодовыми входами первого делителя частоты и элемента срав.нения кодов, информационный вход которого соединен с вторым информационным выходом первого делителя частоты, информационный выход — с инФормационным входом второго делителя частоты, выход которого соединен со счетным входом второго счет.чика импульсов, а вход установкис выходом элемента задержки.

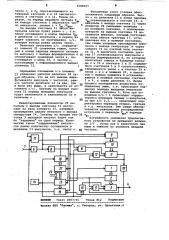

На чертеже представлена структурная электрическая схема устройства.

Цифровой умножитель частоты содержит последовательно соединенные первый счетчик 1 импульсов, первый буферный каскад 2, первый счетчик 3 обратного счета. выход которого соединен с выходной шиной 4 умножителя и с первым входом первого элемента 5 ИЛИ, второй вход которого соединен с выходом формирователя 6 импульсов, вход которого. подключен к входной шине 7 умножителя, с входом. элемента 8 задержки.и входом записи первого буферного каскада 2, а выход - с входом записи первого счетчика 3 обратного счета, последовательно соединенные второй счетчик 9 импульсов, второй буферный каскад 10 и второй счетчик 11 обратного счета, .выход которого подключен к первому входу второго элемента 12 ИЛИ, второй вход которого соединен с выходом формирователя 6 импульсов и входом записи второго буферного каскада

10, а выход — с входом записи второго счетчика 11 обратного счета, выход элемента 8 задержки подключен к входам установки второго счетчика 9 импульсов и первого делителя 13 часто.ты,-счетный вход которого соединен с выходом генератора 14 тактовых импульсов, а первый выход — со счетным входом первого счетчика 1 импульсов, .первый 15 и второй 16 элементы И, триггер 17, второй делитель 18 частоты, третий счетчик 19 обратного счета, инвертор 20 и элемент 21 сравнения, кодов, вход установки которого соединен с выходом Формирователя 6 импульсов, входом запуска. триггера

17 и входом записи третьего счетчика 19 обратного счета, информационный соединен со счетным входом первого счетчика 3 обратного счета, а второй вход — с выходом генератора 14 тактовых импульсов, счетным входом которого соединен со счетным входом второго счетчика 11 обратного счета, второй вход — с выходом триггера 17, вход сброса которого соединен с выходом третьего счетчика 19 обратного счета, причем шина 22 установки коэффициента деления соединена с кодовыми входами первого делителя 13 частоты и элемента 21 сравнения кодов, информационный вход которого соединен с вторым информагионным выходом первого делителя.13 частоты, информационный выход - с информационным входом второго делителя 18 частоты, выход которого соединен со счетным входом второго счетчика 9 импульсов, а вход установки — с выходом элемента 8 задержки.

Нифровой умножитель частоты работает следулцим образом.

Формирователь 6 из входного .периодического сигнала формирует короткие. 1088107 зр

ВНИИПИ Заказ 2687/51 Тираж 862 Подписное

««««« «««««

Филиал ППП Патент", г. Ужгород, ул. Проектная,4 числа Л„и N> перез апнеыеаются из. буферных каскадов 2 и 10 сеответственно в счетчики 3 и 11, Таким образом, за период входного сигнала Т на выходе счетчика 3 образуется чисзк ло импульсов, равное k = Т /Т вх

На выходе счетчика 11 число импульсов всегда будет равно и, т.е. числу оставшихся в конпе периода Т в делителе 13 импульсов, а период йх будет зависеть от соотношения k/n, 10 которое всегда равно. целому числу.

Величину отношения k/n определяет элемент 21 сравнения кодов, который в конце периода входного сигнала по импульсу с выхода формирователя 6 15 обеспечивает сравнение числа k, поступающего с шины 22, с числом и, поступающим с информационного выхода делителя 13. 1

Определив отношение k/п элемент управляет работой делителя 18 таким образом, что íà его выходе выра. Яктываются импульсы с частотой, равной частоте делителя 13 (в два, три .м боге раэ выше, в зависимости от отношения k/n). Поэтому на выходе счет. чика 11 период выходных импульсов будет изменяться в зависимости от в величины и

Инвертированные элементом 20 импульсы с выхода счетчика 11 поступают на вход элемента 15, запрещая прохождение одному импульсу с выхода генератора 14. Лоэтому на выходе сче-35 тчика 3 выходной импульс будет как бы "задержан" на один период. Количество таких "э.адержанных" импульсов равно количеству оставшихся в делителе 13 импульсов, т.е. числу и. 4р

Выполнение этого условия обеспечивается следующим образом. Число и из делителя 13 в конце периода

Т „переписывается в счетчик 19, и импульсы с выхода счетчика 11 через инвертор 20 уменьшают величину п до нулевого значения, с появлением которого иа выходе счетчика 19 появляется импульс, который поступает на вход сброса триггера 17, устанавливая его в нулевое состояние, тем самым запрещая прохождение импульсов с выхода генератора 14 через элемент 16 на счетный вход счетчика 11. В единичное состояние триггер 17 устанавливается импульсом с выхода Формирователя 6, по которому происходит запись в буферные каскады 2 и 10 и счетчики 3 и 11 содержимого счетчиков 1 и 9 соответственно, записывается число и в счетчик 19 и числа п и k в элемент 21, а импульсом с выхода элемента 8 устанавливаются в нулевое состояние счетчики

1 и 9, а также делитель 13. Далее процесс повторяется аналогично изложенному выше, т.е. происходит коррекция периода выходных импульсов на выходе счетчика 3. Если при отношении k/n = 1 происхбдит корректировка периодов первых п-импульсов, то при k/п 2,3,..., происходит корректировка периодов вторых, третьих и т.д. импульсов. Тем самым обеспечивается равномерное распределение импульсов с периодом Т в периоде

-ври 8õ

Погрешность умножения предлагаемого устройства не превышает величины 1/f, тогда как у известного она выше и зависит от значения входной частоты.