Дешифратор

Иллюстрации

Показать всеРеферат

1. ДЕШИФРАТОР, содержащий N входных, 2 выходных шин и управляющие шины, дешифраторные модули, объединенные в ступени, информационные входы дешифраторного модуля первой ступени соединены с входными шинами младших декодируемых разрядов, а его управляющие входы соединены с соответствующими управляющими шинами , выходы дешифраторных модулей последней ступени подключены к соответствующим выходным шинам, о т л и чающийся тем, что, с целью расширения его функциональных возможностей , первый и второй входы управления дешифраторных модулей второй ступени соединены с соответствующими управлякндими шинами, а третьи входы управления подключены к соот- . ветствующим выходам дешифраторного модуля .первой ступени, информационные входы дешифраторных модулей второй ступени соединены с входными шинами старших декодируемых разрядов, выходы дешифраторных модулей второй ступени соединены с соответствующими выходными шинами. 2. Дешифратор по п. 1, отличающийся тем, что каждый дешифратор ный модуль содержит коммути ,рующие элементы, объединенные в.ступени , единичные входы коммутирукяцих элементов первой ступени соединены соответственно с первым и вторым входами управления дешифраторного модуля , а нулевые входы подключены соответственно к второму и третьему входам управления дешифраторного модуля, причем нулевые входы первого и второго коммутирующих элементов второй ступени соединены с соответствующими выходами коммутирующих элементов первой ступени, а их единичные входы соединены с первым входом управления дешифраторного модуля, нулевые входы третьего и четвертого коммутирукицих § элементов второй ступени соединены с третьим входом управления дешифраС/ ) торного модуля, а их единичные входы подключены к соответствующим выходам коммутирующих элементов первой ступени , нулевые входы первого, второго, третьего и четвертого коммутирующих элементов третьей ступени соединены с соответствующими выходами коммутирующих элементов второй ступени, а 00 их единичные входы подключены к персх вому входу управления дешифраторного модуля, нулевые входы пятого, шестого, седьмого и восьмого коммутирующих о: элементов третьей ступени срединены с третьим входом управления дешифраторного модуля, а их единичные входы подключены к соответствующим выходам коммутирующих элементов второй ступени , выходы коммутирукмцих элементов третьей ступени соединены с соответствующими выходами дешифраторного модуля, при этом информационные входы всех коммутирующих элементов подключены к соответствующим информационным входам дешифраторного модуля.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1088116

3др Н 03 К 13/24

3 iC

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABT0PCH0MV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPHTHA (21) 3550088/18-21 (22) 24. 12, 82 (46) 23. 04. 84. Бюл. Ф 15 (72) М.С.Белков, Е.А.Братальский, В.С.Иванова и Я.И.Свирский (53) 621 .321 ° 3(088.8) (56) 1. Авторское свидетельство СССР

1Р 809565, кл. Н 03 К 13/24, 28.02.81.

2. Каган Б.М. Электронные вычислительные машины и системы. М., "Энергия". 1979, с. 191, рис. 3,26. (54) (57) 1. ДЕШИФРАТОР, содержащий

1ч входных, 2 выходных шин и управляМ ющие шины, дешифраторные модули, объединенные в ступени, информационные входы дешифраторного модуля первой ступени соединены с входными шинами младших декодируемых разрядов, а его управляющие входы соединены с соответствующими управляющими шинами, выходы дешифраторных модулей последней ступени подключены к соответствующим выходным шинам, о т л ич а ю шийся тем, что, с целью расширения его функциональных возможностей, первый и второй входы управления дешифраторных модулей второй ступени соединены с соответствующими управляющими шинами, а третьи входы управления подключены к соот- . .ветствующим выходам дешифраторного модуля первой ступени, информационные входы дешифраторных модулей второй ступени соединены с входными шинами старших декодируемых разрядов, выходы дешифраторных модулей второй ступени соединены с соответствующими выходными шинами.

2. Дешифратор по п. 1, о т л и— ч а ю шийся тем, что каждый дешифраторный модуль содержит коммути, рующие элементы, объединенные в. сту пени, единичные входы коммутирующих элементов первой ступени соединены соответственно с первым и вторым входами управления дешифраторного модуля, а нулевые входы подключены соответственно к второму и третьему входам управления дешифраторного модуля, причем нулевые входы первого и второго коммутирующих элементов второй ступени соединены с соответствующими выходами коммутирующих элементов первой ступени, а их единичные входы соединены с первым входом управления дешифраторного модуля, нулевые входы третьего и четвертого коммутирующих элементов второй ступени соединены @ с третьим входом управления дешифраторного модуля, а их единичные входы подключены к соответствующим выходам коммутирующих элементов первой ступени, нулевые входы первого, второго, Я третьего и четвертого коммутирующих элементов третьей ступени соединены с соответствующими выходами коммутирующих элементов второй ступени, а их единичные входы подключены к первому входу управления дешифраторного модуля, нулевые входы пятого, шестого, седьмого и восьмого коммутирующих элементов третьей ступени соединены с третьим входом управления дешифраторного модуля, а их единичные входы подключены к соответствующим выходам коммутирующих элементов второй ступени, выходы коммутирующих элементов третьей ступени соединены с соответствующими выходами дешифраторного модуля, при этом информационные входы всех коммутирующих элементов подключены к соответствующим информационным входам дешифраторного модуля.

1088116

Изобретение относится к вычислительной технике и может быть использовано в различных узлах управления.

Известен дешифратор, содержащий логические элементы, именнций Р вход- 5 ных и 2 выходных шин Г! 3.

Недостаток данного дешифратора— ограниченные функциональные возможности.

Наиболее близким к преплагаемому 10 техническим решением является дешифратор, содержащий М входных, 2 1 выходных и управляющие шины, дешифраторные модули, объединенные в ступени, информационные входы дешифратор- 15 ного модуля первой ступени соединены с входными шинами младших декодируемых разрядов,. а его управляющие входы соединены с соответствующими управляющими шинами, выходы дешифраторных 20 модулей последней ступени подключены к соответствующим выходным шинам 12 ).

Недоетатком известного устройства являются ограниченные функциональные возможности, а именно невозможность формирования логических функций прямой и инверсной маски и инверсного дешифрирования.

Целью изобретения является расширение функциональных возможностей 30 дешифратора.

Поставленная цель достигается тем, что в дешифраторе; содержащем

И входных, 2 выходных и управляю.К щие шины, дешифраторные модули, объединенные в ступени, информационные

Входы дешифраторного модуля первой ступени соединены с входными шинами младших декодируемых разрядов, а его управляющие входы соединены с соответствующими управляющими шиками, выходы дешифраторных модулей последней ступени подключены к соответствующим ВыхОдным шинам первый и ВторОй 4 входы управления дешифраторных модулей второй ступени соединены с соответствующими управляющими шинами, а третьи входы управления подключены к соответствующим выходам дешифраторного модуля первой ступени, информа- .

50 ционные входы дешифраторных модулей второй ступени соединены с входными шинами старших декодируемых разрядов, выходы дешифраторных модулей второй ступени соединены с соответствующими выходными шинами.

Каждый дешифраторный модуль содержит коммугнрукяцие элементы, объединенные в ступени, единичные входы коммутирующих элементов первой ступени соединены соответственно с первым и вторым входами управления дешифраторного модуля, а нулевые входы подключены соответственно к второму и третьему входам управления дешифраторного модуля, причем нулевые входы первого и второго коммутирующих элементов второй ступени соединены с соответствующими Выходами коммутирующих элементов первой ступени, а их единичные входы соединены с первым входом управления дешифраторного модуля, нулевые входы третьего и четвертого коммутирующих элементов второй ступени соединены с третьим входом управления дешифраторного модуля, а их единичные входы подключены к соответствующим выходам коммутирующих элементов первой ступени, нулевые входы первого, второго, третьего и четвертого коммутирующих элементов третьей ступени соединены с соответствующими.выходами коммутирукнцих элементов второй ступени, а их единичные входы подключены к первому входу управления дешифраторного модуля, нулевые входы пятого, шестого, седьмого и восьмого коммутирующих элементов третьей ступени соединены с третьим входом управления дешифраторкого модуля, а их единичные входы подключены к соответствующим выходам коммутирующих элементов второй ступени, выходы коммутирующих элементов третьей ступени соединены с соответствующими выходами дешифраторного модуля, при этом информационные входы всех коммутирующих элементов подключены к соответствующим информационным входам дешифраторного модуля.

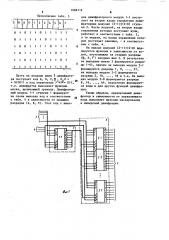

На фиг. 1 представлена структурная схема дешифратора, например для У 6; на фиг. 2 — принципиальная электрическая схема дешифраторного модуля.

Дешифратор содержит ступени 1 и 2 дешифрации, содержащие дешифраторные модули 1-1 и (2"1)т(2-8), подключенные к выходным шинам 3 декодируемых разрядов и управляющим шинам 4 и выходные шины 5, а каждый дешифраторный модуль 1-1, (2-1)-(2-8) содержит ступени 6 8 дешифрации, состоящие из коммутируынцих элементов (6-1)4(6-2); (7-1)-:(7-4) и (8-1) - - (8-8) .

Дешифратор работает следующим образом.

3 10&8116

На входные шины 3 поступает дешифрируемый код А, В, С, Q, Е, F, на управляющие шины 4 - код функции дешифрации 1 †. В соответствии с табл.1 на выходе дешифраторного моду- 5 ля 1-1 ступени 1 при этом формируются функции, которые поясняются табл. 2"5.

Таблица1

1О О О О О 1 1 1 1 1 1 1

О 0 1 О О 1 1 1 1 1 1

О 1 О О О О 1 1 1 1 1 !

0 О 1 О О О О 1 1 1 1

1 О О О О О О О 1 1 1

О О О "Все О"

Маска с исключением границы

О О t

О 1 О

Дешифратор.20 1 О 1 О .О О О О О 1

0 1 1

Маска с включением границы

1 О О

Маска инверсная с включением границы

1 1 О

"Все 1"

1 1 1

О О О 1 1 1 1 1 1 1 1

35 О О 1 О 1 1 1 1 1 1

О t О О О 1 1 1 1 t 1

О 1 1 О О О 1 1 1 1 1

1 О О О О О О 1 1 1 1 .О 1 О О О О О 1 1

45 1 1 О О О О О О О 1 1

1 t .О О О О О О О 1

Таблица

50 У +У 101 — инверсный дешифратор

О О О О 1 1 1 1 1 1

О О l 1 О 1 1 1 1 1 1

1 О 1 Дешифратор инверсный

Маска инверсная с исключением границы

Таблица2 у у 010 - дешифратор

3.О О 0 1 О 0 О О О О О

О О 1 О 1 О О О О О О

О 1 О О О 1 О О О О О

О 1 1 О О О 1 О О О 0

1 О О О О О О 1 О О О

1 О 1 О О О О 0 1 О О

1 1 О О О О О О О 1 О

1 1 t О 0 О О О О О 1

ТаблицаЭ

У УЗ001 - маска с исключением границы

1 1 0 О О О О О О О 1, 1 1 О О О О О О О 0

Таб,цидд

Y"ÔÓ50t.1 - маска с включением границы

1088116

Продолжение табл. 5

О 0 1 1 0 1 1 1 1 1

0 1 1 1 1 0 1 1 1 1 ! 0 0 1 1 1 1 0 1 1 1

0 1 1 1 1 1 0 1 1

1 1 0 1 1 1 1 1 1 0 1

1 1 1 1 1 1 1 1 1 0

Ф

Пусть на входные шины 3 дешифратора поступает код А, В, C,Q, Е 010011 и код управления У"4У 011, т.е. дешифратор выполняет функцию

I маски, включающей границу. Дешифраторный модуль 1-1 ступени 1 формирует на своих выходах код в соответствии с табл. 4 в зависимости от младших разрядов (А, В, С). Этот код с выходов дешифраторного модуля 1-1 поступает на вторые входы управления дешифраторных модулей (2-1)ф(2-8) ступени 2. Часть модулей, на вторые входы управления которых поступают нули, работает в соответствии с табл. 3, а те модули, на входы управления которых поступает единица, — в соответст-вии с табл. 4.

На выходе модулей (2-1)-;(2-8) формируются функции .в зависимости от кодов, поступающих на старшие разряды (3, Е, F) входных шин 3. В результате на выходных шинах 5 формируются разряды 1-64, причем иа выходах модуля 2-! формируются разряды 1, 9, ..., 57, на выходах модуля 2-2 формируются разряды 2, 10, ..., 58 и т.д. На выходах модуля 2-8 формируются разряды

8, 16, ..., 64. Аналогично формируются коды и для других функций дешифрации.

Таким образом, предлагаемый дешифратор в зависимости от управляющего кода выполняет функции маскирования и инверсной дешифрации.

1088116 ущщцр Заказ 2688/52 ТиРаж 862 Подписное

Филиал ППП "Патевт, г. Ужгород, ул.Проектная 4