Приемник биимпульсного сигнала

Иллюстрации

Показать всеРеферат

ПРИЕМНИК БИИМПУЛЬСНОГО СИГНАЛА , содержащий последовательно соединенные ждущий мультивибратор и первый дифференцирующий , a также второй и третий дифференцирующие блоки , первый и второй блок памяти и формирователь тактовых импульсов, выход которого является тактовым выходом приемника биимпульсного сигнала, о тличающийся тем, что, с целью повышения помехоустойчивости, в него введены последовательно соединенные первый преобразователь биимпульсного сигнала в моноимпульсный сигнал, дополнительныйждущий мультивибратор и первьй элемент ИЛИ, a также второй преобразователь биимпульсного сигнала в моноимпульсный сигнал, второй элемент ИЛИ и решающий блок, при этом первый и второй входы решающего блока подключены соответственно к выходам первого и второго блоков памяти, объединенные тактовые входы которых подключены к выходам второго элемента ИЛИ, выход первого преобразователя биимпульсного сигнала в моноимпульсный сигнал подсоединен к инфо мационному входу первого блока памяти, выход второго преобразователя бинмпульсного сигнала в. моноимпульсный сигнал - к информационному входу второго блока памяти и входу ждущего мультивибратора, выход которого подсоединен к другому входу первого элемента ИЛИ, выход которого через втог рой дифференцирующий блок подсоединен к первому входу второго элемента ШШ, второй и третий входы которого подключены соответственно к выходам первого дифференцирующего блока и третьего дифференцирующего блока, вход которого подключен к выходу дополнительного ждущего мультивибратора , a выход второго элемента ИЛИ подсоединен к входу формирователя 00 СХ) .тактовых импульсов, при этом объединенные входы первого и второго преобразователей биимпульсного сигнала в моноимпульсный сигнал являются вхо- 4; дом приемника биимпульсного сигнала, a выход решающего блока является выходом приемника биимпульсного сигналу.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

69) (И) /

ОПИСАНИЕ ИЗОБРЕТЕНИЙ 4

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3549450/18-09 (22) 07.02.83 (46) 23.04.84. Бюл. N 15 ,(72) M.À. Коломиец, Н.А. Карпович и Г.А. Шитик (53) 621.394.62(088.8) (56) 1. Авторское свидетельство СССР

Н 869072, кл. Н 04 L 1/10, 1981.

2. Авторское свидетельство СССР

Ф 497740, кл. Н 04 L 7/02, 1975 (прототип). (54) (57) ПРИЕМНИК БИИМПУЛЬСНОГО СИГНАЛА, содержащий последовательно соединенные ждущий мультивибратор и первый дифференцирующий блок, а также второй и третий дифференцирующие блоки, первый и второй блок памяти и формирователь тактовых импульсов, выход которого является тактовым выходом приемника биимпульсного сигнала, о тл и ч а ю шийся тем, что, с целью повышения помехоустойчивости, в него введены последовательно соединенные первый преобразователь биимпульсного сигнала в моноимпульсный сигнал, дополнительный ждущий мультивибратор и первый элемент ИЛИ, а также второй преобразователь биимпульсного сигнала в моноимпульсный сигнал, второй элемент ИЛИ и решающий блок, при этом первый и второй входы реша <5р Н 04 L 1/10 // Н 04 Ь 7/02 ющего блока подключены соответственно к выходам первого и второго блоков памяти, объединенные тактовые входы которых подключены к выходам второго элемента ИЛИ, выход первого преобразователя биимпульсного сигнала в моноимпульсный сигнал подсоединен к информационному входу первого блока памяти, выход второго преобразователя биимпульсного сигнала в моноимпульсный сигнал — к информационному входу второго блока памяти и входу ждущего мультивибратора, выход которого подсоединен к другому входу первого элемента ИЛИ, выход которого через второй дифференцирующий блок подсоеди- В нен к первому входу второго элемента

ИЛИ, второй и третий входы которого подключены соответственно к выходам первого дифференцирующего блока н третьего дифференцирующего блока, вход которого подключен к выходу дополнительного ждущего мультивибратора, а выход второго элемента ИЛИ подсоединен к входу формирователя ,тактовых импульсов, при этом объединенные входы первого и второго преобразователей биимпульсного сигнала в моноимпульсный сигнал являются вхо" дом приемника биимпульсного сигнала, р а выход решающего блока является выходом приемника биимпульсного сигнала, 1088144

Изобретение относится к электросвязи и может быть использовано при передаче данных.

Известен приемник биимпульсного сигнала, содержащий последовательно 5 включенные усилитель-ограничитель, преобразователь биимпульсного сигнала в телеграфный сигнал и фазовый детектор, а также блок автоподстройки разы тактовой частоты, вход и выход которого подключены соответственно к выходу преобразователя биимпульсного сигнала в телеграфный сигнал и другому входу фазового детектора Я

Наиболее близким по технической IS сущности к изобретению является приемник биимпульсного сигнала, содержащий последовательно соединенные ждущий мультивибратор и первый дифференцирующий блок,а также второй и третий 20 дифференцирующре блоки, первый и второй блоки памяти и формирователь тактовых импульсов, выход которого является тактовым выходом приемника биимпульсного сигнала, при этом первый выход ждущего мультивибратора через второй дифференцирующий блок подсоединен к входу первого блока памяти, второй выход ждущего мультивибратора через формирователь импульсов и тре- 30 тий дифференцирующий блок подсоединен к входу второго блока памяти, выход которого через блок сравнения подключен к другому входу первого бло" ка памяти, а вход первого дифферен- 35 цирующего блока объединен с другими входами второго блока памяти и блока сравнения )2j .

Недостатком известных приемников биимпульсных сигналов является низ- 40 кая помехоустойчивость при наличии стираний и вставок в канале связи.

Цель изобретения — повышение помехоустойчивости при наличии стираний и вставок в канале связи.

Для достижения поставленной цели в приемник биимпульсяого сигнала, содержащий последовательно .соединенные ждущий мультивибратор и первый дифференцирующий блок, а также второй и третий дифференцирукнцие блоки, первый .и второй блоки памяти и формирователь тактовых импульсов, выход которого является тактовым выходом приемника биимпульсного сигна- ла, введены последовательно соединенные первый преобразователь биимпульсного сигнала в моноимпульсный сигнал, дополнительный ждущий мультивибратор и первый элемент ИЛИ, а также второй преобразователь биимпульсного сигнала в моноимпульсный сигнал, второй элемент ИЛИ и решающий блок, при этом первый и второй входы решающего блока подключены соответственно к выходам первого и второго блоков памяти, объединенные тактовые входы которых подключены к выходам второго элемента

ИЛИ, выход первого преобразователя биимпульсного сигнала в моноимпульсный сигнал подсоединен к информационному входу первого блока памяти, выход второго преобразователя биимпульсного сигнала в моноимпульсный сигнал — к информационному входу второго блока памяти и входу ждущего мультивибратора, выход которого подсоединен к другому входу первого элемента ИЛИ, выход которого через второй дифференцирующий блок подсоединен к первому входу второго элемента

ИЛИ, второй и третий входы которого подключены соответственно к выходам первого дифференцирующего блока и третьего дифференцирующего блока, вход которого подключен к выходу дополнительного ждущего мультивибра= тора, а выход второго элемента ИЛИ подсоединен к входу формирователя тактовых импульсов, при этом объединенные входы первого и второго преобразователей биимпульсного сигнала в моноимпульсный сигнал являются входом приемника биимпульсного сигнала, а выход решающего блока является выходом приемника биимпульсного сигнала.

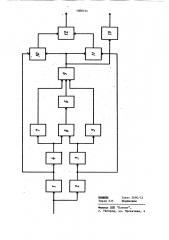

На чертеже изображена структурная электрическая схема приемника биимпульсного сигнала.

Приемник биимпульсного сигнала содержит первый и второй преобразователи I и 2 биимпульсного сигнала в монцимпульсный сигнал, ждущий мультивибратор 3, дополнительный ждущий мультивибратор 4, первый и второй дифференцирующие блоки S и 6, третий дифференцирующий блок 7, первый и второй элементы ИЛИ 8 и 9, первый и второй блоки 10 и 11 памяти, решающий блок 12 и формирователь 13 тактовых импульсов.

Приемник биимпульсного сигнала работает следующим образом.

Информация, закодированная в биимпульсный сигнал, поступает на объединенные входы первого преобразова3 10881 теля 1 н второго преобразователя 2, которые преобразуют биполярный сигнал в моноимпульсные сигналы, соот.ветствующие каждой полярности вхрд ного сигнала. Моноимпульсные сигналы 5 поступают на информационные входы первого и второго блоков 10 и 11 памяти и входы ждущего мультивибратора 3 и дополнительного ждущего мультивибратора 4. Ждущий мультивибратор 3 и дополнительный ждущий мультнвибратор 4 запускаются передним фронтом импульсов, поступающих на их входы, причем длительность формирующего ими импульса составляет 0,75 Т, где Т - 15 период следования входных импульсов.

Сигналы с выходов ждущего мультивибратора 3 и дополнительного ждущего мультивибратора 4 поступают через первый элемент ИЛИ 8 и второй днффе- 20 ренцирующий блок 6 на первый вход второго элемента ИЛИ 9, на второй и третий входы которого поступают соответственно сигналы с выходов первого дифференцирующего блока 5 и третьего дифференцирующего блока 7.

Последовательность импульсов с выхода второго элемента .ИЛИ 9 поступает на тактовые входы первого и второго блоков 10 и 11 памяти, выполненных в ви-ЗО де сдвиговых четырехразрядных регистров. Выходные сигналы разрядов первого и второго блоков 10 и 11 памяти поступают соответственно на первый

44 4 и второй входы решающего блока 12, в котором путем сравнения информации, записанной в .двух- соседних тактах; производится определение исходной информации. При этом, если сумма по модулю два бит-информации s первом и четвертом разрядах сдвиговых регистров первого 10 или второго 11 блоков памяти равна "1", то принятая информация равна "1", а в противном случае — "0". В случае стирания информации или появления новых импуль-" сов (вставок) не чаще одного искажения длительностью в половину тактового интервала на интервале в два тактовых интервала искажения входных сигналов выявляются решающим блоком 1.2.

В последнем осуществляется суммирование по модулю два содержимого сдвиговых регистров первого и .второго блоков 10 и 11 памяти. Если эта сумма равна "1", то данный канал (например, последовательно соединен ные первый преобразователь 1 и первый блок 10 памяти) принимает информацию с ошибкой и на выход решающего блока поступаеч информация со второго канала (последовательно соединены второй преобразователь 2 и второй блок

11 памяти).

Таким образом обеспечивается восста" новление исходной информации из прини- маемых сигналов при их искажении стираниями и вставками.

1088144

Заказ 2690/53

Подписное

Патент", ул. Проектная, 4