Телевизионный синхронизатор

Иллюстрации

Показать всеРеферат

1. ТЕЛЕВИЗИОННЫЙ СИНХРОНИЗАТОР , содержащий последбвательно соединенные задающий генератор и первый делитель частоты, а также второй делитель частоты, выход которого является выходом кадрового импульса , реверсивньй счетчик, формирователь сигнала отклонения, первый вход которого соединен с выходом фомирователя импульсов, вход которого является входом сигнала напряжения сети, отличающийся тем, что, с целью повышения точности синхронизации, введены компаратор и триггер, причем первый и второй входы компаратора соединены соответственно с выходами первого делителя частоты и реверсивного счетчика, а выход - с вторым входом первого делителя частоты;,с первым входом второго делителя частоты и является выходом строчного импульса; триггер включен между выходом формирователя импульсов и вторым входом второго делителя ч;1стоты, выход которого соединен с вторым входом формирователя сигнала отклонения, первый и второй выходы которого соединены с первым и вторым входами реверсивного счетчика соответственно, третий вход которого является входом сигнала установки начального коэффициента деления первого делителя частоты. 2. Синхронизатор по-п. 1, отличающийся тем, что формирователь сигнала отклонения содержит последовательно соединенные первый элемент И, первый триггер, первый элемент задержки и первый элемент запрета, выход которого является первым вьосодом формирователя сигнала отклонения, последовательно соеди (Л ненные второй элемент И, второй триггер , второй элемент задержки и второй элемент запрета, выход которого является вторым выходом формирова-теля сигнала отклонения, а также последовательно соединенные третий элемент И и одновибратор, выход коо торого соединен с вторыми входами 00 00 первого и второго элементов запрета, причем первый вход третьего элемента И соединен с вторыми входами :л первого триггера, второго элемента ю И и является вторым входом формирователя сигнала отклонения, второй вход третьего элемента И соединен с вторыми входами первого элемента И, второго триггера и является первым входом формирователя сигнала отклонения, а вторые выходы первого и второго триггеров соединены с первыми входами второго и первого эле-ментов И соответственно.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И) З(б}) Н 04 N 5/06

OllHCAHHE HSOEPETEHQ!

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3421600/18-09 (22) 12.04.82 (46) 23.04.84. Бюл. Ф 15 (72) В.А.Горных, В.Я.Зенин и В.В.Рыбченко (71) Институт технической кибернетики АН Белорусской ССР (53) 621.397(088.8) (56) 1. Авторское свидетельство СССР

У 445995, кл. Н 04 N 5/06, 1974.

2. Авторское свидетельство СССР

Ф 604 185, кл. Н 04 N 5/06, 1978 (прототип) . (54)(57) 1. ТЕЛЕВИЗИОННЪ|Й СИНХРОНИЗАТОР, содержащий последовательно соединенные задающий генератор и первый делитель частоты, а также второй делитель частоты, выход которого является выходом кадрового импульса, реверсивный счетчик, формирователь сигнала отклонения, первый вход которого соединен с выходом фомирователя импульсов, вход которого является входом сигнала напряжения сети, отличающийся тем, что, с целью повышения точности синхронизации, введены компаратор и триггер, причем первый и второй входы компаратора соединены соответственно с выходами первого делителя частоты и реверсивного счетчика, а выход — с вторым входом первого делителя частоты с первым входом второго делителя частоты и является выходом строчного импульса; триггер включен между выходом формирователя импульсов и вторым входом второго делителя частоты, выход которого соединен с вторым входом формирователя сигнала отклонения, первый и второй выходы которого соединены с первым и вторым входами реверсивного счетчика соответственно, третий вход которого является входом сигнала установки начального коэффициента деления первого делителя частоты.

2. Синхронизатор по п. 1, о т л и ч а ю шийся тем, что формирователь сигнала отклонения содержит последовательно соединенные первый элемент И, первый триггер, первый элемент задержки и первый элемент запрета, выход которого является первым выходом формирователя сигнала отклонения, последовательно соединенные второй элемент И, второй триггер, второй элемент задержки и второй элемент запрета, выход которого является вторым выходом формирова-теля сигнала отклонения, а также последовательно соединенные третий элемент И и одновибратор, выход которого соединен с вторыми входами первого и второго элементов запрета, причем первый вход третьего элемента И соединен с вторыми входами первого триггера, второго элемента

И и является вторым входом формирователя сигнала отклонения, второй вход третьего элемента И соединен с вторыми входами первого элемента

И, второго триггера и является первым входом формирователя сигнала отклонения, а вторые выходы первого и второго триггеров соединены с первыми входами второго и первого элементов И соответственно.

1088152

Изобретение относится к телевидению, в частности к телевизионным формирователям сигналов синхронизации.

Известен телевизионный синхронизатор, содержащий задающий генератор, делитель частоты, формирователь кадровых импульсов, фазовый детектор, фильтр нижних частот и преобразователь частота — напряжение j1) .

Недостатком данного устройства является низкая точность преобразования частоты питающей сети в частоту синхронизирующих импульсов.

Наиболее близким к изобретению по технической сущности является телевизионный синхронизатор, содержащий задающий генератор, первый, второй и третий делители частоты, формирователь сигнала отклонения, формирователь импульсов, пороговый элемент, реверсивный счетчик, два элемента и цифро-аналоговый преобразователь

Недостатком известного устройства является низкая точность синхронизации формируемых импульсов с частотой сети.

Цель изобретения — повышение точности синхронизации.

Указанная цель достигается тем, что в телевизионный синхронизатор, содержащий последовательно соединенные задающий генератор и первый де-. литель частоты, а также второй делитель частоты, выход которого является выходом кадрового импульса, реверсивный счетчик, формирователь сигнала отклонения, первый вход которого соединен с выходом формирователя импульсов, вход которого является входом сигнала напряжения сети, дополнительно введены компаратор и триггер, причем первый и второй вхо ды компаратора соедийены соответственно с выходами первого делителя частоты и реверсивного счетчика, а выход — с вторым входом первого делителя частоты, с первым входом второго делителя частоты и является выходом строчного импульса; триггер включен между выходом формирователя импульсов и вторым входом второго делителя частоты, выход которого соединен с вторым входом формирователя сигнала отклонения, первый и второй выходы которого соединены с первым и вторым входами реверсив10

15 . элемент задержки и второй элемент запре20

50 ного счетчика соответственно, третий вход которого является входом сигнала установки начального коэффициента деления первого делителя частоты.

Кроме того, формирователь сигнала отклонения содержит последовательно соединенные первый элемент И, первый триггер, первый элемент задержки и первый элемент запрета, выход которого является первым выходом формирователя сигнала отклонения, последовательно соединенные второй элемент И, второй триггер, второй та,выход которого является вторым выходом формирователя сигнала отклонения, а также последовательно соединенные третий элемент И и одновибратор, выход которого соединен с вторыми входами первого и второго элементов запрета, причем первый вход третьего элемента И соединен с вторымн входами первого триггера, второго элемента И и является вторым входом формирователя сигнала отклонения, второй вход третьего элемента И соединен с вторыми входами первого элемента И, второго триггера и является первым входом формирователя сигнала отклонения, а вторые входы первого и второго триггеров соединены с первыми входами второго и первого элементов .И соответственно.

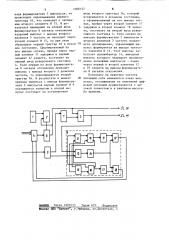

На чертеже представлена структурная электрическая схема телевизионного синхронизатора.

Телевизионный синхронизатор содержит задающий генератор 1, первый

2 и второй 3 делители частоты, реверсивный счетчик 4, формирователь 5 импульсов, компаратор 6, триггер 7 и формирователь 8 сигнала отклонения.

Формирователь 8 сигнала отклонения содержит первый элемент И 9, первый триггер 10, первый элемент

11 задержки, первый элемент 12 запрета, третий элемент И 13, одновибратор 14, второй элемент И 15, второй триггер 16, второй элемент 17 задержки и второй элемент 18 запрета.

Телевизионный синхронизатор работает следующим образом.

В момент включения устройства начинает работать в автоколебательном режиме задающий генератор i, триггеры 7, 10 и 16 устанавливаются

1088152

15 г

f — т с (2) в нулевое состояние, а в реверсивный счетчик 4 по входу установки начального коэффициента деления первого делителя частоты заносится число (!)

f,n где — частота задающего генератог ра 1; — частота питающей сети; — количество строк развертки, приходящихся на один период питающей сети. (Элементы .памяти для хранения числа m и управления записью этого числа в реверсивный счетчик 4 на чертеже не показаны).

Импульсы с задающего генератора

1 поступают на первый вход первого делителя 2 частоты и накапливаются

20 в нем до тех пор, пока комбинация двоичных сигналов на его выходе не совпадает с кодом, соответствующим числу п . В этот момент компаратор

6 формирует сигнал, обнуляющий первый делитель 2 частоты, который начинает новый цикл деления. Обнуление первого делителя 2 происходит с частотой строк.

Строчные импульсы с выхода компаратора 6 поступают на первый счетный вход второго делителя 3 частоты, увеличивая его содержимое до тех пор, пока на второй установочный вход через триггер 7 не поступит первый управляющий импульс с выхода форми- З5 рователя 5 импульсрв. При этом второй делитель 3 частоты обнуляется и начинает новый счет строчных импульсов синхронно с поступлением первого управляющего сигнала.

В момент, когда во втором делителе 3 фиксируется число строчных импульсов, на его выходе формируется кадровый импульс, поступающий на выход устройства и на второй вход фор- 45 мирователя 8 сигнала отклонения, на первый вход которого подаются управляющие импульсы с выхода формирователя 5 импульсов.

Формирователь 8 сигнала отклоне- 5О ния сравнивает время прихода этих импульсов.

При этом, если частота 1 питающей сети с высокой степенью точности связана с частотой 1 соотноше- 55 г нием то кадровый и управляющий импульсы поступают на входы формирователя 8 сигнала отклонения одновременно н на выходе третьего элемента И 13 появляется импульс, указывающий на то, что устройство работает в точном синхронизме с питающей сетью.

В этом случае на выходе одновибратора 14 вырабатывается импульс, запрещающий проникновение возможных импульсов — помех с выходов первого и второго триггеров 10 и 16 через первый и второй элементы 12 и 18 запрета на первый и второй входы реверсивного счетчика 4, который при этом сохраняет на выходе установленное ранее двоичное число.

Если частота питающей сети окажется меньшей, кадровый импульс на второй вход формирователя 8 сигнала отклонения поступит раньше, чем управляющий, что приведет к появлению импульса на выходе второго триггера 16. Этот импульс через второй элемент 17 задержки и второй элемент

18 запрета будет записан в реверсивный счетчик 4, увеличив его содержимое на единицу.

Если же частота питающей сети окажется выше определяемой соотношением (2), то кадровый импульс поступит позже, чем управляющий, выходной импульс аналогично сформируется на первом выходе формирователя 8 сигнала отклонения, что приведет к уменьшению содержимого реверсивного счетчика 4 на единицу.

Увеличение или уменьшение содержимого реверсивного счетчика 4, т.е. числа И1, приведет соответственно к уменьшению или увеличению периода строчных импульсов, формируемых устройством, а значит, и периода кадровых импульсов.

При отклонении частоты питающей сети от величины, определяемой соотношением (2), автоматическое регулирование схемы происходит до момента синхронного прихода управляющих импульсов и кадровых импульсов.

Формирователь 8 сигнала отклонения работает следующим образом.

Первый и второй триггеры 10 и 16 в исходном состоянии установлены в

"0", первый и второй элементы И 9 и

15 при этом открыты. Если первым на первый вход формирователя 8 сигнала отклонения приходит импульс с вы1088152

Вцщщц Заказ 2690/53 Тираж 635 Подписное

Филиал ППП Патент, г.ужгород, ул.Проектная, 4

В Я хода формирователя 5 импульсов, то происходит опрокидывание первого триггера 10, что приводит к запиранию второго элемента И 15. В результате пришедший на второй вход формирователя 8 сигнала отклонения кадровый импульс с выхода второго делителя 3 частоты не проходит через второй элемент И 15, но при этом сбрасывает первый триггер 10 в исход- 10 ное состояние. Сформированный на его выходе сигнал, пройдя через первый элемент 11 задержки и первый элемент 12 запрета, поступает на первый вход реверсивного счетчика 15

4. Если первым на вход формирователя 8 сигнала отклонения приходит импульс с выхода второго 3 делителя частоты, то опрокидывается второй триггер 16. В результате в момент 20 прихода импульса с выхода формирователя 5 импульсов первый элемент И 9 оказывается запертым и второй импульс поступает на установочный вход второго триггера 16, который возвращается в исходное состояние, а сформированный на его выходе сигнал, пройдя через второй элемент 17 задержки и второй элемент 18 запрета, поступает на второй вход реверсивного счетчика 4. Если сигнал на выходах формирователя 5 импульсов и второго делителя 3 частоты появляются одновременно, управляющий импульс формируется на выходе третьего элемента И 13. Этот импульс запускает одновибратор 14, выходной импульс. которого запрещает проникновение возможных импульсов — помех через первый и второй элементы 12 и 18 запрета на выходы формирователя 8 сигнала отклонения.

Поскольку на практике частота питающей сети изменяется очень медленно, отслеживание ее изменений цифровой системой осуществляется с высокой точностью и в реальном масштабе времени.