Устройство для прямого и обратного преобразования чисел из кода системы остаточных классов в двоичный код

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПРЯМОГО И ОБРАТНОГО ПРЕОБРАЗОВАНИЯ ЧИСЕЛ ИЗ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ДВОИЧНЫЙ КОД, содержащее (п+1) счетчиков, (ln-1) дешифраторов нуля, два элемента И, два триггера и переключатель, причем входы дешифраторов нуля соединены с выходами соответствующих счетчиков , единичный выход первого триггера подключен к первому входу первого элемента И, второй вход которого соединен с тактовым входом устройства, а выход подключен к первьм входам счетчиков, выход второго элемента И t подключен к первому входу переключателя , к второму входу которого подключен выход первого дешифратора нуля, выход переключателя соединен с нулевым входом первого триггера, единичный вход которого соединен с входом пуска устройства, выходы дешифраторов нуля с второго по п-и подключены к входам второго элемента И,, нулевой и единичный входы второго триггера подключены к входам управления переводом .двоичный код и обратно устройства соответстйенно, нулевой выход второго триггера подключен к входам управления сложением первого счетчика и вычитанием счетчиков с второго по ()-й, единичный выход второго триггера подключен к входам управления вычитанием первого счетчика и сложением счетчиков с второго по (п+1)-й, отличающееся % тем, что, с целью повышения быстродействия устройства, оно содержит третий и четвертый элементы И, причем входы с первого по третий третьего элемента И соединены соответственно с единичным выходом первого триггера, тактовым входом устройства и прямым выходом четвертого элемента И, инверсный выход которого подключен к 00 третьему входу первого элемента И, выход третьего элемента И подключен к вторым входам счетчиков с первого СП по п-й, первый и второй входы четвер того элемента И соединены соответстсо венно с нулевым выходом второго триггера и выходом ()-го дешифратора нуля.I

СОЮЗ СОВЕТСКИХ

Ю

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3531316/18»24 (22) 04.01.83 (46) 30.04.84. Бюл.  16 (72) П.Л.Прокопьев, В.А.Иванченко, О.E.Ìîë÷àíîâ и А.Д.Щечкин (53) 681 ° 381(088 ° 8) (56) 1. Авторское свидетельство СССР

У 574714, кл. G 06 5/00, 1974.

2. Авторское свидетельство СССР

В 756401, кл. 6 06 F 5/02, 1976 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ПРЯМОГО И

ОБРАТНОГО ПРЕОБРАЗОВАНИЯ ЧИСЕЛ ИЗ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ДВОИЧНЫЙ КОД, содер»кащее (й+1) счетчиков, (h+1) деюифраторов нуля, два элемента И, два триггере н переключатель, причем входы дешифраторов нуля соединены с выходами соответствующих счетчиков, единичный выход первого триггера подключен к первому входу первого элемента И, второй вход которого соепинен с тактовым вхопом устройства, а выхоп подключен к нерввм входам счетчиков, выход второго элемента И подключен к первому входу переключателя, к второму входу которого подключен выход первого девифратора нуля, выход переключателя соединен с нулевым входом первого триггера, единич« ный вход которого соединен с входом

„„SU„„1089573 A

34 9 5 06 F 5/02 пуска устройства, выходы дещифраторов нуля с второго по »» -й подключены к входам второго элемента И,. нулевой и единичный входы второго триггера подключены к входам управления переводом в двоичный код и обратно устройства соответственно, нулевой выход второго триггера подключен к входам управления слонением первого счетчика и вычитанием счетчиков с второго по (и+1)-й, единичный выход второго триггера поднлючен к входам упранления вычитанием первого счетчика н сложением счетчиков с второго по (n+1)-й, о т л и ч а ю щ е е с я тем, что, с целью ловынения быстро- Я действия устройства, оно содер»кит третий и четвертый элементы И, причем входы с первого по третий третьего элемента И соединены соответственно с единичным выходом первого триггера, тактовым входом устройства и прямьи выходок четвертого элемента И, инверсный выход которого подключен к ( третьему входу первого элемента И, Я) выход третьего элемента И подключен к вторым входам счетчиков с первого по »»-й, первый и второй входы четвертого элемента И соединены соответственно с нулев»ак выходок второго триггера и выходом (ь+1)-го дещифратора нуля °

1 1089573 2

Изобретение относится к вычислительной технике и может быть использовано в. цифровых вычислительных устройствах для перевода чисел из двоичной позиционной системы счисления 5 в. систему остаточных классов и обратно.

Известно устройство для прямого и обратного преобразования чисел из кода системы остаточных классов в двоичный код, содержащее приемные регистры, накапливающие счетчики, суммирующие по модулю счетчики, коммутирующие элементы (1 .

Недостаток указанного устройства заключается в значительном обьеме оборудования, предназначенного для преобразования чисел.

Наиболее близким к предлагаемому является устройство для прямого и обратного преобразования чисел нз кода системы остаточных классов в двоичный код, содержащее (n+1) счетчик, (n+1) дешифратор нуля, два элемента И, два триггера и переключатель, причем единичный выход первого триггера подключен к первому входу первого элемента И, второй вход которого соединен с тактовой шиной устройства, а выход соединен с так- З0 товой шиной устройства, выход подключен к входам счетчиков, выход второго элемента И подключен к первому входу переключателя, выход которого соединен с нулевым входом первого д триггера, единнчный выход которого соединен с входом пуска устройства, входы деши@раторов нуля соединены с выходами соответствующих счетчиков, выходы дешифраторов нуля подключены 40 к входам второго элемента И, а выход (в+1)-го дешифратора нуля соединен с вторым входом переключателя, нулевой и единичный входы второго триггера подключены к первой и второй as управляющим шинам устройства соответственно, нулевой выход второго триггера подключен к входу управления сюищением п первых счетчиков и входу

1 . управления вычитанием (n+1)-го счет- 50 чика, единичный выход второго триг.гера подключен к входу управления вычитанием первых счетчиков и входу управления сложением (11+1)-го счет- чика f23. 5S

Недостатком известного устройства . является сравнительно низкое быстро,действие.

Цель изобретения — повышение быстродействия устройства путем повышения скорости преобразования чисел из кода системы остаточных классов в двоичную позиционную систему.

Поставленная цель достигается тем, что устройство для прямого и обратного преобразования чисел из кода системы остаточных классов в двоичный код, содержащее (и+1) счетчиков, (и+1) дешифраторов нуля, два элемента И, два триггера и.переключатель, причем входы дешифраторов нуля соединены с выходами соответствующих счетчиков, единичный выход первого триггера подключен к первому входу первого элемента И, второй вход которого соединен с тактовым входом устройства, а выход подключен к первым входам счетчиков, выход второго элемента И подключен к первому входу переключателя, к второму входу которого подключен выход первого дешифратора нуля, выход переключателя соединен с нулевым входом первого триггера, единичный вход которого соединен с входом пуска устройства, выходы дешифраторов нуля с второго по и-й подключены к входам второго элемента И, нулевой и единичный входы второго триггера подключены к входам управления переводом в двоичный код и обратно устройства соответственно, нулевой выход второго триггера подкгночен к входам управления сложением первого счетчика и вычитавием счетчиков с второго по (и+1)-й, единичный выход второго триггера подключен к входам управления вычитанием первого счетчика и сложением счетчиков с второго по (n+1)-й, выходы счетчиков соединены с входами соответствующих дешифраторов нуля, содержит третий и четвертый элементы И, причем входы с первого по третий третьего элемента И соединены соответственно с единичным выходом первого триггера, тактовым входом устройства и прямым выходом четвертого элемента И, инверсный выход которого подключен к третьему входу первого элемента И, выход третьего элемента И подключен к вторым входам счетчиков с первого по пй, первый и второй входы четвертого элемента И соединены соответственно с нулевым выходом второго триггера и выходом (п+1)-го дешифратора нуля.

1089573

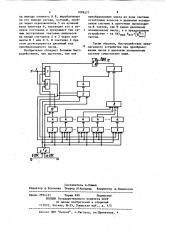

На чертеже представлена схема устройства для прямого и обратного преобразования чисел из кода системы остаточных классов в двоичный код.

Устройство. для прямого и обратно. го преобразования чисел из кода системы остаточных классов в двоичный код содержит триггер 1, первый счетчин 2, счетчики 3 с второго по (и+1)-й, дешифраторы 4 нуля, переключатель 5, триггер 6, элементы И 7 — 10, тактовый вход 11, вход 12 пуска, управляющий вход преобразования числа из двоичного ко. да 13, управляющий вход 14 преобразо- > вания числа в двоичный код.

Счетчики 3 осуществляют счет по модулю соответствующего основания системы остаточных классов. Сигналы на вторых входах счетчиков 2 и 3

20 вызывают изменение их содержимого на величину, равную наименьшему основанию системы остаточных классов.

Устройство для прямого и обратного преобразования чисел из кода системы остаточных классов в двоичный код работает следующим образом.

В режиме преобразования в код сис-, темы остаточных классов сигнал подаЭО ется на вход 13, переключатель 5 устанавливается в первое положение, число в двоичном коде записано в счетчике 2, счетчики 3 обнулены.

Триггер 1 в единичном состоянии, 5 и сигнал с его единичного выхода под- - готавливает счетчик 2 к работе в режиме "Вычитание", а счетчики 3 — к работе в режиме "Сложение".. Сигнал с нулевого выхода триггера 1 вырабатывает нулевой сигнал на единичном . выходе элемента И 10 .и единичный сигнал на нулевом выходе элемента И 10.

По сигналу, приходящему по входу 12 пуска на единичный вход триггера 6, он устанавливается в единичное сос45 тояние.и сигналом со своего единичного выхода открывает элемент И 7 по первому входу, на третий вход которого поступает единичный сигнал с нулевого выхода элемента И 10.. На второй вход элемента И 7 по тактовому входу 11 поступают тактовые импульсы, которые, пройдя через элемент И 7, производят постепенное вычитание единицы в счетчике 2 и 51 одновременно производят заполнение по единице счетчиков 3. В момент обнуления счетчика 2 срабатывает первый дешифратор 4 нуля, сигнал с выхода которого, пройдя через переключатель 5, переводит триггер 6 в нулевое состояние. При этом прекращается поступление тактовых импульсов через элемент И 7. В счетчиках 3 зарегистрирован код системы остаточных классов, соответствующий двоичному коду, первоначально записанному в счетчике 2.

В режиме преобразования в двоичный код сигнал подается на вход .14, переключатель 5 устанавливается во второе положение, число в коде системы остаточных классов записано в счетчиках 3, причем (и+1)-й счетчик 3 имеет наименьший модуль. Счетчик 2 обнулен.

Происходит переключение триггера 1 в нулевое состояние, сигнал с его нулевого выхода подготавливает счетчик 2 к работе в режиме "Сложение", счетчики 3 — к работе. в режиме "Вычитание", а элемент И 10 - к работе в зависимости от значения выходного сигнала (и+1)-ro дешифратора 4 нуля.

По сигналу, приходящему по входу 12 пуска, триггер 6 устанавливается в единичное состояние и разрешает про-, г хождение тактовых импульсов через элемент И 7 либо элемент И 9 на входы счетчиков 2 и 3 ° Если значение (n+1)-го счетчика 3 не равно нулю, то нулевой сигнал выхода (и+1)-го дешифратора 4 нуля, пройдя через элемент И 10, откроет по третьему входу элемент И 7 и закроет по третьему входу элемент И 9. Тактовые импульсы, пройдя через элемент И 7, гроизводят постоянное заполнение по единице счетчика 2 и одновременно вычитание по единице из счетчиков 3. Так будет до тех пор, пока содержимое (п+1)-го счетчика 3 не станет равным нулю.

Как только (и+1)-й счетчик 3 станет равным нулю, срабатывает (и+1)-й дешифратор 4 нуля, сигнал с которого, пройдя через элемент И 10, закроет элемент И 7 и откроет по третьему входу элемент И 9. Тактовые импульсы, пройдя через элемент И 9, производят постепенное увеличение счетчика 2 на константу, равную модулю (n+1)-го счетчика 3 и одновременно вычитание той же константы из всех счетчиков 3, кроме (n+1)-го.

В момент обнуления всех счетчиков 3 срабатывают дешифраторы 4 нуля, сигналы с выходов которых, поступая

108

Составитель А ° Клюев

Редактор А.Власенко Техред И.Асталош Корректор А.Зимокосов

Заказ 2934/45 Тирах 699 Подписное

ВНИИПИ Государственного комитета СССР.по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г.уигород, ул.Проектная, 4 на выходы элемента И 8, вырабатывают на его выходе сигнал, который, пройдя через переключатель 5 на нулевой вход триггера 6, переводит его в нулевое состояние и прекращает тем самым поступление тактовых импульсов на входы счетчиков 2 и 3 через элементы И 7 или И 9. В счетчике 2 при этом регистрируется двоичный код преобразованного числа.

Изобретение обладает большим быстродействием, чем прототип, так как

9 7.3 Ь преобразование числа из кода системы остаточных классов в двоичную позиционную систему.в прототипе происходит за К тактов, где Й равно двоичной позиционному числу, а в предлагаемом устройстве - за (й) Р„ „+(—

N тактов. пил

Таким образом, быстродействие предлагаемого устройства прн преобразовании числа в двоичную позиционную систему существенно выше.