Устройство приоритета

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ПРИОРИТЕТА, содержащее два регистра, две группы элементов И, группу эле ментов ИЛИ, причем группа запросных входов устройства соединена с группой информационных входов первого регистра, группа входов сброса которого соединена с группой сигнальных входов устройства, разрядные выходы первого регистра соединеды с первыми входами собтветствующих элементов И первой группы , выходы элементов И первой группы соединены с информационными входами, второго регистра, разрядные выходы которого соединены с первыми входами элементов И второй/группы, вторые входы которых соединены с опросным входом устройства, выходы элементов И второй группы являются группой выходов устройства, тактовый вход устройства соединен с вторыми входами элементов И первой группы, вход сброса устройства соединен с входом сброса первого разряда второго регистра и с первым входом первого элемента ИЛИ группы, второй вход и выход которого соединены соответственно с выходом первого разряда второго регистра и с входом сброса второго разряда второго регистра, выход каждого разряда второго регистра, начиная с второго, соединен с соответствующим входом одноименного элемента ИЛИ группы, выход каждого i-ro элемента ИЛИ группы, начиная с второго, соединен с входом сброса (i-bl)-ro i разряда второго регистра, отличающееся (Л тем, что, с целью повыщения его быстродействия , выход каждого i-ro ра13ряда второго регистра соединен с соответствующим входом

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ .

РЕСПУБЛИН З(51) G 06 F 9/46

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ч pppp>r—

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 111 "",, К ABTOPCKOMY СВИДЕТЕЛЬСТВУ 1 ий,1:,;о.аи

Ги

7 и (21) 3544458I18-24 (22) 21.01.83 (46) 07.05.84. Бюл. № 17 (72) О. Е. Молчанов, С. Л. Мелешко, И. H. Основенко и А. Д. Шечкин (53) 681.325 (088.8) (56) 1. Авторское свидетельство СССР № 942022, кл. G 06 F 9)46, 1982.

2. Авторское свидетельство СССР № 425177, кл. G 06 Р 9)46, 1974 (прототип). (54) (57) УСТРОИСТВО ПРИОРИТЕТА, содержагцее два регистра, две группы элементов И, группу элементов ИЛИ, причем группа запросных входов устройства соединена с группой информационных входов первого регистра, группа входов сброса которого соединена с группой сигнальных входов устройства, разрядные выходы первого регистра соединены с первыми входами соответствующих элементов И первой группы, выходы элементов И первой группы соединены с информационными входами второго регистра, разрядные выходы которого соединены с первыми входами элементов И второй группы, вторые входы которых сое„„ЯЦ„„1091163 A динены с опросным входом устройства, выходы элементов И второй группы являются группой выходов устройства, тактовый вход устройства соединен с вторыми входами элементов И первой группы, вход сброса устройства соединен с входом сброса первого разряда второго регистра и с первым входом первого элемента ИЛИ группы, второй вход и выход которого соединены соответственно с выходом первого разряда второго регистра и с входом сброса второго разряда второго регистра, выход каждого разряда второго регистра, начиная с второго, соединен с соответствующим входом одноименного элемента ИЛИ группы, выход каждого i-го элемента ИЛИ группы, начиная с второго, соединен с входом сброса (i+1) -го разряда второго регистра, отличающееся тем, что, с целью повышения его быстродействия, выход каждого i-го разряда второго регистра соединен с соответствующим входом (i+-1)-го и последуюших элементов

ИЛИ группы, вход сброса устройства соединен с соответствующими входами всех элементов ИЛИ группы, начиная с второго.

1091163

Составитель М. Кудряшев

Редактор С. Квятковская Техред И. Верес Корректор О. Тигор

Заказ 2827/45 Теи раж 699 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Изобретение относится к вычислительной технике и может быть использовано в устройствах прерывания программ.

Известно многоканальное устройство приоритета, содержащее элементы И и ИЛИ, элементы задержки и регистр (1)., Недостаток указанного устройства — невысокое быстродействие.

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство приоритета, 10 содержащее регистр индикации запросов, вспомогательный регистр, элементы И . и

ИЛИ, причем единичный выход каждого разряда регистра индикации запросов соединен через соответствующий элемент И с единичным входом соответствующего разрядг вспомогательного регистра, единичный выход которого соединен с первым входом элемента ИЛИ данного разряда, второй вход которого соединен с выходом элемента ИЛИ предыдущего разряда, а выход — с нулевым входом разряда вспомогательного реги стр а (2).

Недостаток известного устройства — .невысокое быстродействие.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройстве приоритета, содержащем два регистра, две группы элементов И, группу элементов ИЛИ, причем группа запросных входов устройства соединена с группой информ ационных входов первого регистра, группа входов сброса которого соединена с группой сигнальных входов устройства, разрядные выходы первого регистра соединены с первыми входами соответствующих эле- З5 ментов И первой группы, выходы элементов

И первой группы соединены с информационными входами второго регистра, разрядные выходы которого соединены с первыми входами элементов И второй группы, вторые входы которых соединены с опросным вхо- 40 дом устройства, выходы элементов И второй группы являются группой выходов устройства, тактовый вход устройства соединен с вторыми входами элементов И первой группы, вход сброса устройства соединен с вхо- 45 дом сброса первого разряда второго регистра и с первым входом первого элемента

ИЛИ группы, второй вход и выход которого соединены соответственно с выходом первого разряда второго регистра и с входом сброса второго разряда второго регистра, выход каждого разряда второго регистра, начиная со второго, соединен с соответствующим входом одноименного элемента ИЛИ группы, выход каждого i-го элемента ИЛИ группы, начиная с второго, соединен с входом сброса (i+1)-го разряда второго регистра, выход каждого i-го разряда второго регистра соединен с соответствующим входом (i+1)-го и последующих элементов ИЛИ группы, вход сброса устройства соединен с соответствующими входами всех элементов ИЛИ группы, начиная с второго.

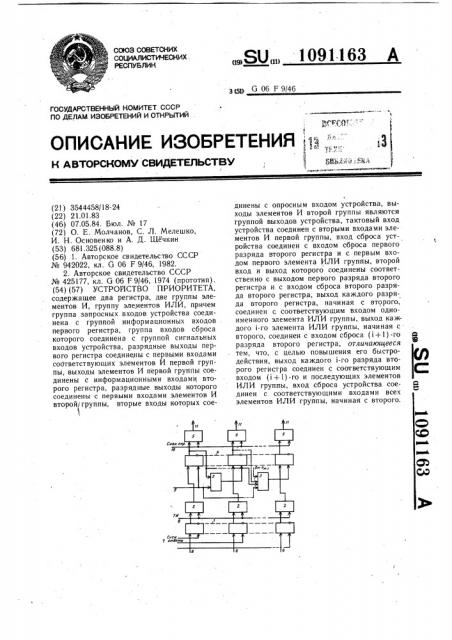

На чертеже представлена функциональная схема устройства.

Устройство содержит регистр l, группу элементов И 2, группу элементов ИЛИ 3, регистр 4, группу элементов И 5, группу запросных входов 6 устройства, группу сигнальных входов 7 устройства, тактовый вход 8 устройства, вход 9 сброса устройства, опросный вход 10 устройства.

Устройство работает следующим образом

Сигналы запросов согласно их приоритетам фиксируются в соответствующих разрядах регистра 1. Время прихода заявок произвольно. По синхроимпульсу с входа 8 заявки, хранящиеся в регистре 1, переписываются через элементы И 2 в регистр 4, установленный в исходном состоянии в «О» импульсом с входа 9, Поэтому в исходном положении на прямых выходах регистра 4 низкий уровень выходного сигнала. При установке любого разряда регистра 4 в единичное состояние сигнал выеокого уровня с его прямого выхода устанавливает в нулевое состояние все остальные разряды с приоритетом более низким по отношению к этому разряду. Установка в «О» разрядов регистра 4 произойдет с задержкой, равной времени задержки элемента ИЛИ ЗГ.

После этого может быть подан сигнал на вход 10, по которому запрос высшего приоритета поступает через элементы И 5 на выходы 11 устройства приоритета.

Применение изобретения позволяет повысить„быстродействие устройства.