Амплитудный дифференциальный дискриминатор

Иллюстрации

Показать всеРеферат

А П1ПИТУДНЫЙ ДИФФЕРЕНЦ11АЛЬНЫЙ ДИСКРИМИНАТОР для спектрометрического анализатора, содержащий дискриминаторы анализатора, содержащий дискриминаторы верхнего и нижнего уровней, входы которых соединены с входной пшной, триггер, первый вход которого соединен с выходом дискриминатора верхнего уровня, а второй вход через логический элемент НЕ соединен с выходом формирователя импульсов и первым входов выходного логического элемента И, второй вход которого подключен к выходу триггера, отличающийся тем, что, с целью повышения точности временной привязки выходного сигнала, в него введены дополнительньш триггер RS-типа, дополнительные логические элементы НЕ и И, генератор тока, блок конденсаторов с переключателем и источник зарядного тока, первьш выход которого соединен с первым входом дополнительного логического элемента И, выходом дополнительного логического элемента НЕ и точкой соединения конденсаторов бло .ка конденсаторов, вторая обкладка одного из которых соединена с общей шиной непосредственно, а вторые обкладки остальных конденсаторов соединены с общей шиной через переключатель , причем выходы генератора С S тока соединены с вторым входом дополнительного логического элемента И (Л и первьш входом источника зарядного тока, второй вход которого соединен с вькодом дискриминатора нижнего уровня и R-входом дополнительного триггера, RS-типа, S-вход которого подключен к выходу дополнительного о логического элемента И, третий вход со которого подключен к одному выходу п1 дополнительного триггера RS-типа, со второй выход которого соединен с входом дополнительного логического элемента НЕ и входом формирователя импульсов.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ll0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬГГИЙ (21) 2607991/18-21 (22) 21.04.78 (46) 07.05.84. Бюл. 11 17 (72) М.E.Глушковский (53) 621.374.4 (088.8) (56) 1. Авторское свидетельство СССР

11 558229, кл. G 01 К 29/00, 1975.

2. Bernard P. and others.

"Journ. Unstrum and Nethods", ч, 68, 1 968,,р.213. (54) (57) АМПЛИТУДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ДИСКРИМИНАТОР для спектрометрического анализатора, содержащий дискриминаторы анализатора, содержащий дискриминаторы верхнего H нижнего уровней, входы которых соединены с входной шиной, триггер, первый вход которого соединен с выходом дискриминатора верхнего уровня, а второй вход через логический элемент НЕ соединен с выходом формирователя импульсов и первым входов выходного логического элемента И, второй вход которого подключен к выходу триггера, отличающийся тем, что, с целью повышения точности временной привязки выходного сигнала, в него введены дополнительный тригÄÄSUÄÄ 1()91311

3(11 Н 03 К 3/22

rep RS-типа, дополнительные логические элементы HE и И, генератор тока, блок конденсаторов с переключателем и источник зарядного тока, первый выход которого соединен с первым входом дополнительного логического элемента И, выходом дополнительного логического элемента HE и точкой соединения конденсаторов бло.ка конденсаторов, вторая обкладка одного из которых соединена с общей шиной непосредственно, а вторые обкладки остальных конденсаторов соединены с общей шиной через переключатель, причем выходы генератора тока соединены с вторым входом дополнительного логического элемента И и первым входом источника зарядного тока, второй вход которого соединен с выходом дискриминатора нижнего уровня и R-входом дополнительного триггера, RS-типа, S-вход которого подключен к выходу дополнительного логического элемента И, третий вход которого подключен к одному выходу дополнительного триггера RS-типа, второй выход которого соединен с входом дополнительного логического элемента

НЕ и входом формирователя импульсов.

1 1Q913

Изобретение относится к ядерной электронике и может быть использовано при измерении амплитуд статистически распределенных импульсов в медицине, биологии и других областях науки и техники.

Известен амплитудный дифференциальный дискриминатор, в котором выходной сигнал формируется с произвольным сдвигом относительно входного, а временный сдвиг уменьшается за счет введения схемы временной привязки (например, к вершине входного сигнала), сигнал с выхода которой задерживается и стробирует выходной сигнал дискриминатора(1 ).

Однако такое выполнение дискриминатора приводит к значительному увеличению оборудования, поскольку схема временной привязки является сложным аналоговым устройством по сравнению с собственно дифференциальным дискриминатором и имеет нелинейный усилитель, дифференциатор, еще один дискриминатор и дополнительную логику. Кроме того, дискриминатор не позволяет получить главную задержку выходного сигнала, что ограничивает его применение.

Наиболее близким техническим ре30 шением к изобретению является амплитудный дифференциальный дискриминатор, который состоит из дискриминаторов нижнего и верхнего уровней, формирователя со схемой И и инвертором, а также триггером, блокирующим схему И при срабатывании дискриминатора верхнего уровня. В дискриминаторе выходной сигнал формируется с произвольным сдвигом относительно выходного, так как генерация этого сигнала производится от заднего фронта дискриминатора нижнего уровня(23.

Недостатком известного амплитудного дифференциального дискриминатора является низкая точность временной привязки выходного сигнала, заключающаяся в том, что выходной сигнал имеет большую неопределенность относительно входного. Это не позволяет использовать дискриминатор в устройствах со схемами совпадений, многомерном анализе и др.

Цель изобретения — повышение точности временной привязки выходного 55 сигнала °

Поставленная цель достигается тем, что в амплитудный дифференциаль11 2 ный дискриминатор для спектрометрического анализа, содержащий дискриминаторы верхнего и нижнего уровней, входы которых соединены с входной шиной, триггер, первый вход котороro соединен с выходом дискриминатора верхнего уровня, а второй вход через логический элемент НЕ соединен с выходом формирователя импульсоа и первым входом выходного логического элемента И, второй вход которого подключен к выходу триггера, введены дополнительный триггер RS-типа, дополнительные логические элементы НЕ и И, генератор тока, блок конденсаторов с переключателем и источник зарядного тока, первый выход которого соединен с первым входом дополнительного логического элемента И, выходом дополнительного логического элемента HE и точкой соединения конденсаторов блока конденсаторов, вторая обкладка одного из которых соединена с общей шиной непосредственко, а вторые обкладки остальных конденсаторов соединены с общей шиной через переключатель, причем выходы генератора тока cîeäèíåíû с вторым входом дополнительного логического элемента И и первым входом источника зарядного тока, второй вход которого соединен с выходом дискриминатором нижнего уровня и R-входом дополнительного триггера RS-типа, S-вход которого подключен к выходу дополнительного логического элемента И, третий вход которого подключен к одному выходу дополнительного триггера RS-типа, второй выход которого соединен с входом дополнительного логического элемента НЕ и входом формирователя импульсов.

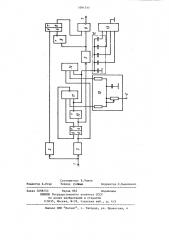

На чертеже представлена блоксхема амплитудного дифференциального дискриминатора.

Амплитудный дифференциальный дискриминатор содержит входную шину 1, дискриминаторы нижнего 2 и верхнего 3 уровней, триггер 4, формирователь 5 импульсов и выходной логический элемент И 6, соединенный с выходом 7 ° Выход дискриминатора 3 верхнего уровня через триггер 8 подключен к второму входу выходного логического элемента И б, а выход формирователя 5 импульсов через логический элемент НЕ 9 — к второму входу триггера 8. Один выход триг3 1091 гера 4 через логический элемент

НЕ 10 и логический элемент И ll coeдинен со своим вторым входом, а второй выход подключен к второму входу логического элемента И 11.

Выход логического элемента НЕ 10 через блок 12 конденсаторов и переключатель 13 соединен с общей шиной, а также подключен к первому выходу источника 14 зарядного тока.

Выходы генератора 15 тока соединены с вторым входом логического элемента И ll и первым входом источника 14 зарядного тока.

Амплитудный дифференциальный дискриминатор работает следующим образом.

Входной сигнал поступает на входную шину 1 и оба дискриминатора, а выходной сигнал появляется только в случае, если срабатывает дискриминатор 2 нижнего уровня и не срабатывает дискриминатор 3 верхнего уровня, т.е. импульс попадает в

"окно". При этом сигнал проходит по цепи: дискриминатор 2 нижнего уровня, дополнительный триггер 4, формирователь 5, выходной логический элемент И б. Если срабатывает дискриминатор 3 верхнего уровня, то он при помощи триггера 8 запрещает прохождение сигнала через выходной логический элемент И б, причем сбрасьгвается задним фронтом этого сигнала в исходное состояние через логический элемент НЕ 9.

Импульс на дополнительном триггере 4, от заднего фронта которого генерируется выходной сигнал, формируется следующим образом. В исходном состоянии выходной транзис— тор логического элемента HE 10 находится в насыщенном состоянии и -; напряжение на первом конденсаторе!

3i 1 4 блока 12 равно нулю. При срабатывании дискриминатора 2 нижнего уровня перебрасывается дополнительный триггер 4, era выходной транзистор запирается и указанный конденсатор начинает заряжаться входным током дополнительного элемента И 11.

Входной ток источника 14 зарядного тока не заряжает первый конденсатор блока 12, так как на второй его вход подается отпирающий сигнал непо" редственно с дискриминатора 2 нижнего уровня. После окончания импульса с дискриминатора 2 нижнего уровня ток заряда конденсатора увеличится вдвое за счет включения входного тока источника 14 заряд-. ного тока. Процесс заряда продолжается до тех пор, пока не будет достигнут порог срабатывания логического элемента И 11, который сбрасывает дополнительный триггер 4 в исходное состояние и запускает формирователь 5 °

Поскольку форма импульса в спектрометрическом тракте около вершины симметрична, то изменение амплитуды входного сигнала в пределах ширины

"окна" не приводит к сдвигу выходного сигнала. Регулировка задержки выходного сигнала осуществляется дискретно при помощи подключения дополнительных конденсаторов блока !2 через переключатель 13 и плавно при помощи сдвоенного регулирующего генератора 15 тока, который отбирает часть входных токов логического элемента И )1 и источника 14 зарядного тока, не нарушая их равенства.

Равенство входных токов логического элемента И 11 и источника 14 зарядно- го тока обеспечивается выполнением этих схем на интегральной технологии на одном кристалле.

1091311

Составитель В.Чижов

Редактор А. Огар Техред О.Веце Корректор Л.Пилипенко

Заказ 3098/53 Тираж 862 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35„ Раушская наб., д. 4/5

Филиал IIIIII "Патент", г. Ужгород, ул. Проектная, 4