Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ , содержащий регистр последовательных приближений, цифро-аналоговый преобразователь, генератор тактовых импульсов, генератор запускающих импульсов и компаратор, первый вход которого подключен к входной шине, второй вход - к выходу цифро-аналогового преобразователя, входы которого соединены с соответствую щими выходами регистра последовательных приближений, первый и второй входы которого подключены к выходам генератора тактовых импульсов и генератора запускающих импульсов соответственно, о тли ч ающийс я тем, что, с целью расширения динамического диапазона преобразуемого сигнала, в него введены первый и второй дополнительные компараторы, первый и второй элементы И, элемент ШШ, инвертор, распределитель кодов, источник порогового уровня и масштабируюш 1й усилитель, вход которого соединен с входной шиной, а выход - с первыми входами первого и второго дополнительного компаратора, второй вход первого дополнительного компаратора соединен с источником порогового уровня, а второй вход второго дополнительного компаратора соединен с выходом цифро-аналогового i преобразователя, при этом выходы компаратора и второго дополнительного (Л компаратора соединены соответственно С с первыми входсШи первого и второго элементов И, второй вход второго элемента И через инвертор подключен к выходу первого дополнительного компаратора , первому входу распределителя кодов и второму входу первого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй х вход которого соединен с выходом второго элемента Ы, а выход - с третьим 2 входом регистра последовательных jO приближений, выходы которого соедине-i ны соответственно с вторыми входами распределителя кодов.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (1И

3(511 H 03 К 13/17

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3470954/18 — 21 (22) 14.07.82 (46) 07.05.84. Бюл. -17 (72) A.И.Коников (71) Московский ордена Ленина авиационный институт им. Серго Орджоникидзе (53) 681.325(088.8) (56) 1. Гитис З.И. Преобразователи информации для электронных цифровых вычислительных устройств. H. "Энергия", 1970, с.309.

2. "Злектронная промышленность", 1978, Р 8, с.l4-16 (прототип). (54) (57) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий регистр последовательных приближений, цифро-аналоговый преобразователь, генератор тактовых импульсов, генератор запускающих импульсов и компаратор, первый вход которого подключен к входной шине, второй вход — к выходу цифро-аналогового преобразователя, входы которого соединены с соответствую— щими выходами регистра последовательных приближений, первый и второй входы которого подключены к выходам генератора тактовых импульсов и генератора запускающих импульсов соответственно, о т л и ч а ю щ и йс я тем, что, с целью расширения динамического диапазона преобразуемого сигнала, в него введены первый и второй дополнительные компараторы, первый и второй элементы И, элемент ИЛИ, инвертор, распределитель коцов, источник порогового уровня и масштабирующий усилитель, вход которого соединен с входной шиной, а выход — с первыми входами первого и второго дополнительного компаратора, второй вход первого дополнительного компаратора соединен с источником порогового уровня, а второй вход второго дополнительного компаратора соединен с выходом цифро-аналогового преобразователя, при этом выходы ком- Е

O паратора и второго дополнительного компаратора соединены соответственно с первыми входами первого и второго элементов И, второй вход второго элемента И через инвертор подключен к

2 выходу первого дополнительного компаратора, первому входу распределителя кодов и второму входу первого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а выход — с третьим входом регистра последовательных приближений, выходы которого соедине- ны соответственно с вторыми входами распределителя кодов.

109!331

Изобретение относится к вычислительной технике и может быть использовано в контрольно-измерительных, информационных и радиотехнических системах различного назначения.

Известны аналого-цифровые пре-. образователи, построенные по методу поразрядного уравновешивания. Устройство включает преобразователь кода в напряжение (НКН), компаратор и уст!

О ройство управления, причем на один вход компаратора подается входное напряжение, другой вход подключен к выходу ПКН, входы ПКН соединены с выходами устройства управления, на вход устройства. управления поступает сигнал с выхода компаратора )lj .

Недостатком данного устройства является малая величина динамического диапазона входного сигнала.

Наиболее близким к предлагаемому является аналого-цифровой преобразователь поразрядного уравновешивания, который содержит регистр последовательного приближения (РПП), источник тактовых импульсов, источник запускающего импульса, компаратор и цифро-аналоговый преобразователь (ЦАП ); причем выходы регистра последовательных приближений подключены к выходам ЦАП, первый и второй входы РПП подключены к генератору тактовых импульсов и генератору запускающих импульсов соответственно, а также к входу компаратора. Первый вход компаратора соединен с выходом

ЦАП, а второй подключен к входной шине 2j .

Недостатком известного устройства является малый динамический 40 диапазон входного сигнала.

Цель изобретения — расширение динамического диапазона преобразуемого сигнала.

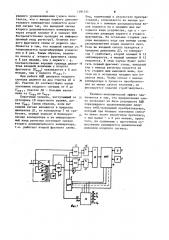

Поставленная цель достигается тем, 45 что в аналого-цифровой преобразователь, содержащий регистр последовательных приближений, цифро-аналоговый преобразователь, генератор тактовых импульсов, генератор запускающих импульсов и компаратор, первый вход которого подключен к входной шине, второй вход — к выходу цифроаналогового преобразователя,, входы которого соединены с соответствующими выходами регистра последовательных приближений, первый и второй входы которого подключены к выходам генератора тактовых импульсов и генератора запускающих импульсов соответственно, введены г ервый и второй дополнительные компараторы, первый и второй элементы 11 элемент . 1ЛИ, инвертор, распределитель кодов, и"точник порогового уровня и масшта5ирующий усилитель, вход которого соединен с входной шиной, а выход— первыми входами первого и второго дополнительного компаратора, второй вход первого дополнительного компаратора соединен с источником лоро:".ового уровня, а второй вход второго дополнительного компаратора соединен с выходом цифро-аналогового преобразователя, при этом выходы компаратора и второго дополнительного компаратора соединены соответственно с первыми входами первого и второго элементов И, второй вход второго элемента И. через инвертор подключен к выходу первого дополнительного компаратора, первому входу распределителя кодов и второму входу первого элемента И,выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а выход — с третьим входом регистра последовательH Ix п1 ибли iеHHA соединены соответственно с вторыми входами распределителя кодов, На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг.2распределитель кодов инвариант).

Входная шина 1 соединена с входом компаратора 2 и входом масштабирующего усилителя 3, к управляющим входам регистра 4 последовательных приближений подключены генератор 5 тактовых импульсов и генератор 6 запускающих импульсов, выход масштабирую. щего усилителя подключен к первым входам первого и второго дополнительных компараторов 7 и 8, вторые входы основного и второго дополнительного компараторов соединены с зыходом ЦАП 9, второй вход первого дополнительного компаратора соединен с источником 10 порогового уровня, выход первого дополнительного компар»I тора соединен с входом инвертора 1, а также с первым входом первого элемента И 12, первый вход второго элемента И 13 подключен к выходу инвертора ll выход первого дополнительного компаратора 7 соединен с управляющим входом распределителя 14 кодов, вторые входы первого и второго з 109 элементов И 12 и !3 подключены соответственно к выходам компаратора 2 и второго дополнительного компаратора 8, выходы первого и второго элементов И 12 и 13 соединены с входами элемента ИЛИ 15, выход которого подключен к информационному входу регистра 4, выходы регистра 4 соединены с информационными входами распределителя 14 кодов, выходы распределителя кодов подключены к выходной шине 16, вход первого дополнительного компаратора подключен к шине 17 строба.

Усилитель 3 состоит из резисторного делителя 18, состоящего из резисторов 19 и 20, и усилителя 21, входы резисторного делителя соединены с выходом усилителя и общей точкой ВыхОд подключен к инвертирующему входу усилителя 21, неинвертирующий вход подключен к входной шине I.

Управляющая входная шина 22 подключена к входу инвертора 23 управления, выход которого соединен с управляющей шиной 24. Формирователь

25 выходного кода состоит из формирователей 26-28 младших, средних и старших разрядов соответственно.

Формирователь младших разрядов, в свою очередь, состоит из К отдельных двухвходовых элементов И 29 (К вЂ” коэффициент масштабирования, в рассмат. риваемом примере К=4 }, один вход которых подключен к управляющей выходной шине 24, а другой соединен с одной из младших шин, входящих в шину

30 входного кода. Формирователь старших разрядов состоит из К отдельных двухвходовых элементов И 31, один из 40 входов которых подключен к управляющей входной шине, а другой соединен с одной из шин старших разрядов, входящих в шину 30. Формирователь кода средних разрядов состоит из и-2К 4 отдельных формирователей, каждый из которых включает первый 32 и второй

33 дополнительные элементы И, выходы которых подключены к входам дополнительного элемента ИЛИ 34, первый вход первого дополнительного элемента И соединен с (i-2)-й шиной входного кода, где i — номер разряда выходного кода, второй вход первого дополнительного элемента 55

И 32 подключен к входной управляющей шине, первый вход второго дополнительного элемента И 33 соединен с!

33! 4 входом -й шины 30 входного кода, второй вход второго дополнительного элемента И 33 соединен с управляющей выходной шиной 24.

Устройство работает следующим образом.

Фрагмент схемы, состоящий из входной шины 1, компаратора 2, первого элемента И 12, элемента ИЛИ !5, регистра 4 последовательных приближений, ЦАП 9, генератора 5 тактовых импульсов и генератора 6 запускающих импульсов, представляет собой известную схему АЦП поразрядного уравновешивания. Дополнительными по сравнению с известной схемой здесь являются первый элемент И 12, и элемент ИЛИ 15, однако здесь будем полагать, что на первый вход первого элемента И 12 с Выхода первого дополнительного компаратора 7 подается логическая единица т, к, что сигнал с выхода компаратора 2 беспрепятственно проходит через указанные элементы И и ИЛИ на информационный вход регистра 4. Указанный фрагмент схемы работает как классический АЦП поразрядного уравновешивания. Функционирование происходит под действием управляющих импульсов регистра последовательных приближений. Б каждом такте регистр 4 вырабатывает код типа 10...0 или Oll ° ° .l в зависимости от принятой логики.

Сигнал с выхода компаратора 2 с приходом тактового импульса устанавливает старший разряд регистра в 0 или ! в зависимости от того, сработал или нет компаратор 2, одновременно устанавливается в нуль следующий по старшинству разряд регистра. С приходом очередного тактового импульса определяется цифра во втором разряде и устанавливается единица в третьем разряде и т.д. По заполнению регистра завершается цикл преобразования, разряды регистра блокируются по входам и информация хранится до начала нового цикла. В исходное состояние регистр приводится соответствующим сигналом с выхода генератора запускающих импульсов.

Фрагмент схемы, состоящий из масштабирующего усилителя, второго дополнительного компаратора, второго элемента И, элемента ИЛИ, регистра, генератора тактовых импульсов, генератора запускающих импульсов и ЦАП, представляет собой также схему пораз1091331 рядного уравновешивания (здесь полагается, что с выхода первого дополнительного компаратора снимается нулевой сигнал так, что выходной сигнал второго дополнительного компаратора через второй элемент И и элемент ИЛИ беспрепятственно проходит на информационный вход регистра). Отличие второго фрагмента схемы от первого закЛючается в том, что входной сигнал ус-10 танавливается масштабирующим усилителем в К раз. Таким образом, величина кванта q второго фрагмента схемы в К раз меньше, чем у первого — q.

Соответственно верхняя граница диапа- 15 зона входной величины у второго фрагмента (11 о„ ) оказывается в К раз меньше, чем у йервого (0„,о„ ).

При работе АЦП диапазон входного сигнала делится иа два участка Д1 и щ

Д2. Участок Дl соответствует малым значениям входного сигнала от О до

I участок Д2 — большим зиаче-! ниям от Ощо» до У о °

Пороговый уровень, поступающий от 2s источника lO noyoroaoro уровня, pa-: ! вен Уп,ц . Таким образом, если выходной сигнал находится в пределах диапазона Дl, то компаратор 7 не сработает, первый элемент И блокирует сигнал компаратора и на информационный вход регистра поступает сигнал второго дополнительного компаратора, т.е. работает второй фрагмент схемы.

Код, полученный в результате преобразования, записывается на выходе регистра и с помощью распределителя кодов подается íà и младших шин выходного кода устройства, где n — количество разрядов первого и второго фрагментов. На остальные старшие разряды выходного кода при помощи схемы распределителя кодов подаются нуля.

Если же входной сигнал находится в пределах диапазона Д2, то компаратор 7 сработает, второй элемент И 13 заблокируется, а первый элемент И 12 откроется. В этом случае будет работать первый фрагмент схемы, выходной код с выхода регистра подается на

k-и старших шин выходной шины, при этом на и остальных младших шин подается нуль. Чтобы сигнал с выхода компаратора в процессе преобразов»ния не менял своего значения, он фиксируется подачей строб-импульса.

Технико-экономический эффект заключается в том, что предлагаемая схема позволяет на базе разрядного АЦП поразрядного уравновешивания полу" чить n+KL-разрядный преобразователь, который при больших значениях сигнала имеет квант аналогичен прототигу, а при малых — в К раз меньше, кроме того, по сравнению с прототипом существенно расширяется динамический диапазон входного сигнала.

1091331

Составитель И.Романова

Редактор Ю.Ковач Техред M.Òåïåð Корректор А.Пзятко

Заказ 3100/54 Тираж 862 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Г1осква, Ж-35, Раушская наб,, д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4