Логический анализатор

Иллюстрации

Показать всеРеферат

1. ЛОГИЧЕСКИЙ АНАЛИЗАТОР, содержащий регистр, сумматор по модулю два, первая группа входов которого соединена с выходами регистра, а выходы сумматора по модулю два соединены с информационными входами регистра, индикатор, соединенный с выходами регистра, отличающийся тем, что, с целью сокращения времени диагностики неисправностей цифровых устройств путем локализации однобитовой ошибки, в него вве дены двоичный счетчик с исключенным нулевым состоянием и элемент И, причем вторая группа входов сумматора по модулю два соединена с выходами двоичного счетчика с исключенньм нулевым состоянием, вход начальной установки двоичного счетчика с исключенным нулевым состоянием и вход установки нуля регистра соединены с первой входной клеммой логического анализатора,счетный вход двоичного счетчика с исключенным нулевым состод ts яиием соединен с второй входной С клеммой логического анализатора и с первым входом элемента И, второй вход которого соединен с третьей входной клеммой логического анализатора, а выход элемента И соединен с входом синхронизации регистра. фиг. 1

союз сОВЕтских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (1}) 315g Н 03 К 13/32

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3461928/18-21 (22) 01.07.82 (46) 07.05.84. Бюп. Н -17 (72) Э.М.Витенберг, В.И.Луценко, Б.В.Осыка и И.Д.Шварцбанд (71) Научно †производственн объеди нение по радиоэлектронной медицинской аппаратуре (53) 621.294.14 (088.8) (56) 1. "Электроника". 1973, 11 - 23, с. 32, рис. 2,3.

2. "Электроника". 1977, N- 5, с.26, 27,31, рис. 2 (прототип). (54)(57) 1. ЛОГИЧЕСКИЙ АНАЛИЗАТОР, содержащий регистр, сумматор по модулю два, первая группа входов которого соединена с выходами регистра, а выходы сумматора по модулю два соединены с информационными входами регистра, индикатор, соединенный с выходами регистра, о т л и ч а ю— шийся тем, что, с целью сокращения времени диагностики неисправностей цифровых устройств путем локализации однобитовой ошибки, в него вве» дены двоичный счетчик с исключенные нулевым состоянием и элемент И, причем вторая группа входов сумматора по модулю два соединена с выходамй двоичного счетчика с исключенньм нулевым состоянием, вход начальной установки двоичного счетчика с исключенным нулевым состоянием и вход установки нуля регистра соединены с первой входной клеммой логического анализатора, счетный вход двоичного счетчика с исключенным нулевым состо- яиием соединен с второй входной

Ю клеммой логического анализатора и с первым входом элемента И, второй вход которого соединен с третьей входной клеммой логического анализатора, а выход элемента И соединен с входом синхронизации регистра.

1091339 стоянием.

5 !

15

ЗО

2. Анализатор по п. 1, о т л и— ч а ю шийся тем, что двоичный счетчик с исключенным нулевым состоянием содержит три элемента И-НЕ, двоичный счетчик и счетный триггер„ причем счетный входы двоичного счет« чика и счетного триггера соединены соответственно с выходами первого и второго элементов И-НЕ, входы установки нуля двоичного счетчика и установки единицы счетного триггера соединены с входом начальной установки двоичного счетчика с исключенным нулевым состоянием, выходы двоичИзобретение относится к цифровой технике и может быть применено для наладки, ремонта, контроля цифровых устройств (например ЭВМ, микропроцессорных систем и др.).

Известен логический анализатор, содержащий схемы сравнения, индика " торы и позволяющий сравнивать проверяемую последовательность с эталонной (I) .

Недостатком данного логического анализатора является необходимость в источнике эталонных сигналов.

Наиболее близким к предлагаемому является логический анализатор, со-: держащий регистр, сумматор по модулю два, первая группа входов которого соединена с выходами регистра, а выход сумматора по модулю два — с информационным входом регистра, индикатор, соединенный с выходами регистра, причем проверяемая последовательность поступает на вторую группу входов сумматора по модулю два. Дан ный логический анализатор позволяет обнаружить однобитовую ошибку в последовательности любой длины и двухбитовую ошибку в последовательности, цлина которой меньше 2, где r— число разрядов регистра (2) .

Однако логический анализатор не позволяет локализовать ошибку, т.е. указать ошибочный разряд последовательности, что имеет важное значение для диагностики неисправностей, особенно в схемах запоминающих устройств.,ного счетчика и счетного триггера соединены с входами третьего элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, выход счетного триггера соединен с первым входом первого элемента И-НЕ, а вторые входы первого и второго элементов И-НŠ— со счетным входом двоичного счетчика с исключенным нулевым состоянием, выходы двоичного счетчика и счетного тоиггеоа яв- ляются выходами двоичного счетчика с исключенным нулевым соЦель изобретения — сокращение времени диагностики неисправностей цифровых устройств путем локализации однобитовой ошибки.

Поставленная цель достигается тем, что в логический анализатор, содержащий регистр, сумматор по модулю два, первая группа входов которого соединена с выходами регистра, а выходы сумматора по модулю два соединены с информационными входами регистра, индикатор, соединенный с выходами регистра, дополнительно введены дво-. ,ичный счетчик с исключенным нулевым состоянием и элемент И, причем вторая группа входов сумматора по модулю два соединена с выходами двоичного счетчика с исключенным нулевым состоянием, вход начальной установки двоичного счетчика с исключенным нулевым состоянием и вход установки нуля регистра соединены с первой входной клеммой логического анализатора, счетный вход двоичного счетчика с исключенным нулевым состоянием соединен с второй входной клеммой логического анализатора и с первым входом элемента И, второй вход которого соединен с третьей входной клеммой логического анализатора, а выход элемента И соединен с входом синхронизации регистра.

Двоичный счетчик с исключенным нулевым состоянием содержит три эле,мента И-НЕ, двоичный счетчик и "".÷åò

З5 ныи триггер, причем счетные входы

10913 двоичного счетчика и счетного триггера соединены соответственно с выхода- ми первого и второго элементов И-НЕ, входы установки нуля двоичного счетчика и установки единицы счетного триггера соединены с входом начальной установки двоичного счетчика с исключенным нулевым состоянием, выходы двоичного счетчика и счетного триггера соединены с входами третьего 1О элемента И- IE, выход которого соединен с первым входом второго элемента

И-НЕ, выход счетного триггера соединен с первым входом первого элемента

И-НЕ, а вторые входы первого и вто- 15 рого элементов И-HE — со счетным входом двоичного счетчика с исключенным нулевым состоянием, выходы двоичного счетчика и счетного триггера являются выходами двоичного счетчика с исключенным нулевым состоянием.

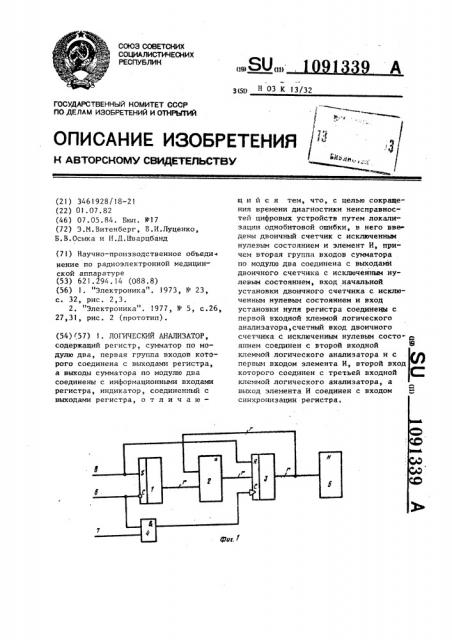

На фиг.1 приведена функциональная схема предлагаемого логического анализатора; на фиг.2 — вариант ре- . ализации двоичного счетчика с исклю-. ченным нулевым состоянием.

Логический анализатор содержит двоичный счетчик 1 с исключенным нулевым состоянием, сумматор 2 по мо ЗО дулю два, регистр 3, элемент И 4 и индикатор 5, входные клеммы 6 — 8, элементы И-HE 9,10 и 11, двоичный счетчик 12 и счетный триггер 13.

Входы начальной установки счетчи35 ка 1 с исключенным нулевым состоянием н регистра 3 соединены с первой входной клеммой 8. Счетный вход счетчика 1 с исключенным нулевым состоянием и первый вход элемента И 4 соединены с второй входной клеямой

6, на которую поступают синхроимпульсы. Второй вход элемента И 4 соединен с третьей входной клеммой 7, на которую поступает цифровая последова" 45 тельность. Выходы счетчика 1 с исключенным нулевым состоянием соединены с второй группой входов сумматора 2, первая группа входов которого соединена с входами индикатора 5 и выходами регистра 3, при этом инфор50 мационные входы последнего соединены с выходами сумматора 2, а вход синхронизации — с выходом элемента И 4.

39 4 двоичного счетчика 12 и установки

1 единицы счетного триггера 13 соеди.нены с входом начальной .установки двоичного счетчика 1 с исключенным нулевым состоянием, выходы двоичного счетчика 12 н счетного триггера l3 соединены с входами элемента И-НЕ 11, выход которого соединен с первым вхо дом элемента И-HE 10, выход счетного триггера 13 соединен с первым входом элемента И-НЕ 9, а вторые входы элементов И-НЕ 9 и 10 соединены со счетно входом двоичного счетчика 1 с исключенным нулевым состоянием, выходами которого являются выходы

14 и 15.

Логический анализатор работает следующим образом (фиг.1).

Перед началом работы импульсом с входной клеммы 8 счетчик 1 устанавливают в состояние 1. Проверяемую последовательность подают на входную клемму 7, на входную клемму 6 подают синхроимпульсы, синхронизирующие каждый разряд последовательности.

По переднему фронту синхроимпульса происходит запись в регистр 3, а по . заднему фронту синхроимпулвса — переключения счетчика 1. Состояние на выходе регистра опишется уравнением

К

p(с 1 = E. ж; и (1) (=1 где к — длина последовательности; ф.; — значение i-го разряда последовательности,, Е (0,1 ;

h — состояние счетчика.на д-и шаге;

h; = ддля ic2, h, 0 {2)

Суммирование здесь и ниже производится по модулю два.

Последовательность с ошибками можно представить, в виде где е — последовательность, содерлщ11 I1

Ф щая 0 в правильных разрядах и "1" в разрядах, где произошла ошибка.

Тогда воспользовавшись линейностью операции (1) можно записать к к

p(g, ) =Е.(g;+ e,)h,=P(c) K и;, (Ъ)

1=1 1" 1

Счетные входы двоичного счетчика 55

12 и счетного триггера 13 соединены соответственно с выходами элементов .

И-НЕ, 9 и 10, входы установки нуля где суммирование происходит по индексам i, равным номерам разрядов с ошибками.

109!339

Из формул (2) и (3) вытекают следующие выводы: любая однобитовая ошибка будет обнаружена, причем для последовательностей с к (2 получим где f †-,, номер разряда с ошибкой; для к а 2 любая двухбитовая ошибка будет обнаружена (i< + i2 4 О). . 10

Возможность локализации однобитовой ошибки (т.е. указания ошибочного разряда последовательности) обеспечивается тем, что состояния двоичного счетчика 1 с исключенным I5 нулевым состоянием соответствуют номерам разрядов контролируемой логической последовательности. При этом в регистре 3 записана двоичная сумма по модулю два номеров разрядов 20 последовательности, содержащих логи ческую единицу. В случае однобитовой ошибки полученная сумма будет отличаться от правильной на состояние счетчика, соответствующее Моменту 25 ошибки, т.е. при 2, на номер ошибочого разряда. Осуществив сложение по одулю два полученного содержимого егистра 3 с известным правильным, получим номер ошибочного разряда в зо последовательности.

Двоичный счетчик с исключенным нулевым состоянием (фиг.2) работает следующим образом. Перед началом работы импульсом с входной клеммы 8 двоичный счетчик 12 устанавливают в положение "0", а счетный триггер, 13 — в положение "1" (выход 15 играет

Роль младшего разряда двоичного счетчика с исключенным нулевым состоянием). До момента времени, когда . выходы !4 и 15 примут состояние рав" ное 11 ... 11, двоичный счетчик 12 и счетный триггер 13 работают как двоичный счетчик со сквозным переносом второго разряда. После установки выходов 14 и !5 в состояние

11 ... Il выход элемента И-НЕ !I блокирует через элемент И-НЕ 10 счетный вход счетного триггера 13. Следующим синхроимпульсом с входной клеммы 6 через элемент И-НЕ 9 двоичный счетчик 12 перевопится в состояние

00...00, при этом счетный триггер находится в положении "!". и схема устанавливается в исходное состояние

Таким образом осуществляется исключение нулевого состояния двоичного счетчика.

При подключении логического аналн! затора показание индикатора отличается при однобитовой или двухбитовой ошибке от правильного. При одиночной ошибке сумма по модулю два полученного показания индикатора и правильного даст номер ошибочного разряда (при длине последовательности меньше 2 ).

Таким образом, логический акализатор позволяет обнаружить и, кроме того, для последовательностей длиной меньше 2 определить место положения ошибочного бита последовательности, что позволяет ускорить процесс наладки, ремонта и контроля цифровых устройств, например ЭВМ, микропроцессорньп систем и др.

1091339

Составитель И.Катанова

Редактор М.Янович ТехредЛ;Микеш Корректор А.Дэятко аказ 3100/54 Тираж 862 Подписное

МИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва. Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4