Следящий приемник

Иллюстрации

Показать всеРеферат

СЛЕДЯЩИЙ ПРИЕМНИК, содержащий дешифратор, последовательно соедине|нные первый смеситель, вход коTopdro является входом приемника, первый фильтр нижних частот и первый пороговьш детектор, выход которого соединен с первым входом дешифратора , последовательно соединенные фазовращатель на 90., вход которого соединен с входом приемника, второй смеситель, второй фильтр нижних частот и второй пороговый детектор, выход которого соединен с вторым входом дешифратора, последовательно соединенные фильтр-экстраполятор я управляемый генератор, выход которого соединен с гетеродинными входами первого и второго смесителей, последовательно соединенные первый триггер, вход которого соединен с первым выходом дешифратора, первый элемент И, другой вход которого соединен с вторым выходом деши(атора, первый элемент ИЛИ и второй элемент ИЛИ, выход которого соединен с другим Входом первого триггера, последовательно соединенные второй триг-: гер, вход которого соединен с третьим выходом дешифратора, а другой вход соединен с выходом второго эле-мента ИЛИ, второй элемент И, третий элемент ИЛИ, выход которого соединен с другим входом второго элемента ИЛИ, реверсивный счетчик, другой вход которого соединен с выходом первого элемента ИЛИ, и цифро-аналоговый преобразователь, третий элемент И, выход которого соединен с другим входом третьего элемента ИЛИ, четвертый элемент И, выход которого соединен с другим входом первого элемента ИЛИ, отличающийс я тем, что, с целью повышения точности слежения за частотой, межg ду выходом первого фильтра нижних частот и входом фильтра-экстраполятора включены последовательно инвертор , переключатель, другой вход которого соединен с выходом первого 4мльтра нижних частот, а управляющий вход соединен с выходом второго порогового детектора, и сумматор, другой вход которого соединен с выходом цифро-аналогового преобразователя , между вторым выходом дешифратора и входом третьего элемента И, другой вход которого соединен с первым выходом дешифратора, включен третий ,триггер, между четвертым выходом дешифратора и входом четвертого элемента И, другой вход которого соединен с третьим выходом дешифратора, включен четвертый триггер, другие входы третьего и четвертого триггеров соединены с выходом второго элемента 11ЛИ, другой вход второго элемента И соединен с четвертым выходом дешифратора. °

ИЮ (И) СОКИ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3фр П 04 В l/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ. C V

ГООУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3547535/18-09 (22) 26.01,83 (46) 15.05,84, Вюл. К 18 (72) В.Н. Лукин, Ю.А, Гребенко и В,Н. Абросимов (53) 621.396.62(088.8) (56) I. Патент СП1А Ф 3863156, кле Н 04 В l/16 1975

2. Патент США 11 3934(05, кл..Н 04 В I /16, 1976 (прототип). (54)(57) СЛЕДЯЩИЙ ПРИЕМНИК, содержащий,дешифратор, последовательно соединенные первый смеситель, вход которбго является входом приемника, первый фильтр нижних частот и первый пороговыи детектор, выход которого соединен с первым входом дешифратора, последовательно соединенные фазовращатель на 90., вход которого соединен с входом приемника, второй смеситель, второй фильтр нижних частот и второй пороговый детектор, выход которого соединен с вторым входом дешифратора, последовательно соединенные фильтр-экстраполятор и управляемый генератор, выход которого соединен с гетеродинными входами первого и второго смесителей последовательно соединенные первый триггер, вход которого соединен с первым выходом дешифратора, первый элемент И, другой вход которого соединен с вторым выходом дешифратора, первый элемент ИЛИ и второй элемент

ИЛИ, выход которого соединен с другим входом первого триггера, последовательно соединенные второй триг-. гер, вход которого соединен с третьим выходом дешифратора, а другой вход соединен с выходом второго эле-. мента ИПИ, второй элемент И, третий элемент Ш1И, выход которого соеди" нен с другим входом второго элемента ИЛИ, реверсивный счетчик, другой вход которого соединен с выходом первого элемента ИЛИ, и цифро-аналоговый преобразователь, третий элемент И, выход которого соединен с другим входом третьего элемента ИЛИ, четвертый элемент И, выход которого соединен с другим входом первого элемента ИЛИ, о т л и ч а ю щ и йс я тем, что, с целью повышения точности слежения за частотой, между выходом первого фильтра нижних I частот и входом фильтра-экстраполя. тора включены последовательно инвер: тор, переключатель, другой вход кото- рие рого соединен с выходом первого фильтра нижних частот, а управляющий O вход соединен с выходом второго порогового детектора, и сумматор, другой вход которого соединен с выходом цифро-аналогового преобразовате- Ж ля,между вторым выходом дешифратора Ю и входом третьего элемента И, другой 4 вход которого соединен с первым выходом дешифратора, включен третий рффи ,триггер, между четвертым выходом дешифратора и входом четвертого эле" мента И, другой вход которого соединен с третьим выходом дешифратора, включен четвертый триггер, другие входы третьего и четвертого триггеров соединены с выходом второго элемента ИЛИ, другой вход второго элемента И соединен с четвертым выходом дешифратора.

92734

1 0

Изобретение относится к области радиотехники и может быть использовано в радиосвязи и радионавигации.

Известен следящий приемник, содержащий последовательно соединенные антенну, первый смеситель, первый фильтр низкой частоты, первый усилитель-ограничитель, дешифратор, к другому входу которого подключены последовательно подсоединенные к антенне фаэовращатель, второй смеситель, второй фильтр низкой частоты, второй усилитель-ограничитель, а также последовательно соединенные реверсивный счетчик, цифро-аналоговый преобразователь, фильтр-экстраполятор и управляемый генератор, выходом соединенный параллельно с вторыми входами первого и второго смесителей, первый и второй триггеры, первые входы которых соединены с первым и четверть1м входами дешифратора, первый, второй, третий и четвертый элементы И, причем первые входы первого и второго элемента И подключены параллельно к выходу первого триггера, вторые входы третьего и четвертого элементов И подключены параллельно к выходу четвертого элемента И, соединены параллельно .с вторым выходом дешифратора, а второй вход второго элемента И и пер-, вый вход третьего элемента И соединены параллельно с третьим выходом дешифратора, первый элемент ИЛИ, иодсоединенный своими входами к выходам первого и третьего элементов

И, второй элемент ИЛИ, подсоединенный к выходам второго и четвертого . элементов И, третий элемент ИЛИ, подсоединенный входами к выходам первого и второго элемента ИЛИ и соответственно к вычитающим и суммирующим входам реверсивного счетчика, а выходом к вторым входам триггеров Pl ).

Однако данный приемник отличает-.. ся недостаточной точностью слежения, Наиболее близким по технической сущности к предложенному является следящий приемник, содержащий дешифратор, последовательно соединенные первый смеситель, вход которого является входом приемника, первый фильтр нижних частот и первый пороговый детектор, выход которого соединен с первым входом дешифратора, последовательно соединенные фазовра(Ъ щатель на 90, вход которого соединен с входом приемника, второй смеситель, второй фильтр нижних частот и второй пороговый детектор, выход которого соединен с вторым входом дешифратора, последовательно соединенные фильтр-экстраполятор и управляемый генератор, выход которого соединен с гетеродинными входами первого и второго смесителей, последовательно соединенные первый триггер, вход которого соединен с первым выходом дешифратора, первый элемент И, другой вход которого соединен с вторым выходом дешифратора, первый элемент ИЛИ и второй элемент ИЛИ, выход которого соединен с другим входом первого триггера, последовательно соединенные второй триггер, вход которого соединен с третьим выходом дешифратора, а другой вход соединен с выходом второго элемен- та ИЛИ, второй элемент И, третий элемент ИЛИ, выход которого соединен с другим входом второго элемента ИЛИ, реверсивный счетчик, другой вход которого соединен с выходом первого элемента ИЛИ, и цифро-аналоговый преобразователь, третий элемент И, выход которого соединен с другим входом третьего элемента

ИЛИ, четвертый элемент И, выход которого соединен с другим входом первого элемента ИЛИ (2 ).

Однако известное устройство имеет недостаточную точность (порядка

35 нескольких десятков градусов), что обусловлено ступенчатым характером регулирования в процессе слежения при переходе от квадранта к квадран40 ту и наличием Гистерезиса при изменении знака частотной расстройки.

Цель изобретения — повышение точности слежения за частотой.

Поставленная цель достигается

45 тем что в следящем приемнике соЭ держащем дешифратор, последователь-, но соединенные первый смеситель, вход которого является входом приемника, первый фильтр нижних частот

50 и первый пороговый детектор, выход которого соединен с первым входом дешифратора, последовательно соединенные фазовращатель на 90, вход которого соединен с входом приемни55 ка, второй смеситель, второй фильтр нижних частот и второй пороговый детектор, выход которого соединен с вторым входом дешифратора, последовательно соединенные фильтр-экстрапо1092734 4 лятор и управляемый генератор, выход которого соединен с гетеродинными входами первого и второго смесителей, последовательно соединенные первый триггер, вход которого соединен с первым выходом дешифратора, первый элемент И, другой вход которого соединен с вторым выходом дешифратора, первый .элемент ИЛИ и второй элемент ИЛИ, выход которого соединен с другим входом первого триггера, последовательно соединенные второй триггер, вход которого соединен с третьим выходом дешифратора, а дру гой вход соединен с выходом второго элемента ИЛИ, второй элемент И, третий элемент ИЛИ, выход которого соединен с другим входом второго эле-. мента ИЗП1, реверсивный счетчик, другой вход которого соединен с выходом первого элемента ИЛИ, и цифроаналоговый преобразователь, третий элемент И, выход которого соединен с другим входом третьего элемента

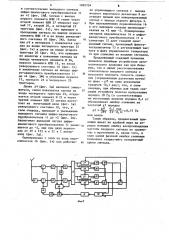

ИЛИ, четвертый элемент И, выход которого соединен с другим входом первого элемента ИЛИ, между выходом первого фильтра нижних частот и входом фильтра-экстраполятора включены последовательно инвертор, переключатель, другой вход которого соединен с выходом первого фильтра нижних частот, а управляющий вход соединен с выходом второго порогового детектора, и сумматор, другой вход которого соединен с выходом цифроаналогового преобразователя, между вторым выходом дешифратора и входом третьего элемента И, другой вход которого соединен с первым выходом дешифратора, включен третий триггер, между четвертым выходом дешифратора и входом четвертого элемента И, другой вход которого соединен с третьим выходом дешифратора, включен четвертый триггер, другие входы третьего и четвертого триггеров соединены с выходом второго элемента ИЛИ, другой вход второго элемента И соединен с четвертым выходом дешифратора, На фиг. 1 представлена структурная схема предложенного следящего приемника; на фиг ° 2 — диаграммы нап»»яжений, поясняющие работу следящего приемника.

Следящий приемник содержит антенну 1, первый смеситель 2, первый фильтр 3 нижних частот, первый пороговый детектор 4, дешифратор 5, . фазовращатель 6 на 90»», второй смеситель 7, второй филь»р 8 нижних частот, второй пороговый детектор 9, реверсивный счетчик 10, цифро-аналоговый преобразователь 11, сумматор 12, фильтр-экстраполятор 13 управляемый генератор 14, инвертор

15, переключатель 16, первый триггер !7, первый элемент И 18, первый элемент.ИЛИ 19, второй триггер 20, второй элемент И 21, третий элемент

ИЛИ 22, третий триггер 23, третий элемент И 24, четвертый триггер 25, четвертый элемент И 26, второй элемент ИЛИ 27.

Следящий приемник работает следующим образом.

С поступлением входного сигнала на антенну 1 на входе первого фильт5 !

О !

5 ра 3 появляется сигнал, пропорцио?0i нальный синусу разности фаз (фазовое рассогласование) а» входного сигнала и сигнала управляемого генератора 14. На выходе второго фильтра 8 появляется сигнал, про?5 же сигнал проходит через первый элемент И 18, поскольку первым триггером 17 запомнен сигнал предыдущего интервала III, Сигнал с выхода первого элемента И 18 поступает через первый элемент ИЛИ !9 на суммирую55 щий вход реверсивного счетчика 10 (фиг. 2K), увеличивая его состояние порциональный косинусу этой разности фаз а . При работе устройства аФ может меняться произвольным образом, например, так, как показано на

50 фиг, 2а. Разность фаза»»". последовательно проходит четыре квадранта цикла фазового рассогласования, обозначенные на фиг. 2 I II III

IV соответственно для интервалов

35 от — j» до /2; от — l»/2 до 0; от

0 до Ti /2; от J(/2 до Т .

В результате выходные сигналы первого 3 н второго 8 фильтров при прохождении соответственно через

40 первый 4 и второй 9 пороговые детекторы, дешифратор 5, вызывают только один сигнал с потенциалом логической единицы на одном из четырех выходов дешифратора 5.

45 При ь», находящемся в интервале ХХХ (фиг, 2а), появляется сигнал на входе первого триггера 17 и устанавливает его в "1" (фиг.2ф}. . При дальнейшем изменении аЧ в Ху интервале появляется сигнал на входе третьего триггера 23 (фиг, 2ф, этот

1092734

30 и соответственно выходного сигнала цифро-аналогового преобразователя ll до +2 (фиг. 2bj1. Сигнал с выхода первого элемента ИЛИ !9 также через второй .элемент ИЛИ 27 обнуляет пер- 5 вый !7, второй 20, и четвертый 25 триггеры (фиг..23), что приводит к пропаданию сигнала на выходе первого элемента ИЛИ 19 и на входе реверсивного счетчика 10 (фиг. Зк). Затем при dV в интервале 1 появляется сигнал на входе четвертого триггера 25 (фиг. Зк) и далее на входе второго триггера 20 (фиг. 3s), что приводит по аналогии к появлению сигнала на выходе четвертого элемента И 26, первого элемента ИЛИ 19, на входе реверсивного счетчика 10 {фиг. 3 к) и увеличению сигнала на выходе цнфро-аналогового преобразователя ll 20 до +4 (фиг. Зй) и обнулению первого

17>. третьего 23 и четвертого 25 триггеров.

Далее d9 (фиг. За) начинает уменьшаться, снова появляется сигнал на входе четвертого триггера 25, открывается второй элемент И 21 и через третий элемент ИЛИ 22 сигнал поступает иа вычитающий вход (фиг. З ) реверсивного счетчика 10, что, в, свою очередь, приводит к уменьшению выходного сигнала цифро-аналогового преобразователя ll до +2 (фиг. 2м).

Аналогично выходной сигнал цифроаналогового преобразователя 1! умень- З5 шается до -2, еще при двух переходах от IV к Ш и к П. к Х интервалу (Фиг. 3 !).

Одновременно с этим на вход переключателя 16 (фиг. Зи) под действн- 40 ем управляющего сигнала с выхода второго порогового детектора 9 поступает прямой или инвертированный сигнал с выхода первого фильтра 3.

При переключениях переключателя 16 в его выходном сигнале происходят"скачки на +2 или -2. Суммирование сигналов переключателя 16 и цифроаналогового преобразователя 11 в сумматоре 12 дает гладкий однозначный сигнал, проходящий фильтрэкстраполятор 13 и регулирующий час-. тоту и фазу управляемого генератора

14 при слежении за входным сигналом, Предложенный следящий приемник является линейным устройством автоматического слежения как при больших, так и малых рассогласованиях относительно входного сигнала и позволяет получить точность слежения (определенную расчетным путем) по фазе - d9 не хуже нескольких градусов (О,! рад 1, что, в свою очередь, при обычных для таких следящих устройств полосах пропускания порядка !О Гц (и соответствующих им постоянных времени порядка О,! с обеспечивает ошибку слежения, за частотой дf порядка

0,! рад аю = — — —,—,.-«о,}5 гц или менее, Таким образом, предлагаемый приемник имеет по крайней мере ка порядок меньшую ошибку воспроизведения частоты входного сигнала по сравнению с прототипом и, кроме того, в силу малой фазовой ошибки слежения позволяет осуществить когерентный прием сигнала.

1092734

5 Я!7и

Составитель Н, Мельников

Редактор О. Колесникова Техред C. ryHosa Корректор,Г. Огар

Заказ 3277/44

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 Ю

Ф йс

Ж оКы е/барс с елжи

Тираж 635 Подписное

ВН1ЖПИ Государственного комитета,CCСP по делам изобретений и открытий

113035, Москва, )l(-35, Раушская наб., д. 4/5