Устройство для автоматического выявления ошибок дискретного канала связи

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ВЫЯВЛЕНИЯ ОШИБОК ДИСКРЕТНОГО КАНАЛА СВЯЗИ, содержащее основной и дополнительный регистры сдвига, динамический триггер, дешифратор, инвертор , первый, второй и третий блоки совпадения, счетчик импульсов и блок сравнения, первый вход которого соединен со входом записи основного регистра сдвига с сумматором в цепи обратной связи, а -выход динамического триггера соединен с первым входом сдвига основного регистра сдвига, отличающееся тем, что, с целью.повышения точности выявления ошибок путем сокращения времени обнаружения и устранения сбоя фазы по циклу, введены дополнительный счетчик импульсов, счетчик фазы и триггер режима, при этом выход первогоблока совпадения соединен со входом записи дополнительного регистра сдвига и с выходом второго блока совпадения, второй вход блока сравнения соединен с выходом первого разряда дополнителы ного регистра сдвига, выход которого , соединен с первым входом второго блока совпадения, второй вход которого соединен с выходом инвертора, вход которого соединен с первым входом первого блока совпадения, с входом сброса дополнительного счетчика импульсов, с входом сброса счетчика фазы, с входом сброса триггера режима, с первым i входом сдвига дополнительного регистра сдвига, со вторым входом сдвиг основного регистра сдвига и с входом г установки динамического триггера, вы (Л ход которого соединен со вторым вхо ,дом сдвига дополнительного регистра с сдвига и со счетным входом дополнительного счетчика импульсов, выход которого соединен с третьим входом сдвига основного регистра сдвига, с входом сброса счетчика импульсов, с вхсэдом установки триггера режима и со счетным входом счетчика фазы, выход которого соединен с входом сброса ди намического триггера, с выходом триге гера режима и с первым входом третьего блока совпадения, второй вход которого соединен со счетным входом счетчика импульсов и с выходом блока сравнения, а выходы основного регистра сдвига соединены с соответствующими входами дешифратора , выход которого соединен со входом записи основного регистра сдвига.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) 01) (д) Н 04 В 3/46

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ у«3

MhJi Q f )ЯД

Н АВТОРСКОМ У СВИДЕТЕЛЬСТВУ! (21) 3533465/IS-О9 (22) 06.01.83 (46) 15.05,84. Бап. 11р IS (72) Б.Е.Аксенов, М.В.Гаазе и В.И.Дмитриев (71) Ленинградский ордена Ленина политехнический институт им. М,И.Калинина (53) 621.395.664 (088.8) (56) 1. Авторское свидетельство СССР

N- 429543, кл. Н 04 В 3/46, 1972.

2. Авторское свидетельство СССР

11 740463, кл. Н 04 В 3/46, 1978, 3, Авторское свидетельство СССР

N 535743, кл. Н 04 В 3/46, 1974 (прототип). (54) (57) УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ВЬИВЛЕНИЯ ОШИБОК ДИСКРЕТНОГО

КАНАЛА СВЯЗИ, содержащее основной и дополнительный регистры сдвига, динамический триггер, дешифратор, инвертор, первый, второй и третий блоки совпадения, счетчик импульсов и блок сравнения, первый вход которого соединен со входом записи основного регистра сдвига с сумматором в цепи обратной связи, а .выход динамического триггера соединен с первым входом сдвига основного регистра сдвига, < о т л и ч а ю щ е е с я тем, что, с целью повышения точности выявления ошибок путем сокращения времени обнаружения и устранения сбоя фазы по циклу, введены дополнительный счетчик импульсов, счетчик фазы и триггер режима, при этом выход первого блока совпадения соединен со входом записи дополнительного регистра сдвига и с выходом второго блока совпадения, второй вход блока сравнения соединен

j с выходом первого разряда дополнителы ного регистра сдвига, выход которого, соединен с первым входом второго блока совпадения, второй вход которого соединен с выходом инвертора, вход которого соединен с первым входом первого блока совпадения, с входом сброса дополнительного счетчика импульсов, с входом сброса счетчика фазы, с вхо дом сброса триггера режима, с первым входом сдвига дополнительного регистра сдвига, со вторым входом сдвига основного регистра сдвига и с входом д установки динамического триггера, вы" Е ход которого соединен со вторым вхо,дом сдвига дополнительного регистра сдвига и со счетным входом дополнительного-счетчика импульсов выход

O которого соединен с третьим входом . сдвига основного регистра сдвига, с входом сброса счетчика импульсов, с входом установки триггера режима и со счетйым входом счетчика фазы, выход которого соединен с входом сброса ди-.. намического триггера, с выходом триго гера режима и с первым входом третьего блока совпадения, второй вход кото рого соединен со счетным входом счетчика импульсов и с выходом блока сравнения, а выходы основного регистра сдвига соединены с соотватствуивими входами давифра- ЬВ тора, выход которого соединен со входом записи ocHoBHoI регистра сдвига.

1092738

Изобретение относится к электросвяе зи и может использоваться, в контрольно-измерительной связной аппаратуре и аппаратуре передачи данных.

Известно устройство для автоматического выявления ошибок дискретного канала связи,содержащее основной ре" гистр сдвига и дополнительный регистр сдвига, выходы которого соединены со входамн дешнфратора, инвертор, блок 10 совпадения, счетчик импульсов и блок сравнения, первый вход которого соединен со входом записи основного регистра сдвига с сумматором в цепи обрат-. ной связи (1 ) . 15

Недостатком этого устройства явля ется невысокая точность выявления ошибок из-за длительного обнаружения и устранения сбоя фазы по циклу.

Известно также устройство для ав- 20 томатического выявления ошибок дискретного канала связи, содержащее основной и дополнительный регистры сдвига, инвертор, блоки совйадения, дешифратор,счетчик импульсов и блок срав- 25 кения, первый вход которого соединен со входом записи основного регистра " сдвига с сумматором в цепи обратной связи (2 3 .

Недостатком этого устройства также 30 является невысокая точность выявления ошибок из-за осуществления цикловой синхронизации по зачетному интервалу.

Наиболее близким к изобретению по технической сущности является устройе 35 ство для автоматического выявления ошибок дискретного канала связи,,содержащее основной и дополнительный регистры сдвига, динамический триггер, дешифратор, инвертор, первый, второй 40 н третий блоки с6впадення, счетчик импульсов и блок сравнения, первый вход которого соединен со входом записи основного регистра сдвига с сумматором в цепи обратной связи, а выход динамического триггера соединен с первым входом сдвига основного регистра сдвига ГЗ 1 .

Однако зто устройство не обеспечивает высокой достоверности выявлеяия.ошибок и достаточно быстрого устранения сбоя фазы по циклу в каналах низI кого качества (при средней вероятности ошибки на символ 10 " ) . В каналах . такого качества вероятность появления

20-60 символов подряд беэ ошибки мала и, следовательно, известное устройство, осуществляющее синхронизацию по циклам по зачетному интервалу, б уде т дават ь недостоверные данные. Кроме того, известное устройство не определяет количественно величину сбоя фазы IIo циклу, т.е ° на сколько тактов разошлась принимаемая последовательность относительно передаваемой.

Цель изобретения — повышение точности выявления ошибок путем сокращения времени автоматического обнаружения и устранения сбоя фазы по циклу.

Цель достигается тем, что в устройство для автоматического выявления ошибок дискретного канала связи, содержащее основной н дополнительный регистры сдвига, динамический триггер, дешифратор, инвертор, первый, второй и третий блоки совпадения, счетчик импульсов и блок сравнения, первый вход которого соединен со входом записи основного регистра сдвига с сумматором в цепи обратной связи, а выход, динамического триггера соединен с первым входом сдвига основного регист-. ра сдвига, введены дополнительный счетчик импульсов, счетчик фазы и триггер режима, при этом выход первого блока совпадения соединен со входом записи дополнительного регистра сдвига и с выходом второго блока совпаде-. ния, второй вход блока сравнения соединен с выходом первого разряда дополнительного регистра сдвига, выход которого соединен с первым входом второго блока совпадения, второй вход которого соединен с выходом инвертора, вход которого соединен с первым входом первого блока совпадения, с входом сброса дополнительного счетчика импульсов, с входом сброса счетчика фазы, с входом сброса триггера режима, с первым входом сдвига дополнительного регистра сдвига, со вторым входом сдвига основного регистра сдвига и входом установки динамического триггера, выход которого соединен со вторым входом сдвига дополнительного регистра сдвига и со счетным входом дополнительного счетчика импульсов, выход которого соединен с третьим входом сдвига основного регистра сдвига, с входом сброса счетчика импульсов, с входом установки триггера режима и счетным входом счетчика фазы, выход которого соединен со входом сброса динамического триггера, с выходом триггера режима и с первым входом третьего блока совпадения, второй вход которого соединен со счетным входом счетчика импульсов и с выходом

3 10927 блока сравнения, а выходы основного регистра сдвига соединены с соответствующими входами дешифратора, выход которого соединен со входом записи основного регистра сдвига.

Принцип действия устройства основан на корреляционных свойствах mпоследовательностей, используемых в качестве тестовых псевдослучайных последовательностей при исследованиях1О дискретных каналов связи.

Устройство при приеме каждого очередного символа производит сравнение принимаемой из канала последовательности из очередных N символов (где

N — - длина периода,. m-последователь-. ности) с N фазами эталонной последовательности, т,е, вычисляется корреляционная функция между приходящей последовательностью и N фазами эталонной последовательности и по максиI муму этой функции определяют верную фазу. Таким образом сбой по фазе может быть устранен эа время прихода одного . символа в канале очень низкого качества.24

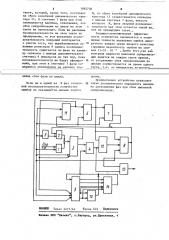

На чертеже приведена структурная электрическая схема устройства.

Устройство для автоматического выявления ошибок дискретного канала связи содержит первый и второй блоки

1 и 2 совпадения, дополнительный ре-

-.,30 гистр 3 сдвига, блок 4 сравнения, инвертор 5, дополнительный счетчик 6 импульсов, счетчик 7 фазы, триггер 8 режима, основной регистр 9 сдвига, сумматор 10, динамический триггер 11,З5 счетчик 12 импульсов, третий блок 13 совпадения и дешифратор 14.

Устройство работает следующим образом. двоичная последовательнссть иэ ди-40 скретного канала связи через первый блок 1 совпадения поступает на вход дополнительного регистра 3.сдвига, на второй вход первого блока 1 совпа- дения поступает тактовая последовательность из дискретного канала связи, которая также осуществляет начальную установку схемы фаэирования, а именно сдвиг основного и дополнительного регистров 9 и 3 сдвига, запуск динамического триггера 11, сброс додополнительного счетчика 6 импульсов и счетчика 7 фазы, сброс триггера 8 режима, После окончания тактового mr, пульса дополнительный регистр 3 сдви-55 га замкнут . в кольцо" через второй блок 2 совпадения, на второй вход которого поступает тактовая последова38 4 тельность через инвертор 5, .

Сигнал с младших разрядов основного и дополнительного регистров 9 и

3 сдвига поступает на входы блока 4 сравнений, с выхода которого выявленные ошибочные символы поступают на вход счетчика 12 импульсов, а также на выход из устройства для регистрации через третий блок 13 совпадения, на второй вход которого поступает сигнал с выхода триггера 8 режима, означающий завершение процесса фазирования на данном такте.

Для повышения точности выявления ошибок дискретного канала связи необходимо исключить такое состояние основного регистра 9 сдвига, при кот „. тором все его разряды равны нулю, так как при этом регистр сдвига не вырабатывает последовательность, Поэтому выходы разрядов основного регистра 9 сдвига подключены к входам дешифратора 14, который реагирует на запрещенное состояние и устанавливает первый разряд основного регистра 9 сдвига в единицу.

Автоматическое вычисление величины сбоя фазы по циклу между поступающей иэ канала двоичной последовательностью и последовательностью, вырабатываемой основным регистром 9 сдвига, и устранение этого сбоя осуществляется спедующим образом.

Последовательность импульсов с выхода динамического триггера 11 поступает на входы сдвига основного и вспомогательного регистров 9 и 3 сдвига, а также подсчитывается допол»: нительным счетчиком 6 импульсов емкостью N. Количество несовпадений с выхода блока 4 сравнения подсчитывается счетчиком 12 импульсов, имею-.: щим пороговый элемент на выходе. Сигнал на выходе счетчика 12 импульсов появляется в том случае, если количество несовпадений меньше некоторого порога М, т.е. последовательности сфазированы. После окончания Н сдви-. гов сигнал с выхода дополнительного счетчика 6 импульсов осуществляет запись информации с выхода счетчика

12 импульсов в триггер 8 режима, осуществляет сброс счетчика 12 импульсов и поступает на вход счетчика 7 фазы.

В случае отсутствия сбоя фазы по циклу появляется сигнал на выходе триггера 8 режима,.означающий завершение процесса фазирования на данном

109273 такте, который, кроме того, поступает на сброс колебаний динамического триггера 11. В счетчике 7 фазы при этом записывается единица, означающая, что сбоя синхройизации по циклу на этом 5 такте не происходит. Если же двоичные последовательности на этом такте не .сфазированы, то вся указанная последовательность операций повторяется с учетом того, что вырабатываемая ос- 10 .новным регистром 9 сдвига последовательность сдвигается по фазе на единицу сигналом,с выхода дополнительного счетчика 6 импульсов до тех пор, пока последовательности не будут сфазированы, при этом в счетчике 7 фазы содер тсяузеличенное на е иниич знаi время.

Предлагаемое устройство позволяет

20 также дополнительно определять величину расхождения фаз при сбое цикловой синхронизации.

ВИИИПИ Заказ 3277/44 Тираж 635 - Подписное

Филнвл ППП "Патент", г Ужгород, ул.Проектная, 4 чение сбоя фазы по циклу.

Если ни в одной из М фаз эталонной последовательности количество ошибок не оказывается меньше порога

8 6

М, то сброс колебаний динамического триггера 11 осуществляется сигналом с выхода счетчика 7 фазы, емкость которого N фаза опорной последовательности при этом остается такой же, как на предыдущем такте..

Технико-экономическая эффективность устройства заключается в повышении точности выявления ошибок диск" ретного канала связи низкого качества (средняя вероятность ошибки на символ (1-3) 10 " „ Кроме того,так как контроль верности цикловой синхрониза- ции ведется на каждом такте приема, то устранение сбоя синхронизации по циклам осуществляется эа время одного такта, т е. за минимальна яочможтт