Одноканальное устройство для управления @ -фазным преобразователем

Иллюстрации

Показать всеРеферат

ОДНОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ fn -ФАЗНЫМ ПРЕОБРАЗОВАТЕЛЕМ по авт.св. № 775855, отличающееся тем, что, с. целью повышения надежности, оно снабжено блоком контроля, содержащим два D - триггера, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, входы которого подключены к выходу соответствующего элементна ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход каждого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен С. прямым выходом соответствующегоD триггера , второй вход - с выходом логического ключа, тактовьй вход)-триггера соединен с выходом счетчика импульсов , а информационный вход подS ключен к прямому выходу последнего D-триггера регистра сдвига. (П У1 :o

ЩЮЭ СОВЕТСНИХ

«««

РЕСПУБЛИН

«9) SU (n) gyp Н 02 P 13 16

Q (61) 775855 (21) 3516145/24-07 (22) 30.11.82 (46) 30.05.84. Бюл. 9 20 (72) А.Г. Азаров, С.И. Королев, В.В. Полонский и Г.И. Цветков (71) Научно-исследовательский институт автоматики и электромеханики при Томском институте автоматизированных систем управления и радиоэлектроники (53) 621.316.727(088.8) (56) 1. Авторское свидетельство СССР

У 775855, кл, Н 02 P 13/ 16, 1978. (54)(57) ОДНОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ

УПРАВЛЕНИЯ 1п -ФАЗНЬК ПРЕОБРАЗОВАТЕЛЕМ ч по авт.св. к 775855, о т л и ч а ющ е е с я тем, что, с целью повыщения надежности, оно снабжено блоком контроля, содержащим два 3 -триггера, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, входы которого подключены к выходу соответствующего элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход каждого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с прямым выходом соответствующегоР триггера, второй вход — с выходом ло- ., гического ключа, тактовый входР -триггера соединен с выходом счетчика импульсов, а информационный вход подключен к прямому выходу последнего

«

Э-триггера регистра сдвига.

1095341

Изобретение относится к электротехнике, а именно к системам управления статическими преобразователями.

По основному авт.св. У 775855 известно одноканальное устройство для управлениями -фазным преобразователем, содержащее последовательно соединенные формирователь синхронизирующих импульсов, блок фазовой автоподст!

О ройки частоты, генератор треугольного напряжения и блок сравнения, а также два логических ключа и два фазорасщепителя. Блок фазовой автоподстройки частоты содержит соединенные в кольцо фазовый детектор, преобра15 зователь длительности импульсов в напряжение, управляемый генератор и делитель частоты, выполненный в виде кольцевого регистра сдвига на 2 и триггерах (и = 1,2,3,...). Каждый

20 фазорасщепитель содержит два формирователя коротких импульсов, входы которых подключены к прямому и инверсному выходам логического ключа, элемент ИЛИ, счетчик импульсов и последовательный регистр сдвига из (rrr-1)D -триггеров, тактовый вход которого соединен с выходом счетчика, 1информационный вход подключен к

30 прямому выходу логического ключа, а управляющие входы объединены со входами элемента ИЛИ и подключены к выходам формирователей коротких импульсов. Выход элемента ИЛИ соединен со входом установки счетчика импульсов, счетный вход которого подключен к выходу управляемого генератора.

Прямой выход блока сравнения подключен к тактовому входу первого логического ключа, управляющие входы которо; 411

ro соединены с выходами первого триггера делителя частоты. Инверсный выход блока сравнения подключен к тактовому входу второго логического ключа, управляющие входы которого соеди- 45 иены с выходами (П+1)-ro триггера делителя частоты.(< ..

Недостаток устройства — невысокая надежность, обусловленная отсутствием контроля правильности работы. Сбои в работе устройства, вызванные неисправностью его узлов или импульсными помехами. приводят к искажению величины и формы выходного напряжения пре55 образователя, что недопустимо для ответственных потребителей.

Целью изобретения является повышение надежности работы устройства путем контроля правильности его работы °

Поставленная цель достигается тем, что одноканальное устройство для управления й)-фазным преобразователем снабжено блоком контроля, содержащим два3 -триггера, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, входы которого подключены к выходу соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход каждого элемента ИСКЛЮЧА10ЩЕЕ ИЛИ соединен с прямым выходом соответствующегo2 -триггера, второй вход — с выходом логического ключа, тактовый входР -триггера соединен с выходом счетчика импульсов, а информационный вход его подключен к прямому выходу последнего2 -триггера регистра сдвига.

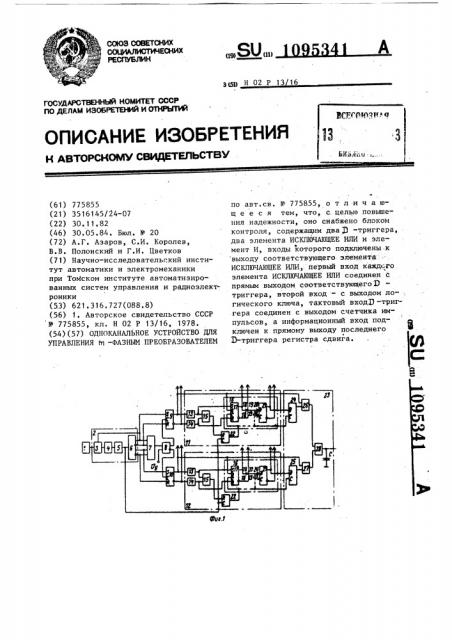

На фиг.1 представлена схема устройства для управления rrr-фазным преобразователем, где rn= 6; на фиг.2— диаграммы, поясняющие работу устройства.

Устройство содержит последовательно соединенные формирователь 1 синхронизирующих импульсов, блок 2 фазовой автоподстройки, содержащий соединенные в кольцо фазовый детектор 3, преобразователь 4 длительности импульсов в напряжение, управляемый генератор 5 и делитель частоты 6, выполненный в виде кольцевого регистра сдвига на 2 g триггерах (=1,2,3,...), формирователь треугольного напряжения

7 и элемент сравнения 8, а также два логических ключа 9 и 10, два фазо,расщепителя 11 и 12. Тактовые входы логических ключей 9 и 10 подключены соответственно к прямому и инверсному выходам элемента сравнения 8,управляющи входы соединены с выходами 1-ro и (q+1)-го триггеров делителя частоты соответственно. Выходы логических ключей 9 и 10 подключены соответственно к фазорасщепителям 11 и 12, каждый из которых содержит два формирователя коротких импульсов 13 и 14, элемент ИЛИ 15, последовательный регистр сдвига 16 составленный из (m-1) триггеров 17"21, и счетчик импульсов 22, выход которого подключен к тактовому входу регистра сдвига

16, тактовый вход соединен с выходом управляемого генератора 5, а вход установки соединен с выходом элемента ИЛИ 15, один вход которого соединен со входом установки " " триггера

1095341 1

17 и подключен к выходу формирователя 14 коротких импульсов, а другой вход объединен со входом установки

"$" триггера 17 и подключен к выходу формирователя 13 коротких импульсов, вход которого объединен с информационным входом регистра сдвига 16 и подключен к прямому выходу логического ключа, инверсный выход которого соединен с входом формирователя 14 коротких импульсов. Блок контроля 23 содержит2 -триггеры 24 и 25, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 26 и 27 и элемент

И 28,каждый вход которого соединен с выходом соответствующего элемента .

ИСКЛЮЧАЮЩЕЕ ИЛИ, один вход элемента

26 подключен к выходу логического ключа 9, другой вход соединен с выходом -триггера 24, тактовый вход которого соединен с выходом счетчика импульсов 22 фазорасщепителя 11, информационный вход подключен к прямому выходу триггера 21 регистра сдви5 !

О

20 га 16 в фазорасщепителе 11. Аналогичвход — к выходу1) -триггера 25, тактовый вход которого соединен с выходом счетчика импульсов 22 в фазорасщепителе 12, информационный вход соединен с прямым выходом триггера 21 регистра сдвига 16 в фазорасщепителе

12.

На фиг. 2 приняты следующие обоз- 35 начения: 29 — импульсы на выходе формирователя 1 синхронизирующих импульсов; 30 — импульсы с выхода фазового детектора 3; 31 — напряжение на выходе преобразователя 4 длитель- 40 ности импульсов в напряжение; 32— импульсы на выходе управляемого генератора 5; 33 — импульсы на прямом выходе 1-го триггера; а 34— импульсы на прямом выходе (11+1)-го 45 триггера делителя частоты 6; 35—

1напряжение на выходе генератора 7 треугольного напря.хения, g> — управляющее напряжение; 36 — импульсы на прямом выходе элемента сравнения 8; 50

37 — импульсы на прямом выходе логического ключа 9; 38 — импульсы на выходе. формирователя 13 коротких импульсов; 39 — импульсы на выходе фор.

ИЛИ 15; 41 — импульсы на выходе счетчика импульсов 22; 42 — импульсы на но одни входы элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 27 подключены соответственно к выходу логического ключа 10, другой мирователя 14 коротких импульсов;

40 — импульсы на выходе элемента прямом выходе первого 9 -триггера

17 последовательного регистра сдвига

16; 43 — импульсы на прямом выходе (в-1)-го2 -триггера 21 последовательного регистра сдвига 16; 44 — импульсы на прямом выходе2 -триггера 24;

45 — напряжение на выходе элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ 26; 46 — импульсы на инверсном выходе элемента сравнения

8; 47 — импульсы на прямом выходе логического ключа 10; 48-50 — сигналы на выходах элементов фазорасщепителя

12, в том числе:,48 — импульсы на прямом выходе первого2 -триггера 17 последовательного регистра сдвига 16, 49 — импульсы на прямом выходе 9-1)ro триггера 21 последовательного регистра сдвига 16; 50 — импульсы на прямом выходец-триггера 25; 51 напряжение на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 27; 52 — напряжение на выходе элемента И 28.

Устройство работает следующим образом.

На выходе формирователя 1 с;;нхронизирующих импульсов формируются— прямоугольные импульсы 29 со скважностью "два", которые поступают на блок 2 фазовой автоподстройки частоты. а точнее — на один из выходов фазового детектора 3, на другой вход которого поступают прямоугольные импульсы 33 со скважностью "два" с прямого выхода первого триггера делителя частоты 6. На выходе фазового детектора 3 формируются импульсы 30, длительность которых прямо пропорциональна рассогласованию по фазе между сигналами 29 и 33. При этом, если выходной сигнал 29 формирователя 1 синхронизирующих импульсов опережает по фазе сигнал 33, поступающий с выхода делителя частоты 6, полярность выходных импульсов 30 фазового детектора 3 положительная (фиг.2), если же отстает, то отрицательная.

На выходе преобразователя 4 длительности импульсов в напряжение, подключенного к выходу фазового детектора

3, формируется, постоянное напряжение

3i, уровень которого прямо пропорционален длительности импульсов 30, т.е. рассогласованию по фазе между сигналами 29 и 33. Постоянное напряжение 31 поступает на вход управляемого генератора 5, который в установивишемся режиме генерирует импульсы

1095341

32 с частотой, превьш ающей частоту синхронизирующих импульсов 29 в целое число раз. К выходу управляемого генератора 5 подключен делитель частоты 6 на 2 и триггерах, где и- =1,2,3...,5 охваченных перекрестными обратными связями. На прямом выхопе первого триггера делителя частоты 6 формируются импульсы 33, на прямом выходе (0+1)-roD -триггера формируются им10 пульсы 34, сдвинутые относительно импульсов 33 на 90 эл.град. Пусть по каким-либо причинам частота синхронизирующих импульсов 29 увеличилась.

Тогда возрастает длительность импуль15 сов 30 на выходе фазового детектора

3 и увеличится постоянное напряжение

31 на входе управляемого генератора

5. Это вызовет увеличение частоты управляемого генератора и фаза импульсов 33 и 34 на выходах делителя частоты 6 изменится так, что частоты сигналов 29, 33 и 34 будут вновь равны друг другу. Таким образом, с

25 помощью блока 2 фазовой автоподстройки частоты осуществляется синхронизация устройства управления, а значит и преобразователя в целом от другого источника и формируется три последовательности импульсов: высокочастотные импульсы 32, частота которых строго в целое число раз превышает частоту синхронизирующих импульсов

29, и две последовательности импульсов 33 и 34, синхронных с последова- 35 тельностью синхронизирующих импульсов 29 и сдвинутых относительно друг друга на 90 эл.град. Эти две последовательности импульсов поступают на формирователь 7 развертывающего на- 40 пряжения, на выходе которого формируется треугольное напряжение двойной частоты 35. На выходе элемента сравнения 8, подключенном к формирователю развертывающего напряжения, 45 в момент равенства треугольного напряжения 35 с управляющим UI1 формируются прямой и инверсный сигналы

36 и 46, которые поступают на тактовые входы логических ключей 9 и 10 соответственно. На управляющие входы логического ключа 9 поступают прямой и инверсный сигналы с выхода первого триггера делителя частоты 6. Переключение логического ключа 9 проис- 55 ходит при подаче на его тактовый !! t! вход сигнала ло гиче с кои 1, т . е, передний фронт импульсов 36 опреде. ляет фазу прямоугольных импульсов

37, формируемых логическим ключом

9. На управляющие входы логического ключа 10 поступают прямой и инверсный сигналы с выхода (n+1)D -тригге-! ра делителя частоты 6. Переключение логического ключа 10 происходит также при подаче на его тактовый вход сигнала логической "1", так как передний фронт импульсов 46 определяет фазу прямоугольных импульсов 47, формируемых логическим ключом 10. Таким образом, на выходах логических ключей

9 и 10 формируются две однородные последовательности прямоугольных импульсов 37 и 47, регулируемых по фазе. При изменении управляющего напряжения ll!! от 0 до амплитуды треугольного напряжения фаза выходных импульсов 37 логического ключа 9 изменяется на 90 эл.град. в сторону отставания, а фаза выходных импульсов 47 логического ключа 10 — на 90 эл.град. в сторону опереженйя относительно сигнала

29, снимаемого с выхода формирователя

1 синхронизирующих импульсов, К выходам логических ключей 9 и

10 подключены соответственно фазорасщепители 11 и 12, формирующие (! !-1)фазные последовательности управляющих импульсов. Оба фазорасщепителя построены по одной и той же схеме, поэтому принципы формирования (л -1)фазной последовательности управляюц!их импульсов рассмотрим на примере фазорасщепителя 11, подключенного к выходам логического ключа 9. Пусть в результате предыдущих переходных процессов все триггеры регистра сдвига 16 находятся в нулевом состоянии, а сигнал 37 на прямом выходе логического ключа 9 принимает состояние "1".

B этот момент на выходе формирователя

13 коротких импульсов возникает короткий импульс 38, который поступает на установочный вход "5" триггера 17 последовательного регистра сдвига 16 и на вход элемента ИЛИ 15. С выхода элемента ИЛИ 15 импульс 40 поступает на вход установки "Д" счетчика импульсов 22 и переводит его в состояние

"0". Поскольку время срабатывания счетчика имеет конечную длительность, то возможна ситуация, когда "1" с выхода счетчика 22 сразу после перек-. лючения логического ключа 9 поступает на тактовый вход "С" триггера 17 и происходит его ложное срабатывание.

1095341

Посылкой короткого импульса 38 на установочный вход "5" триггера 17 ложные срабатывания исключаются.

На счетный вход счетчика 22 непрерыв но поступают. высокочастотные импульсы 32 с выхода у. равляемого генератора 5. При заполнении счетчика на тактовые входы "C" всел триггеров регистра сдвига 16 поступают импуль0 сы 41. Но переключается при этом только триггер 17 (сигнал 42 на фиг.2), так как только на его информационном входе "D" сигнал изменился с "0" на

"1". Затем счетчик возвращается в

15 нулевое состояние, вновь заполняется, 1при этом переключается следующий триггер 18 регистра сдвига, далее процессы про-.екают аналогично. За полпериода частоты синхронизирующего напряжения 29 счетчик 22 успевает

20 заполниться 1п раз. При этом переключаются все триггеры регистра сдвига, так что сдвиг по фазе между выходными импульсами двух соседних триггеров регистра сдвига, а также между импульсами с выходов логического ключа

9 и триггера 17 составляет 180/щ эл. град. Чем выше частота управляемого генератора, тем больше емкость счетчика и тем точнее выдерживается требуе- З0 мый фазовый сдвиг, т.е. тем выше симметрия управляющих импульсов. При переключении логического ключа 9 в нулевое состояние формируется короткий импульс 39 на выходе формирователя 35

14 коротких импульсов, который, поступая на установочный вход Я" триггера 17 младшего разряда регистра сдвига, удерживает его в единичном состоянии до тех пор, пока импульс 40

40 с выхода элемента ИЛИ 15 не подготовит счетчик импульсов 22 к приему импульсов от управляемого генератора

5. При заполнении счетчика на его выходе формируется сигнал 1 и тригll 11 45 гер 17 переводится в нулевое состояние. Послед-го заполнения счетчика переключится тригг< р старшего разряда 21, формируяа-ю последовательность однофазных импульсов 43 (для

50 определенности взято 1п =6 и сдвиг по фазе между двумя соседними однофазными последовательностями импульсов составляет 30 эл.град.). На вы ходе D -триггера 24 в блоке контроля

23 формируется (1 1+ 1)-я последовательность импульсов 44, сдвинутая на

180 эл,град. относительно первой последовательности импульсов 37 с выхода логического ключа 9. Таким образом, при нормальной работе устройства сигналы 37 и 44, поступающие на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26, находятся в противофазе и на его выходе практически постоянно присутствует уровень логической "I". Только в момент изменения сигнала 37 на выходе логического ключа 9, сигнал

45 на выходе элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 26 кратковременно может принять значение логического "0" вследствие конечного времени переключения элементов схемы и ошибки за счет дискретизации.

Аналогично с помощью логического ключа 10 и фазорасщепителя 12 формируется втораяа -фазная последовательность управляющих импульсов, а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 27 формируется сигнал 51.

Сигналы 45 и 51 с выходов элементов ИСКЛ10ЧАЮЩЕЕ ИЛИ 26 и 27 поступают на входе элемента И 28, к выходу которого подключен конденсатор С, который устраняет кратковременные изменения сигнала на выходе элемента

И 28, вызванные конечным временем переключения элементов схемы и ошибкой за счет дискретизации. Таким образом, при нормальной работе устройства сигнал 52 на выходе элемента

И 28 будет иметь значение логической "1".

В случае поступления импульсной помехи на тактовый вход регистра сдвига 16 в фазорасщепителе 11 (сигнал .

41), например, в момент времени 11 триггер 21 переключится импульсом помехи, а следующий тактовый импульс переключит D -триггер 24 в блоке контроля. В результате сигнал 37 на выходе логического ключа 9 и сигнал 44 на выходец -триггера 24 становится одинаковым, а на выходе элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ 26 появится уровень логического "0" (сигнал 45), что,в свою очередь, вызывает появление логического "0" на выходе элемента И 28 (сигнал 52).

В случае неисправности элементов фазорасщепителя (например, счетчика

22 или одного из триггеров регистра сдвига 16 в фазорасщепителя 12 в момент времени 4g) после переключения логического ключа 10 сигнал 47 на егс выходе изменится, а сигнал 50 на вы1095341

10 ходеЗ-триггера 25 в блоке контроля останется прежним. В результате на выходе элемента ИСКЛЮЧАВМЦЕЕ ИЛИ 27 появится уровень логического "0" (сигнал 51), что приводит к появлению логического "0" на выходе элемента И 28 (сигнал 52).

Неисправность логического ключа (например, логического ключа 9) при" водит к тому, что после возникновения 10 неисправности (момент времени, ) он не переключается и на его.âûõîäå но» стоянко поддерживается уровень логического "0" (сигнал 37). В то же время триггеры регистра сдвига в фазорасщепителе 11 продолжают переключаться до тех пор, пока все они не установятся в нулевое состояние. Следу " щий тактовый импульс вызовет переключением) -триггера 24 в блоке контроля го и на его выходе появится сигнал 44 логического "0". В результате . на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26 появится уровень логического "0" (сигнал 45), что приводит к появлению логического "0", на выходе элемента

И 28 (сигнал 52) .

Таким образом, сбой или неисправность устройства приводит к появлению уровня логического "0" на выходе элемента И 28 в блоке контроля.

Введение в устройство для управлениял1-фазным преобразователем блока контроля позволяет осуществлять постоянный контроль за правильностью работы устройства и своевременно об1 наруживать практически любую неиспр«вность или сбой. Благодаря этому существенно. повышается надежность устройства управления.

1095341

so

37

DZ

Составитель Н. Савинова

Редактор Т. Веселова Техред Т.Маточка Корректор П. Коссей

3617/39

Заказ

З5

Ж

37

38

39

И

lQ

И ф/

if/

//g

Ф7

Тираж 667 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4