Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ , содержащий фазопращающий блок, выход которого соединен с первым входом блока фазовых компараторов, подключенный вторым входом к первому выходу блока управления, вход которого соединен с первым выходом блока фазовых компараторов, соединенного вторым выходом с первым входом шифратора , второй вход которого подключен к второму выходу блока управления , а выход - к первому входу регистра , второй вход которого соединен с третьим выходом блока управления , а выход - с выходной шиной преобразователя и через блок компенсирующего тока - с первым входом фазовращающего блока, второй вход которого соединен с входной шиной преобразователя , а третий вход - с выходом генератора, отличающийся тем, что, с целью повышения точности, в него введены фазовращатель Смещения, опорный фазовращатель и опорный фазовый компаратор , причем выход генератора соединен через фазовращатель смещения с третьим входом блока фазовых компараторов , выход фазовращающего блока соединен с первым входом опорного (Л фазового компаратора, второй вход которого соединен через опорный фазовращатель с выходом генератора, а выход соединен с третьими входами шифратора и регистра, четвертый вход которого соединен с дополнительным выходом блока управления. Г) ел :с со со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) З(51) Н 03 К 13 20

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

БНБЛЫОИ1(А (21) 3565141/18-21 (22) 21.01.83 (46) 30.05 ° 84. Бюл. № 20 (72) В.П.Стокай (71) Ордена Ленина институт кибернетики им. В.M.Глушкова, (53) 621.376(088.8) (56) 1. Приборы и системы управления", 1972, № 8, с. 40-43.

2. Авторское свидетельство СССР № 477541, кл. Н 03 К 13/20,05.06.1973. (54)(57) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий фазовращающий блок, выход которого соединен с первым входом блока фазовых компараторов, подключенный вторым входом к первому выходу блока управления, вход которого соединен с первым выходом блока фазовых компараторов, соединенного вторым выходом с первым входом шифратора, второй вход которого подклю. чен к второму выходу блока управления, а выход — к первому входу регистра, второй вход которого соединен с третьим выходом блока управления, а выход — с выходной шиной преобразователя и через блок компенсирующего тока — с первым входом фазовращающего блока, второй вход которого соединен с входной шиной преобразователя, а третий вход — с выходом генератора, о т л и ч а ю— шийся тем, что, с целью повышения точности, в него введены фазовращатель смещения, опорный фазовращатель и опорный фазовый компаратор, причем выход генератора соединен через фазовращатель смещения с третьим входом блока фазовых компараторов, выход фазовращающего блока соединен с первым входом опорного фазового компаратора, второй вход которого соединен через опорный фазовращатель с выходом генератора, а выход соединен с третьими входами шифратора и регистра, четвертый вход которого соединен с дополнительным выходом блока управления.

1 1 0953

Изобретение относится к импульсной технике и может быть использовано при измерении слабых токов.

Известно устройство, содержащее фазовращающий блок, грубую и точную цепи преобразования, каждая из которых состоит из последовательно соединенных блока фазовых компараторов, дешифратора, регистра, блока компенсирующего тока, генератора опорного 10 напряжения 1

Недостатком этого устройства является низкая точность.

Наиболее близким к предлагаемому по техническому решению является уст- 15 ройство, содержащее фазовращающий блок, выход которого соединен с первым входом блока фазовых компараторов, второй вход которого подключен к первому выходу блока управления, первый вход которого соединен с пер" вым выходом блока фазовых компара- тороз, второй выход которого соединен с первым входом шифратора, второй вход которого соединен с вторым выходом блока управления, а выход — с первым входом регистра, второй и третий входы которого соединены с третьим и четвертым выходами блока управления, а выход соединен с шиной выходного сигнала и через блок компенсирующего тока соединен с первым входом фазовращающего блока, второй вход которого соединен с шиной входного сигнала, а третий вход соединен с выходом генератора и с третьим вхо«Ý5 дом блока фазовых компараторов (23.

Недостатком известного устройства является низкая точность.

Цель изобретения — повышение точ»

40 ности, Поставленная "цель достигается тем, что в устройство, содержащее фазовращающий блок, выход которого соединен с первым входом блока фазовых компараторов, подключенный вторым входом к первому выходу блока управления, вход которого соединен с первым выходом блока фазовых компараторов, соединенного вторым выходом с первым

50 входом шифратора, второй вход которого подключен к второму выходу блока управления, а выход — к первому входу регистра, второй вход которого соединен с третьим выходом блока управления, а выход — с выходной шиной преобразователя и через блок компенсирующего тока — с первым входом фаэовращающего блока, второй вход

93 2 которого соединен с входной шиной преобразователя, а третий вход — с выходом генератора, введены фазовращатель смещения, опорный фазовращатель и опорный фазовый.компаратор, причем выход генератора соединен через фазовращатель смещения с третьим входом блока фазовых компараторов, выход фазовращающего блока соединен с первым входом опорного фазового компаратора, второй вход которого соединен через опорный фазовращатель с выходом генератора, а выход соединен с третьими входами. шифратора и регистра, четвертый вход которого соединен с дополнительным выходом блока управления.

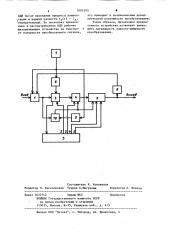

На чертеже представлена блок-схема аналого-цифрового преобразователя.

Аналого-цифровой преобразователь содержит фазовращающий блок 1, выход которого соединен с первым входом блока 2 фазовых компараторов, второй вход которого.подключсн к первому выходу блока 3 управления, первый вход которого соединен с первым выходом блока 2, второй выход которого соединен с первым входом шифратора 4, второй вход которого соединен с вторым выходом блока 3 управления, а выход соединен с первым входом регистра 5, второй и четвертый входы которого соединены с третьим и четвертым выходами блока 3 управления, а выход соединен с шиной выходного сигнала и через блок б компенсирующего тока— с первым входом блока 1, второй вход которого соединен с шиной входного сигнала, а третий вход соединен с выходом генератора 7, через фазовращатель 8 смещения с третьим входом блока 2 и через опорный фазовращатель 9 с первым входом опорного фазового компаратора 10, второй вход которого соединен с выходом блока 1, а выходс третьим входом шифратора 4 и третьим входом регистра 5.

Устройство работает следующим образом.

В течение первого такта кодирования в зависимости от величины фазового сдвига У,, пропорционального величине преобразуемого сигнала Ч „(), в блоке 2 срабатывает определенное количество фазовых компараторов и при помощи шифратора 4 формируется и/2 старших разрядов двоичного цифрового кода, который по сигналу иэ блока 3 управления заносится в и/2 старших

109

1О

25

30 мого сигнала IX(t) 35

3 разряда регистра 5. Пропорциональный этому коду компенсирующий ток Зк, вырабатываемый в блоке 6 компенсирующего тока, поступает на второй вход блока 1, осуществляя компенсацию сдвига фазы его выходного напряжения до значения 3 . В результа" те процесса компенсации выходное напряжение имеет некоторый остаточный фазовый сдвиг где — значение фазы выходного наМ пряжения блока 1, пропорциональное входной преобразуемой величине „(1); значение фазы, йропорциональное двоичному коду, занесенному в первом такте преобразования в регистр 3.

При компенсации под воздействием компенсирующего тока 3 фаза выходного напряжения фазовращающего блока

1 сдвигается в направлении, противоположном тому, в котором она сдвигалась под воздействием входного сигнала 3 „() .

В течение второго такта происходит кодирование величины Pо — определение и занесение в соответствующие разряды регистра 5 и/2 младших разрядов выходного кода. В течение процесса компенсации по сигналу из блока

3 управления происходит соответствующая перестройка блока 2 фазовых компараторов. Если корректирующий компаратор 10 не сработал, то в течение второго такта работа АЦП происходит так же, как и в течение первого так та: при помощи блока 2 фазовых компараторов и шифратора 4 происходит формирование и занесение в регистр 5 двоичного кода, соответствующего n/2 младшим разрядам.

На этом преобразование заканчивается и АЦП готов к новому циклу преобразования.

Если же опорный компаратор 10 сработал, то это означает, что разностный сигнал ц, соответствующий разностному току I р= I x(t) - Тк,где

3< - компенсирующий ток, пропорциональный коду п/2 старших разрядов регистра 5), превышает диапазон сигналов, на который настроены фазовые компараторы в блоке 2 в течение второго такта кодирования, т.е. частичный код n/2 старших разрядов, сформи5393 4 рованный в течение первого такта кодирования, получен с недостатком (меньше истинного). Поэтому этот код должен быть скорректирован.

Для того, чтобы в течение второго такта преобразования происходило исправление ошибки, возникшей в первом такте, введен компаратор 10, опорный уровень которого, обеспечиваемый опорным фазовращателем 9, продолжает прогрессию, образуемую опорными уровнями компараторов блока 2. Компаратор

10 определяет номинальный диапазон уровней, подаваемый на блок 2 фазовых компараторов в течение второго такта преобразования. Он обнаруживает любой переход за границу этого диапазона, а значит, и наличие ошибки в первом такте.

После этого происходит процесс докомпенсации фазы выходного напряжения рабочего фазовращающего блока

1 до значения Урра 2 1ост . Процесс докомпенсации заключается в том, что в блоке 6 компенсирующего тока вырабатывается несколько больший комI пенсирующий ток, соответствующий уже правильному коду четырех старших разрядов выходного кода, в результате чего фаза выходного напряжения рабочего фазовращающего блока 1 еще больше сдвигается в направлении, противоположном тому, в котором она сдвигалась под воздействием преобраэуеПосле окончания процесса докомпенсации происходит кодирование величины Чо т2,. т.е. определение четырех младших разрядов выходного кода.

Фазовращатель 8 обеспечивает смещение уровней настройки фазовых компараторов в блоке 2 только вверх (в сторону увеличения), благодаря чему код четырех старших разрядов всегда получается или правильным, или с недостатком.

При отсутствии смещения пороги срабатывания фазовых компараторов могут сместиться не только вверх, но и вниз. В последнем случае определяемый в течение первого такта преобразования код старших разрядов получают с избытком. Поэтому величина компенсирующего тока I> превышает величину входного (преобразуемого) тока

I>(t), в силу чего эквивалентный входной ток, воздействующий на вход

1095393

Составитель Н. Коновалов

Редактор Л. Веселовская Техред С.Иигунова Корректор A. Ференц

Заказ 3622/42 Тираж 862 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

АЦП после окончания процесса компен1сации и равный разности I>(t) — I.+, отрицательный. Но поскольку применяемое в рассматриваемом АЦП рабочее фазовращающее устройство не чувствует полярности преобразуемого сигнала, это приводит к возникновению дополнительной погрешности преобразования.

Таким образом, пременение предлагаемого устройства позволяет умень5 шить погрешность аналого-цифрового преобразования.