Устройство для решения дифференциальных уравнений в частных производных

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ, содержащее R-сетку, преобразователь код - напряжение, выхоД которого непосредстве нно подкхвочен к первому граничному узлу R-сетки, а через преобразователь напряжение ток соединен с вторым граничньм уз- ; лом R-сетки, блок памяти, выход которого подключен к входу задания кода преобразователя код-напряжение, вход задания эталонного напряжения которого соединен с выходом цифроаналогового преобразователя, информационный вход устройства подключен к входу блока памяти, отличающеёс я тем, что, с целью повышения быстродействия, в него введены блок сравнения, блок дифференцирования, пороговый блок, три элемента задержки , два элемента И, аналого-цифровой преобразователь, регистр, два ши атора , два формирователя прямоугольных импульсов и элемент ИЛИ, причем центральные узлы R-сетки подключены 8УЙ1,1096663 А a v«jwai) 3

СОЮЗ СОВЕТСКИХ

ОРИIIHDIINE

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ н asmpaewv саиайвльств

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

FO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТН ЫТЗФ (21) 3476634/18-24 (22) 28.07.82 (46) 07.06.84. Бюл. В 21 (72) И.Э. Опманис, Э.Э. Родэ и Я.Г. Лимежс (71) Рижский ордена Трудового Крас" ного Знамени политехнический институт (53) 681.333(088.8) (56) 1. Авторское свидетельство СССР

В 332469, кл. G 06 G 7/40, 1970.

2. Авторское свидетельство СССР

Ф 473453, кл. G 06 С 7/40, 1973 (нрототил). (54)(57) УСТРОЙСТВО ДЛЯ РЕШКНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ

ПРОИЗВОДНЫХ, содержащее к-сетку, преобразователь код — напряжение, выход" которого непосредственно подключен к первому граничному узлу R-сетки, а через преобразователь напряжение - ток соединен с вторым граничным узлом к-сетки, блок памяти, выход которого подключен к входу задания кода преобразователя код-напряжение, вход задания эталонного напряжения которого соединен с выходом цифроаналогового преобразователя, информационный вход устройства подключен к входу блока памяти, о т л и ч а ю щ Q pс я тем, что, с целью повынения быстродействия, в него введены блок, сравнения, блок дифференцирования, Ъ. пороговый блок, три элемента задержки, два элемента И, аналого-цифровой преобразователь, регистр, два шифратора, два формирователя прямоугольных импульсов и элемент ИЛИ, причем центральные узлы R-сетки подключены

gory С 06 С 7/40 ., 1-. ° к -группе входов блока сравнения, выход которого соединен с входом аналого-цифрового преобразователя и с входом блока дифференцирования, выход которого подключен к входу порогового блока, выход которого непосредственно соединен с первым входом первого элемента И, а через первый элемент задержки — с вторым входом . первого элемента И, выход которого подключен к первому входу первого шифратора, первый выход которого является выходом готовности устройства, вход запуска которого соединен с входом первого формирователя прямоугольных импульсов и с входом второго эле- И

9 мента задержки, выход которого подключен к первому входу второго элемента И и к входу третьего элемента задержки, выход которого соединен со стробирующим входом второго шифратора, выход которого подключен к входу цифроаналогового преобразователя и к второму входу первого шифратора, второй выход которого является информационным выходом устройства, выход аналого-цифрового преобразователя соединен с вторым входвм второго элемента И, выход которого подключен к входу- записи кода регистра и к треТьему входу первого шифратора, третий выход которого соединен с входом второго формирователя прямоугольных еимпульсов, выход которого подключен к первому входу элемента ИЛИ, выход которого соединен с входом обнуления регистра, выход первого формироватепя прямоугольных импульсов подключен к второму входу элемента ИЛИ.

1096663

1О

Однако в известном устройстве при задании токов в узловые точки сеточной модели неизвестен момент окончания переходного процесса и неизвестен . необходимый масштаб вводимых токов.

Начало работы устройства масштабиро50 вания определяют программным путем, а масштабный коэффициент выбирают методом последовательного приближения.

Это увеличивает время решения задачи на сеточной модели, что снижает быст55 родействие устройства.

Целью изобретения является повыпение быстродействия устройства.

Изобретение относится к аналогоцифровой вычислительной технике и предназначено для решения дифференциальных уравнений в частных производных. . Известно устройство для решения дифференциальных уравнений в частных производных, содержащее блок памяти, подключенный к преобразователю, соединенному с блоком запоминающих источников, выходы которых подключены к узловым точкам R-сетки, блок памяти связан с блоком управления (1) .

Однако устройство не позволяет

J получить оптимальное распределение потенциалов на сеточной модели, что может привести к потере информации из-за перенапряжений или из-за низких потенциалов, которые ниже уровня помех.

Наиболее близким к изобретению по технической сущности является устройство для решения дифференциальных уравнений в частных,проиэвод- 25 ных, содержащее R-сетку, преобразователь код — напряжение, выход которого непосредственно подключен к первому граничному узлу R-сетки, а через преобразователь напряжение — 5б

) ток соединен с вторым граничным узлом R-сетки, блок памяти, выход которого подключен к входу задания кода преобразователя код - напряжение, вход задания эталонного напряжения которого соединен с выходом цифроаналогового преобразователя, информационный вход устройства подключен к входу блока памяти. Кроме того, устройство содержит счетчик, 4 дешифратор, управляемый источник напряжения, блок стабилизаторов тока, и блок управления, который управляет работой всех блоков устройства 2 1

Поставленная цель достигается тем, что в устройство, содержащее R-сетку, преобразователь код — напряжение, выход которого непосредственно подключен к первому граничному узлу R-сетки, а через прдобразователь напряжение— ток соединен с вторым граничным узлом К-сетки, блок памяти, выход которого подключен к входу задания кода преобразователя код — напряжение, вход задания эталонного напряжения которого соединен с выходом цифроаналогового .преобразователя, информационный вход устройства подключен к входу блока памяти, введены блок сравнения, блок дифференцирования, пороговый блок, три элемента задержки, два элемента И, аналого-цифровой преобразователь, регистр, два шифратора, два формирователя прямоугольных импульсов и элемент ИЛИ, причем центральные узлы R-сетки подключены к ,группе входов блока сравнения, выход которого соединен с входом аналогоцифрового преобразователя и с входом блока дифференцирования, выход которого подключен к входу порогового блока, выход которого неносредственно соединен с первым входом первого элемента И, а через первый элемент задержки — с вторым входом первого элемента И, выход которого подключен к первому входу первого шифратора, первый выход которого является выходом готовности устройства, вход запуска которого соединен с входом первого формирователя прямоугольных импульсов и с входом второго элемента задержки, выход которого подключен к первому входу второго элемента И и к входу третьего элемента задержки, выход кЬторого соединен со стробирующим входом второго шифратора, выход которого подключен к входу цифроаналогового преобразователя и к второму входу первого шифратора, второй выход которого является информационным выходом устройства, выход аналогоцифрового преобразователя соединен с вторым входом второго элемента И, выход которого подключен к входу записи кода регистра и к третьему входу первого шифратора, третий выход которого соединен с входом второго формирователя прямоугольных импульсов, выход которого подключен к первому входу элемента ИЛИ, выход которого соединен с входом обнуления регистра, вьФод первого формирователя прямо1096663 угольных импульсов подключен к второму входу элемента ИЛИ.

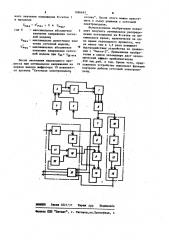

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит R-сетку 1, преобразователь 2 напряжение — ток, преобразователь 3 код — напряжение, блок 4 памяти, цифроаналоговый преобразователь 5, блок 6 сравнения, аналого-цифровой преобразователь 7, !

О элемент И 8, регистр 9, блок 10 дифференцирования, пороговый блок 11, элемент И 12, элемент 13 задержки, шифратор 14, элемент 15 задержки, элемент 16 задержки, формирователь 17

15 прямоугольных импульсов, элемент ИЛИ

18, шифратор t9, формирователь 20 прямоугольных импульсов.

Устройство работает следующим образом.

В блок 4 памяти заносится массив исходных данных для блока 3. Сеточная электромодель R-сетка 1 настраивается согласно решаемой задаче. 25

Для запуска устройства на вход элемента 15 задержки и формирователя 17 подается уровень напряжения, который поддерживается до съема решения с

R-сетки 1. Уровень напряжения через 30 первый формирователь 17 и элемент

ИЛИ 18 устанавливает регистр 9 в нулевое состояние, через первый 15 и второй 16 элементы задержки на блок элементов И 8 и шифратор 14 поступа35 ют разрешающие уровни, после чего шифратор 14 выдает код управления цифроаналоговому преобразователю 5, которому соответствует минимальное выходное напряжение цифроаналогового преобразователя 5, которое является опорным напряжением По„ преобразователя 3 код — напряжение. На выходах преобразователя 3 код — напряжение и преобразователя 2 напряжение — ток устанавливаются минимальные напряжения и токи, пропорциональные кодам исходных данных, записанных в блоке 4 памяти,и опорному напряжению. На

R-сетке 1 формируется распределение потенциалов, блок 6 сравнения непрерывно выдает максимальный по абсолютному значению потенциал узловых точек R-сетки 1. Аналого-цифровой преобразователь 7 непрерывно преобразовывает выходное напряжение блока 6 сравнения в код, который через элемент И 8 поступает на кодовый вход регистра 9. Выходное напряжение блока 6 сравнения поступает также на вход элемента 13, который выдает высокий уровень на время нарастания напряжения на выходе. По окончании переходного процесса прекращается нарастание или спадение напряжение на входе элемента 13, вторый выдает уровень на выходе, близкий к нулю.

После этого пороговый блок 11, сравнивая выходное напряжение элемента 13 с опорным напряжением, вырабатывает уровень окончания переходного процесса. Для исключения появления ложного уровня окончания переходного процесса от неравномерного изменения выходного напряжения блока 6 сравнения устройство содержит элемент 13 задержки и элемент И 12, задерживающие уровень окончания переходного процесса.

Уровень окончания переходного процесса от элемента И 12 поступает на третий вход шифратора 19. Если выходное напряжение блока 6 после окончания переходного процесса находится в пределах

0,5 U ä„ñ U и мак где 0„,а„ вЂ” максимально возможное напряжение сеточной электромодели, то при поступлении уровня окончания переходного процесса шифратор 19 на первый выход выдает уровень "Сеточная электромодель готова".

Если выходное напряжение блока 6 после окончания переходного процесса больше максимально допустимого, шиф- ратор 19 на второй выход выдает уровень "Перенапряжение сеточной электромодели", после чего необходимо снять уровень "Пуск сеточной электромодели", произвести повторный расчет и перезанесение исходных данных и повторить процесс сначала.

Если выходное напряжение блока 6 после окончания переходного процесса меньше половины максимально допустимого и на выходе цифроаналогового преобразователя установлено минимальное опорное напряжение, то на третий выход шифратора поступает уровень, который формирователем 20 формируется в импульс, разрешающий через элемент

ИЛИ 18 запись выходного кода элемента. И 8 в регистр 9. Выходной код регистра 9 поступает на вход шифратора

14, который управляет цифроаналоговым преобразователем 5 таким образом, чтобы добиться максимального абсолют5 1096663 6

It ного значения напряжения R-сетки 1 готова . После этого можно пристув пределах пить к съему решения с сеточной

1 электромодели. а П и 0

"еа к " o II ЧЕк Использование изобретения позвогде U — максимальное абсолютное з ляет получить оптимальное распредезначение напряжения сеточ- ление потенциалов на К-сетке за ми« ной модели нимальное время, практически sa ода ьно допустимое зни- но времЯ пеРехоДного пРоЦесса, что

Мах чение сеточной модели; не менее чем в 1,$ Раза повышает

U — максимальное абсолютное быстродействие устройства по сравне-, Old g

It II значение напряжения сеточ- ниш с Омега-2 . Применение изобреной модели при 0 0 „,„,„ тения а одном экземпляре даст экономический эффект приблизительно

После окончания переходного про- 250 тыс.Руб. в год. Кроме того,.предце а при оптимальном напряжении на r5 ложенное Устройство выполняет функции первом выходе шифратора 39 появляет- контроля Работы сеточной электромося уровень "Сеточная электромодель дели, с

ЗИННИ . 33_#_33 3827/37 Тираа ®9, Подписное ф@йиай ШШ "и® eit г. ужгород,ул.Проектная, 4