Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

1. ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее матрицу запоминаю-, щих элементов, дешифраторы строк и столбцов, коммутатор столбцов, причем объединенные по столбцам выходы запоминающих элементов соединены с входыми первой группы входов коммутатора столбцов, входы второй группы входов которого соединены с выходами дешифратора столбцов, а выход является выходом устройства, объединенные по строкам первые входы запоминающих элементов соединены с выходами дешифратора строк, входы дешифраторов строк и столбцов являются входами первой и второй групп адресных входов устройства соответственно, о тличающееся тем, что, с целью упрощения устройства, оно содержит блок формирования логических функций двух переме1шых , два входы которого являются входами третьей группы адреснъи входов устройства, а выходы соединены с вторыми входами за11оминающ11х элементов в соответствии с размещаемой в них информацией. 2. Устройство по п. 1, о -т л и ч а ющ е -е с я тем, что блок форм11рова1шя логических функций двух переменных содержит два элемента НЕ, входы которых являются входами блока, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и ЭКВИВАЛЕНТНОСТЬ, входы которых соединены с входами и выходами элементов НЕ, по четыре двухвходовых элемента И и ИЛИ, причем первые входы первого и второго элементов .И и ИЛИ соединенъ с входом первого элемента НЕ, а первые входы третьего и четвертого элементов И и ИЛИ - с выходом первого элемента НЕ, вторые входы первого и третьего элементов И и ИЛИ соединены с входом второго элемента НЕ, а вторые входы второго и четвертого элементов И и ИЛИ - с выходом второго элемента НЕ, выходы элементов И и ИЛИ являются с первого по восьмой выходами блока соответственно, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и ЭКВИВАЛЕНТНОСТЬ являются девятым и десятым выходами блоСО СГ) ка соответственно, выходы первого и второго элементов НЕ являются одиннадцатым и , х двенадцатым выходами блока соответственно, входы первого и второго элементов НЕ явля- I со 4: ются трннадцать1М и четырнадцатым выходами блока соответственно, Ш1шы нулевого по тенциала и питания являются пятнадцатым и шестнадцатъ1м выходами блока соответственно.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУВЛИК

ОЮ (11) ада G ll С Л)аО

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТБУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3471222/18-24 (22) 16.07.82 (46) 07.06.84. Бюл. У 21 (72) А. И. Комарова (53) 681.327.66 (088.8) (56) 1. Авторское свидетельство СССР

Р 881862, кл. G 11 С 17(00, 1979.

2. Соботка 3., Стары Я. Микропроцессоры системы. М., "Мир", 1981, с. 99, рис. 5.27, 5.28 (прототип) . (54) (57) 1. ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО, содержащее матрицу запоминаю-. щих элементов, дешифраторы строк и столбцов, коммутатор столбцов, причем объединенные по столбцам выходы запоминающих элементов соединены с входыми первой группы входов коммутатора столбцов, входы второй группы входов которого соединены с выходами дешифратора столбцов, а выход является выходом устройства, объединенные по строкам первые входы заломинающих элементов соединены с выходами дешифратора строк, входы дешифраторов строк и столбцов являются входами первой и второй групп адресных входов устройства соответственно, о тличающееся тем,что,сцелью упрощения устройства, оно содержит блок формирования логических функций двух переменных, два входы которого являются входами третьей группы адресных входов устройства, а выходы соединены с вторыми входами запоминающих элементов в соответствии с размещаемой в них информацией.

2, Устройство по и. 1, о т л и ч а ющ е е с я тем, что блок формирования логических функций двух переменных содержит два элемента НЕ, входы которых являются входами блока, элементы ИСКЛЮЧА—

ЮЩЕЕ ИЛИ и ЭКВИВАЛЕНТНОСТЬ, входы ко. торых соединены с входами и выходами элементов НЕ, по четыре двухвходовых элемента И и ИЛИ, причем первые входы первого и второго элементов .И и ИЛИ соединены с входом первого элемента НЕ, а первые входы третьего и четвертого элементов И и

ИЛИ вЂ” с выходом первого элемента НЕ, вторые входы первого и третьего элементов

И и ИЛИ соединены с входом второго элемента НЕ, а вторые входы второго и четвертого элементов И и ИЛИ вЂ” с выходом второго элемента НЕ, выходы элементов И и

ИЛИ являются с первого по восьмой выходами блока соответственно, выходы элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ н ЭКВИВАЛЕНТНОСТЬ являются девятым и десятым выходами блока соответственно, выходы первого и второго элементов НЕ являются одиннадцатым и двенадцатым выходами блока соответственно, входы первого и второго элементов НЕ явля- ются триналдатйм и четырналдатым выходами блока соответственно, шины нулевого потенциала и питания являются пятнадцатым и шест.

I надцатым выходами блока соответственно.

1096694

Изобретение относится к вычислительной технике и может быть использовано для построения постоянных запоминающих устройства (ПЗУ) .

Известно ПЗУ, в которое с целью уменьшения количества запоминающих элементов включаются генератор констант и формирователь двоичных последовательных кодов (1), Недостатком ПЗУ является последовательное считывание групп разрядов, что снижает быстродействие и усложняет управление выборкой информации.

Наиболее близким по технической сущноо ти к предлагаемому является ПЗУ, содержащее матрицу запоминающих элементов, дешифраторы строк и столбцов, причем объе диненные по столбцам выходы запоминающих элементов соединены с входами первой группы коммутатора столбцов,,входы второй группы входов которого соединены с выходами дешифратора столбцов, а выход является выходом устройства, объединенные но строкам первые входы запоминающих элементов соединены с выходами дешифратора строк, входы дещифраторов строк и столбцов являются входами первой и второй групп адресных входов устройства соответственно (2) .

Недостатком ПЗУ является сложность, обусловленная большим количеством запоминающих элементов в запоминающей матрице, Бель изобретения — упрощение устройства эа счет сокращения количества запоминающих элементов.

Поставленная цель достигается тем, что постоянное запоминающее устройство, содержащее матрицу запоминающих элементов, дешифраторы строк и столбцов, коммутатор столбцов, причем объединенные по столбцам выходы запоминающих элементов соединены с входами первой группы входов коммутатора столбцов, входы второй группы входов которого соединены с выходами дешифратора столбцов, а выход является выходом устройства, o&åäèíåíëûå по строкам первые входы запоминающих элементов соединены с выходами дешифратора строк, входы дешифраторов строк и столбцов являются входами первой и второй групп адресных входов устройства соответственно, содержит блок формирования логических функций двух переменных, два входа которого являются входами третьей группы адресных входов устройства, а выходы соединены с вторыми входами запоминающих элементов в .4 . соответствии с размещаемой в них информа1 цией;

1 Блок формирования логических функций двух переменных содержит два элемента. НЕ, входы которых являются входами блока, эле. менты ИСКЛЮЧАЮЩЕЕ ИЛИ и ЭКВИВАЛЕНТНОСТЬ, входы которых соединены с входами и выходами элементов НЕ, по четыре

5 двухвходовых элемента И и ИЛИ, причем первые входы первого и второго элементов

И и ИЛИ соединены с входом первого элемента НЕ, а первые входы третьего и четвертого элементов И и ИЛИ вЂ” с выходом первого элемента НЕ, вторые входы первого и третьего элементов И и ИЛИ соединены с входом второго элемента НЕ, а вторые входы второго и четвертого элементов И и

ИЛИ вЂ” с выходом второго элемента НЕ, выходы элементов И и ИЛИ являются с первого по восьмой выходами блока соответственно, выходы элементов ИСКЛЮЧАЮ—

ЩЕЕ ИЛИ и ЭКВИВАЛЕНТНОСТЬ являются девятым и десятым выходами блока соответ20 ственно, выходы первого и второго элементов HE являются одиннадцатым и двенадцатым выходами блока соответственно, входы первого и второго элементов НЕ являются тринадцатым и четырнапдатым выходами блока соответственно, шины нулевого потенциала и питания являются пятнадцатым и шестнадцатым выходами блока соответственно.

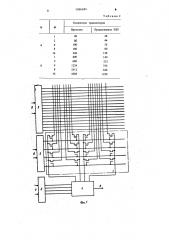

На фиг. 1 приведена схема ПЗУ; на

30 фиг. 2 — схема блока формирования логических функций двух переменных, Устройство содержит матрицу 1 запоминающих элементов, дешифратор строк 2 и столбцов 3, коммутатор 4 столбцов, блок 5

35 формирования логических функций двух переменных, три группы адресных входов

6 — 8 и выход 9. Блок формирования логических функций двух переменных содержит два элемента НЕ 10, элементы ИСКЛЮ—

ЧАЮЩЕЕ JIH 11 и ЭКВИВАЛЕНТНОСТЬ 12, но четыре элемента И 13 и ИЛИ 14. Полный набор логических функций (У l — У16) двух входных переменных (Al, А2) следующий: Уl = А1ЛА2; У2 = А1ЛА2; УЗ

45 = А1АА2 У4 = А1АА2. У5 = А11/А2

У6 = А1ЧА2; У7 = A1VA2; У8 = A I VA2;

У9 = AlAA2VA1AA2; У10 = А1ЛА2ЧА1ЛА2;

Уll = Al; У12 = А2; У13 = Аl; У14 = А2;

У15 = 0; У16 = 1.

Постоянное запоминающее устройство работает следующим образом.

Разряды кода адреса 6 и 7 поступают соответственно на входы дешифраторов строк

2 и столбцов 3, оставшиеся два разряда кода адреса 8 поступают на входы блока 5 формирования логических функций. При этом становятся проводящими запоминающие элементы той строки матрицы 1, которые соединены с выходом дешифратора 2 строк, принявшим

3 10966 состояние логической, "1" при данном коде адреса, и открывается тот вход из первой группы входов коммутатора столбцов, который соединен с выходом дешифратора 3 столбцов, принявшим при данном коде адре- 5 са состояние логической "1". При этом состо. яние второго входа запоминающего элемента

Р. находящегося на пересечении "выбранных" строки и столбца, передается на выход устройства 9. Состояние второго входа этого >0 запоминающего элемента определяется при данном. коде адреса той логической функции из У1-У16, соответствующий которой выход блока 5 формирования подключен к второму входу выбранного запоминающего эле- 15 мента. Эти связи являются программируемыми, т.е. формируются в соответствии с размещаемой в ПЗУ информацией.

Для каждой группы из четырех адресов, соответствующей одинаковому значению кода 20 адреса на входах 6 и 7 и разным значениФ ям кода адреса на входах 8 (А1, А2), определяется логическая функция (У1 — У16), . при одиночном значении которой разряд слова имеет значение логической "1". Соответ- 25 ствующий данной логической функции выход блока 5 формирования соединяется с вторым входом выбранного запоминающего элемента.

В табл. 1 приведены примеры программирования. 30

Блок 5 формирования логических функций в общем случае может иметь 1, 2, 3 ... входов. Однако наименьшие затраты оборудования для устройства в целом получаются в случае, когда число входов блока равно двум, Технико- экономические преимущества предлагаемого устройства можно оценить следующим образом.

И

Для реализации ПЗУ емкостью Мх2 бит (N — разрядность адреса, M — разрядность <щ

94 4 дова) в соответствии с прототипом требуется следующее количество транзйсторов: для каждого дешифратора при условии равного распределения адресных входов между дешифраторами "(2 (2 — + 1) транзисторов, т.е.

tt для двух дешифратороа Ц (2- +1) транэисй

2 торов (это оборудование не зависит от раз рядности ПЗУ); для запоминающей матрицы

2" транзисторов на каждый разряд ПЗУ; для коммутатора столбцов 2 "1 транзисторов на каждый разряд ПЗУ.

Суммарное количество транзисторов в таком

ПЗУ равно й(2 + 1) +М(2 +2) (1)

И(2

В предложенном ПЗУ вводится блок формирования логических функций от двух адресных разрядов. Затраты оборудования на этот блок составляют 26 транзисторов. При равномерном распределении оставшихся N — 2 разрядов между дешифраторами строк и столбцов для реализации дешифраторов требуется ( — 2) (2 + 1) транзисторов. Количество транзисторов в запоминающей матрице на, н-г один разряд равно .2 и J2-1 HJ2-а

2 х 2

1 4

Для коммутатора столбцов требуется й(2-1

М 2 транзисторов. Общее количество транзисторов в предложенном ПЗУ равно

Щ2-< а-2 HI2-4 ,26+ (N — 2) (2 + 1) + М (2 + 2 ) (2)

В табл. 2 приводятся затраты оборудования, рассчитанные по формулам (1),и (2).

Иэ таблицы видно, что оборудование предложенного ПЗУ по сравнению с прототипов при больших значениях N и М уменьшается почти в четыре раза.

Таблица 1

:1 0

0 1

1 1

0 0

1 0

0 1

1 0

0 1

1 1

0 0

0

1

0 (УЗ А1ЛА2) 12 (У12 = А2) 10 (У10. A1AA2V 1ЛА2) 1

4

16

4

16

3 09Ü694

409

1224

2312

4488

Таблица 2

38

56

128

212

356

644

1220

1096694 фаа.Р

ВНИИПИ Заказ 3833/39 Тираж 575 Подписное

Филивл ППИ "Патвкт", г.Уагород, уп.Проектная, 4