Устройство формирования точной оценки измеряемого параметра

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ФОРМИРОВАНИЯ ТОЧ .НОЙ ОЦЕНКИ ИЗМЕРЯЕМОГО ПАРАМЕТРА, содержащее синхронизатор, последовательно соединенные первый регистр . и перзаЛ ключ, второй ключ, последовательно соединенные второй регистр и блок сравнения, выход которого подключен ко входу записи второго регистра , прячем первый выход синхронизатора подключен к управляющему входу первого ключа, отличающее .ся тем, что, с целью повышения точиости измерений,введены последовательно соединенные третий. Четвертый , пятый, щестой регистры, третий ключ, первый сумматор, первый вычитатель , первый умножитель, делитель, второй умножитель, второй сумматор ; и коммутатор, выход которого является выходом устройства, в строСйрующйй вход подключен к второму выходу синхронизатора, первый блок памяти, выход которого соединен с вторым входом второго умножителя, причем уп равляющие входы третьего, четвертого 1 и пятого регистров объединены и под7 дя ., 7j... ; yj fe... ключены к третьему выходу синхронизатора, выход третьего регистра через седьмой регистр подключен к сигнальному входу второго ключа, выход второго регистра через последовательно соединенные четвертый ключ и третий умножитель подключен к второму входу первого вычитателя,управлякицие входы второго, третьего и четвертого ключей объединены и соединены с первым выходом синхронизатора/ входы записи первого, шестого и седьмого регистров соединены с выходом блока сравнения, выход третьего ключа через второй вычитатель подключен к второму входу делителя, вторые входы втос S рого вычитателя и первого сумматора подключены к выходу второго ключа, U) выход первого ключа через четвертый умножитель подключен к вторым входам коммутатора и второго сумматора, а также второй блок памяти, выход кото рого подключен к второму входу чет- g вертого умножителя, дешифратор, выход которого подключен к управляющетлу входу кокмутатора, первый вход дешифратора объединен с первым входом четвертрго умножителя, причем четвертый выход синхронизатора подключен к сигнальному--входу первого регистра, ся со вход третьего регистра является информационным входом устройства формирования точной оценки измеряемого 4 параметра, первый вход синхронизатора и вход установки в ноль второго, третьего, четвертого и пятого регистров объединены и являются входом пилот-сигнала, второй вход синхрони затора является входом синхроимпульсов , а третий вход синхронизатора и второй вход д хшфратора объединены и Являются входами установки числа обрабатываемых отсчетов.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

3(5g G 01 S 13 16

ОПИСАНИЕ ИЗОБРЕТЕН

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3576084/18-09 (22) 05.04.83 (46) 30.06.84. Вюл. Р 24 (7.2) A.À. Чумаченко, Н.В. Долженков, С.Л. Голинец и В.С. Прокопенко (71) Харьковский ордена Ленина авиационный институт им. Н.Е. Жуковского (53) 621.396.96(088.8) (56) 1. Сколник N. Введение в технику радиолокационных систем. Под ред. К.Н. Трофимова. Пер. с англ. М., Мир, 1965.

2. Авторское свидетельство СССР

Р 930219, кл. G 01..Р 10/04,.

23.05.82 (прототип) . (54)(57) УСТРОЙСТВО ФОРМИРОВАНИЯ ТОЧ-.

НОЙ ОПЕНКИ ИЗМЕРЯЕМОГО ПАРАМЕТРА

;содержащее синхронизатор, последовательно соединенные первый регистр и первый ключ, второй ключ, последовательно соединенные второй регистр и блок сравнения, выход которого под-. ключен ко входу записи второго регис-. тра, причем первый выход синхронизатора подключен к управляющему входу первого ключа, о т л и ч а ю щ е е.с"я тем, что, с целью повышения точности. измерений, введены последовательно соединенные третий, четвертый, пятый, шестой регистры, третий ключ, первый сумматор, первый вычитатель, первый умножитель, делитель, второй. умножитель, второй суьаеатор и коммутатор, выход которого является выходом устройства, в стробирующий вход подключен к второму выходу синхронизатора, первый блОк памяти, выход которого соединен с вторым входом второго умножителя, причем уп равляющие входы третьего, четвертого

H пятого регистров объединены H под„„SU„„1100594 А ключены к третьему выходу синхронизатора, выход третьего регистра через седьмой регистр подключен к сигнальному входу второго ключа, выход второго регистра через последовательно соединенные четвертый ключ и третий. умножитель подключен к второму входу первого вычитателя,управляющие входы второго, третьего и четвертого ключей объединены и соединены с первым выходом синхронизаторами входы записи первого, шестого и седьмого регистров соединены с выходом блока сравнения, выход третьего ключа через второй вычитатель подключен к второму входу делителя, вторые входы второго вычитателя и первого сумматора @ подключены к выходу второго ключа, выход первого ключа через четвертый умножитель подключен к вторым входам коммутатора и второго сумматора, атакже второй блок памяти, выход которого подключен к второму входу четвертого умножителя, дешифратор, выход которого подключен к уйравляющему входу коммутатора, первый вход дешифратора объединен с первым входом четвертого умножителя, причем четвертый выход синхронизатора подключен к сигнальному:входу первого регистра, вход третьего регистра является информационниа входом устройства формирования точной оценки измеряемого параметра, первый вход синхронизатора и вход установки в ноль второго, третьего, четвертого и пятого регистров объединены и являются входом пилот-сигнала, второй вход синхрони затора является входом синхроимпульсов, а третий вход синхронизатора и второй вход дешифратора объединены и являются входами установки числа обрабатываемых отсчетов.

1100594

Изобретение относится к радиотехнике и может быть использовано для формирования точной оценки измеряемого параметра в многоканальных измерйтельных системах.

Известен широкий класс радиотехни- 5 ческих устройств; формирующих резуль-. тат измерения — оценку измеряемого параметра " — путем сравнения уровней выходных сигналов И .параллельных каналов оценивания, каждый из которых10 настроен на одно из возможных значе-. ний параметра В, т - ТМ

Известен пеленгатор, содержащий последовательно соединенные остронаправленную сканирующую антенну, уст- 15 ройство обработки и индикатор. Устройство обработки сигналов в данном пеленгаторе содержит последовательно соединенные смеситель и усилитель промежуточной частоты, к выходу кото-20 рого подключены объединенные по входу N идентичные цепочки, состоящие иэ узкополосного фильтра и амплитудного детектора, выходы всех И цепочек

1 подключены к N входам индикатора.

Решение о наличии или отсутствии сигнала выносится человеком-оператором на основе наблюдения всей совокупности спектральных составляющих на экране индикатора (1).

Однако быстрая утомляемость опера- тора ведет к большой вероятности пропуска пеленгуемых сигналов °

Наиболее близким к предлагаемому является устройство формирования точной оценки измеряемого параметра, содержащее синхронизатор, последовательно соединенные первый регистр и первый ключ второй ключ, последова- тельно соединенные второй регистр и блок сравнения, выход которого под-.. ключен к входу записи второго регист-. ра, причем первый выход синхронизатора подключен к управляющему входу первого ключа (2).

Однако данное устройство характе- 45 ризуется низкой точностью измерения, определяемой шагом дискретизации.

Бель изобретения — повышение точности измерений.

Поставленная цель достигается тем, 50 что в устройство формирования точной ,оценки измеряемого параметра, содержащее синхронизатор, последовательно соединенные первый регистр и первый ключ, второй ключ, последовательно со- - 55, единенные второй регистр и блок сравнения, выход которого подключен ко входу записи второго регистра, причем первый выход синхронизатора подключен к управляющему входу первого ключа, введены следовательно соединенные третий, четвертый, пятый, шестой регистры, третий ключ, первый сумматор, первый вычитатель, первый умножитель, делитель, второй умножитель, второй сумматор и коммутатор, 65 выход которого является выходом устройства а стробирующий вход подключен к второму выходу синхронизатора, первый блок памяти, выход которого соединен с вторым входом второго умножителя, причем управляющие входы третьего, четвертого и пятого регистров объединены и подключены к третьему. выходу синхронизатора, выход третьего регистра через седьмой регистр подключен к сигнальному входу второго ключа, выход второго регистра через последовательно соединенные четвертый ключ и третий умножитель подключен к второму входу первого вычитателя, управляющие входы второго, третьего и четвертого ключей объединены и соединены с первым выходом синхрбниэатора, вход. записи первого, шестого и седьмого регистров соединены с выходом блока сравнения, выход третьего ключа через второй вычитатель подключен к второму входу делителя, вторые входы второго вычитателя и первого сумматора подключены к выходу второго ключа, выход первого ключа через четвертый умножитель подключен к вторым входам коммутатора и второго сумматора, а также второй вход блока памяти, вы-. ход которого подключен к второму входу четвертого умножителя, дешифратор, выход которого подключен к управляющему входу коммутатора, первый вход дешифратора объединен с первым входом четвертого умножителя, причем четвертый выход синхронизатора подключен к сигнальному входу первого регистра, вход третьего регистра является информационным входом устройства формирования точной оценки измеряемого параметра, первый вход синхронизатора и входы установки в ноль второго, третьего, четвертого и пятого регистров объединены и являются входом пилот-сигнала, второй вход синхронизатора является входом синхроимпульсов, а третий вход синхронизатора и второй вход дешифратора объединены и являются. входами установки числа обрабатываемых отсчетов.

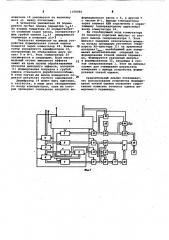

На фиг.1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 - синхронизатор, пример выполнения.

Устройство (фиг.1) содержит синхронизатор 1, первый 2, второй Э, третий 4, четвертый 5, пятый 6, шестой 7 и седьмой 8 регистры, блок 9 сравнения, первый 10, второй 11, третий 12 и четвертый 13 ключи, дешифратор 14, первый блок 15 памяти, первый умножитель 16, первый вычитатель 17, второй умножитель 18, первый сумматор 19, второй вычитатель 20, третий умножитель 21, делитель 22, второй сумматор 23, коммутатор 24, второй блок 25.памяти, четвертый умножитель 26.

1100594

Синхронизатор (фиг.2) содержит ключ 27, элемент 28 задержки 3, счетчик 29, компаратор 30, RS-триггер 31, формирователь 32 и элемент

ИЛИ 33.

На третьем входе синхронизатора, 5

1 задают число N-i, oïðåäåëÿþùåå объем массива дискретных отсчетов, подлежащих обработке.

Устройство формирования точной оценки измеряемого параметра работа- )p ет следующим образом.

В момент t = 0 на первый вход синхронизатора 1 подается пилотсигнал, предваряющий во времени поступление группы информационных чи- сел, соответствующих входным отсчетам. Этот сигнал записывает в счетчик 29 синхронизатора 1 число -1 и переводит RS-триггер 31 синхронизатора 1 в состояние 1 на инверсном выходе. Ключ 27 синхронизатора 1 от- 20 крывается, разрешая прохождение N сопровождающих информацию синхроимпульсов с первого входа синхронизатора 1 на входы записи третьего 4, четвертого 5 и пятого 6 регистров. 25

Пилот-сигналом также обнуляются третий 4, четвертый 5, пятый 6 и второй

3 регистры. Па сигнальный вход тре,,тьего регистра 4 подаются числа, соответствующие входным дискретным отсчетом (у 1, ф =I,N, а на второй вход синхронизатора 1 - сопровождающие эти числа синхроимпульсы, которые проходят на входы записи третьего 4, четвертого 5 и пятого 6 регис- З5 тров и управляют процессом записи информации. В третий регистр 4 записывается очередной у входной отсчет, в четвертый 5 и пятый 6 регистры — предшествующий и еще более ранний входной отсчет. Отсчет, содер- 4О жащийся в четвертом регистре 5, участвует в процедуре обнаружения наи-" большего (экстремального) отсчета.

Счетчик 29 синхронизатора 1 подсчитывает количество синхроимпульсов, со- 45 провождающих информацню. В первый регистр 2 с выхода счетчика 29 в процессе выполнения процедуры обнаружения экстремального отсчета помещается число, соответствующее расстоянию (a числе интервалов дЛ между отсчетами) наибольшего. входного отсчета от нижней границы значений измеряембго параметра М. 3а держкой сигнала в элементе 28 задер« жки обеспечивается смена показаний счетчика 29 синхронизатора 1 только после завершения перезаписи информации в третьем 4, четвертом 5 и пятом 6 регистрах. Когда в четвертом регистре 5 находится первый из мас- 60 сива обрабатываемых входных отсчетов, счетчик 29 синхронизатора 1 имеет на выходе число О, т.е. имеет место запаздывание показаний счетчика 29 синхронизатора 1 на единицу по сравнению с числом поступивших на вход устройства формирования точной оценки входных отсчетов.

Процедура обнаружения наибольшего отсчета. выполняется следующим образом.

Число с выхода четвертого регистра 5 поступает на объединенные входы блока 9 и второго регистра 3. На второй вход блока 9 сравнения поступает число из второго регистра 3.

Если новое число превышает хранящееся во втором регистре 3 значение, выполняется запись содержимого четвертого регистра 5 во второй регистр

3 и показаний счетчика 29 синхронизатора 1 в первый регистр 2. Чтобы в процедуре обнаружения приняли участие все N чисел входного массива, на входы записи третьего 4, четвертого

5 и пятого,6 регистров необходимо подать (И+1) импульс. Дополнительный (N+I) -й импульс, обеспечивающий-участие в процедуре обнаружения N-ro входного отсчета, формируется на выходе компаратора 30 синхронизатора

1 в момент достижения счетчиком 29, показания (N-I).

По завершению процедуры обнаружения RS-триггер 31 синхронизатора 1 устанавливается в состояние логического нуля на инверсном выходе, запрещая прохождение каких-либо,(помеховых) импульсов через ключ 27 ° При этом в седьмом 8, втором 3 и шестом

7 регистрах оказываются наибольший и два соседних к нему входные отсчеты, в первом регистре 2 — число L определяющее расстояние в единицах

8h от нижней границы значений измеряемого параметра .до наибольшего отсчета. Далее начинается вычисление поправки к грубой оценке параметра, в которую может быть пересчитан номер максимального отсчета.

В момент переворота RS-триггера

31 синхронизатора 1 открываются первый 10, второй 11, четвертый 13 и третий 12 ключи.

В первом сумматоре 19 выполняется сложение чисел, соответствующих соседним по отношению к максимальному отсчетам У(„и У <+„. В вычитателе 20 формируется разность У,,- У . В третьем умножителе 21 вйчисляется удвоенное значение амплитуды максимального отсчета. Второй вычитатель

20 формирует разность 2У -У,„ -У „, которая затем удваивается в первом умножителе 16, делитель 22 формирует нормированную поправку

Yl i1 уб,-1 д "Л =

2(- „- .„) () к грубой оценке параметра (определяющейся номером наибольшего отсчета) .

Для пересчета к истинному значению нормированная поправка во втором ум1100594 ножителе 18 умножается на величину шага д между отсчетами.

В четвертом умножителе 26 формируется гр„ бая оценка параметра L@84 .

Во втором сумматоре 23 осуществляется сложение кодов чисел, соответству- 5 щих грубой оценке Ь 43 измеряемого параметра и поправки d3d"Я

Результат измерения на выход устройства Формирования точной оценки подается через коммутатор 24. Комму- 10 татор управляется дешифратором 14, настроенным ha обнаружение двух чи" сел: О и N-1. Роль коммутатора 24 заключается в следующем. Если максимальный отсчет выходного эффекта лежит на краю группы обрабатываемых отсчетов выходного эффекта, алгоритм (1) формирования поправки к грубой оценке становится неработоспособном.

В этом случае йа вйход измерителя подается результат грубого оценивания.

Дешифратор 14 может быть выполнен, в частности, в виде двух объединенных по входу компараторов, один из которых проверяет совпадение входного информационного числа с О, а другой = с числом N-1. Выходы компараторов через элемент ИЛИ подключены к управляющему (одноразрядному адресному) входу коммутатора 24.

На стробирующий вход коммутатора

24 подается короткий импульс со второго выхода синхронизатора 1. Этот импульс задержан относительно момента начала процедуры уточнения (переворота RS-триггера 31) на временной интервал „„, необходимый для завер- . шения вычйсмлйтельных операций по формированию точной оценки параметра. Формируется указанный импульс в формирователе 32, входящем в состав синхронизатора 1. Этот же импульс служит для считывания результата измерения с выхода устройства формирования точной оценки, Сравнительный анализ показывает, что использование устройства форыирования точной оценки позволяет существенно повысить точность оценки измеряемого параметра..1100594 ца в8

А

Составитель В.Родзивилов

Техред Л. Коцюбняк Корректор Л.Пилипенко

Редактор Н. Кищтулннец

Филиал ППП Патент, Г. Ужгород, ул. Проек уая, 4

Заказ 4577/Зб Тираж 711 Подписное

ВНИИПИ Государственного комитета СССР. по делам изобретений и открытий

113035, Москва, Ж35, Раушская наб., д. 4/5