Сумматор

Иллюстрации

Показать всеРеферат

C3WIATOP, содержащий первый транзистор с каналом р-типа, затвор которого соединен с истоком второго транзистора с каналом р-типа и входом первого инвертора, выход которого соединен с затвором третьего транзистсфа с каналом П -типа и истоком четвертого транзистора с каналом П-типа, вход второго инвертора соединен со стоками первого, второго,, третьего/и четвертого транзисторов, затворами пятого, шестого транзисторов с каналами р -типа и седьмого транзистора с каналом п -типа, вьпсод второго инвертора подключен к зат-. ворам восьмого, девятого транзисторов с каналами Л -типа и десятого транзистора с каналом р -типа, истоки первого и третьего транзисторов соединены с затворами второго и четвертого транзисторов и истоками шестого и девятого транзисторов, истоки пятого и восьмого транзисторов соединены с истоками седьмого и десятого транзисторов, сток шестого транзистора подключен к стокам седьмого , девятого .и десятого транзисторов , отличающийся тем, что, с целью упрощенияj в него введены одиннадцатый и двенадцатый транзисторы , причем исток одиннадцатого транзистора с каналом р-типа соединен с входом второго инвертора,исток две (Л надцатого транзистора с каналом П-типа соединен с выходом второго инвертора, затворы одиннадцатого и двенадцатого транзисторов соеди- . нены с истоком пятого транзистора и входом переноса, стоки одиннадцатого и двенадцатого транзисторов соединены со стоками пятого, восьмого транзисторов и выходом суммы, затворы первого и второго транзисторов 35 подключены соответственно к первому о . и второму информационным входам, а сток шестого транзистора - к выходу переноса.

СОЮЗ СОВЕТСКИХ

ЮЦ Ю

РЕСПУБЛИН

6% (1И

gag С 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3537758/18-21 (22) 11 01.83 (46) 30.06.84. Бюл. У 24 (72) С.Н.Лубянов, В.К.Прядилов и С.С.Устинов (71) Московский ордена Трудового

Красного. Знамени инженерно-физический институт (53) 621.375.083(088.8) (56) 1. Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств.

М., "Советсткое радио", 1975, с.45, рис. 1 ° 43.

2. Заявка Японии Ф 55-1619, кл. G 06 F 7 /50, 1980 (прототип). (54)(57) СУММАТОР, содержащий первый транзистор с каналом р-типа, затвор которого соединен с истоком второго транзистора с каналом р-типа и входом первого инвертора, выход которого соединен с затвором третьего транзистора с каналом и -типа и истоком четвертого транзистора с каналом

ll-тяпа, вход второго инвертора соединен со стоками первого, второго, третьего,и четвертого транзисторов, затворами пятого, шестого транзисто- . ров с каналами р -типа и седьмого транзистора с каналом и -типа, выход второго инвертора подключен к затворам восьмого, девятого транзисторов с каналами 11 -типа и десятого транзистора с каналом р -типа, истоки первого и третьего транзисторов соединены с затворами второго и чет- вертого транзисторов и истоками шестого и девятого транзисторов, истоки пятого и восьмого транзисторов соединены с истоками седьмого и десятого транзисторов, сток шестого транзистора подключен к стокам седьмого, девятого и десятого транзисторов, отличающийся тем, что, с целью упрощения; в него введены одиннадцатый и двенадцатый транзисторы, причем исток одиннадцатого транзистора с каналом р-типа соединен с входом второго инвертора,исток двенадцатого транзистора с каналом

A-типа соединен с выходом второго инвертора, затворы одиннадцатого и двенадцатого транзисторов соединены с истоком пятого транзистора и входом переноса, стокй одиннадцатого и двенадцатого транзисторов соединены со стоками пятого, восьмого транзисторов и выходом суммы, затворы первого и второго транзисторов подключены соответственно к первому .и второму информационным входам, а сток шестого транзистора - к выходу переноса.

1 .110062

Изобретение относится к импульсной технике и может быть использовано при построении устройств цифровой автоматики и вычислительной техники.

Известен сумматор на дополняющих

ИДП-транзисторах, содержащий 28 ИДПтранзисторов (1) .

Недостатком известного сумматора является сложность, т.е. большое количество транзисторов. 10

Ниаболее близким к предлагаемому по технической сущности является сумматор на дополняющих МДП-транзисторах, содержащий первый транзистор с каналом р-типа, затвор которого соединен с истоком. второго., транзистора с каналом р -типа и входом первого инвертора, выход которого соединен с затвором третьего транзистора с каналом h -типа и истоком четвер- 20 того транзистора с каналом и -типа, вход второго инвертора соединен со стоками первого, второго, третьего и четвертого транзисторов, затворами пятого и шестого транзисторов с каналами р -типа и седьмого транзистора с каналом 11 -типа, выХод второго инвертора подключен к затворам восьмого, девятого транзисторов с каналами п -типа и десятого транзистора с каналом р -типа, истоки первого и третьего транзисторов соединены с затворами второго и четвертого транзисторов и истоками. шестого и девятого транзисторов, истоки пятого и

35 восьмого транзисторов соединены с истоками седьмого и десятого транзисторов, сток шестого транзистора подключен к стокам седьмого, девятого и десятого транзисторов (2) .

Недостатком такого сумматора является сложность.

Цель изобретения — упрощение сумматора.

Поставленная цель достигается 45 тем, что в сумматор, содержащий первый транзистор с каналом Р-типа, затвор которого соединен с истоком второго транзистора с каналом р -типа и входом первого инвертора, выход 50 которого соединен с затвором третьего транзистора с,каналом П -типа и истоком четвертого транзистора с каналом и -типа, вход второго инвертора соединен со стоками первого, 55 второго, третьего и четвертого транзисторов, затворами пятого, шестого транзисторов с каналами р -типа и седьмого транзистора с каналом П типа, выход второго инвертора подключен к затворам восьмого, девятого транзисторов с каналами П -типа и десятого транзистора с каналом p— типа, истоки первого и третьего транзисторов соединены с затворами второго и четвертого транзисторов и истоками шестого и девятого транзисторов, истоки пятого и восьмого транзисторов соединены с истоками седьмого и десятого транзисторов, сток шестого транзистора подключен к стокам седьмого, девятого и десятого транзисторов, введены одиннадцатый и две. надцатый транзисторы, причем исток одиннадцатого транзистора с каналом р-типа соединен с входом второго инвертора,исток двенадцатого транзистора с каналом и-типа соединен с выходом второго инветора, затворы одиннадцатого и двенадцатого транзисторов соединены с истоком пятого. транзистора и входом переноса, стоки одиннадцатого и двенадцатого транзисторов соединены со стоками пятого, восьмого транзисторов и выходом сумI мы, затворы первого и второго транзисторов подключены соответственно к первому и второму информационным входам, а сток шестого транзисторак выходу переноса.

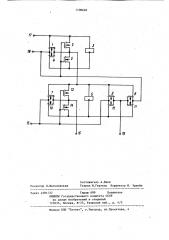

На чертеже приведена принципиальная электрическая схема сумматора.

Сумматор содержит первый транзистор 1 с каналом Р -типа, затвор которого соединен с истоком второго транзистора 2 с каналом р -типа и входом первого инвертора 3, выход которого соединен с затвором третьего транзистора 4 с каналом д -типа и истоком четвертого транзистора 5 с каналом и -типа, вход второго инветора 6 соединен со стоками первого 1, второго 2, третьего 4 и четвертого 5 транзисторов; затворами пятого 7 и шестого 8 транзисторов с каналом р -типа и седьмого транзистора 9 с каналом tl -типа, выход второго инвертора 6 подключен к затворам восьмого 10, девятого 11 транзисторов с каналом 0 -типа и десятого транзистора 12 с каналом р -типа, истоки первого 1 и третьего 4 транзисторов соединены с затворами второго 2 и четвертого 5 транзисторов и истоками шестого 8 н девятого 11 транзисторов, истоки пятого 7 и восьмого 10

1100620

Работа сумматора иллюстрируется таблицей истинности сумматора, дополнительной таблицей состояний транзисторов (символы П и 3 соответствуют . проводящему и запертому состоянию и транзисторов).

Применение предлагаемого изобре-, тения позволяет упростить сумматор и, следовательно, повысить надежность его работы.

Входы Выходы

17 18 19 1 2 4 9 10 11 12 13 14 16 19

Транзисторы

J 5 J 7 )8 ) П 3 П 3 0 О

О 0 О П П П 3 П П 3 П

П. 3 1 0

3 П 3

1 О 0 3 П 3 3 3

3 П

О 1

3 П 3 3 П П 3 1 О

О П 3 П .П 3

П 3 П

П 3 П 3 0 1

1 1 О 3 3 3 П П

3 П 1 0

3 П 0 1,П 3

3 П

П 3 П

3 П 3

1 П П П 3 П

1 3 П 3 3 3

О. О

1 О

3 П 3

3 П 3 П О !

О 1 1 П 3 П П 3

1 1 1 3 3 3 П .П П 3 П П 3

3 П 1 1 транзисторов соединены с истоками седьмого 9 и десятого 12 транзисторов, а сток шестого транзистора 8 подключен к стокам седьмого 9, девятого 1! и десятого 12 транзисторов, исток одиннадцатого 13 транзистора с . каналом р -типа соединен с входом второго инвертора 6, исток двенадцатого 14 транзистора с каналом !! -типаI соединен с выходом второго инверто- !0 ра 6, затворы одиннадцатого 13 и двенадцатого 14 транзисторов соединены с истоками пятого 7 транзистора и входом переноса 15, стоки одиннадцатого 13 и двенадцатого 14 транзисто- !5 ров соединены со стоками пятого 7 и восьмого 10 трайзисторов и выходом суммы 16, затворы первого 1 и второго 2 транзисторов подключены соответственно к первому 17 и второму -18 2р информационным входам, а сток шестого транзистора 8 - к выходу йереноса 19.

Сумматор работает следующим образом. 25

Первым информационным входом 17 является точка соединения затвора первого транзистора 1 с истоком второго транзистора 2 и входом первого инвертора 3. Вторым информационным входом 18 является точка соединения истоков первого 1, третьего 4, шестого 8 и девятого 11 транзисторов.

Входом переноса 15 из предыдущего разряда является точка соединения истоков пятого 7, седьмого 9, вось-. мого 10 и десятого 12 транзисторов с затворами одиннадцатого 13 и двенадцатого 14 транзисторов. Выходом суммы 16 является точка соединени стоков пятого 7, восьмого 10 одиннадцатого 13 и двенадцатого 14 транзисторов, а выходом переноса 19— точка соединения стоков шестого 8, ведьмого 9,, девятого 11 и десятого 12 транзисторов.

Рассмотрим работу сумматора, например, при нулевом наборе входных переменных, т.е. когда на всех входах сумматора нули.

Первый 1, второй 2.и третий 4 транзисторы открываются, а четвертый транзистор 5 запирается, и в точке соединения стоков первого 1, второго 2, третьего 4 и четвертого 5 транзисторов устанавливается нулевой

1 уровень. Затем открываются пятый 7, восьмой 10, одиннадцатый 13 транзисторы, запирается двенадцатый транзистор 14, и на выходе суммы 16 устанавливается нулевой уровень. Одновременно с этим отпираются шестой 8 и девятый 11 транзисторы, а седьмой 9 и десятый 12 транзисторы запираются, и на выходе переноса 19 также устанавливается нулевой уровень.

1100620

Составитель А.Янов

Техред М.Гергель Корректор И. Эрдейи (Редактор Л. Веселовская

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная, 4

Заказ 4581/37 Тираж 699 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5