Устройство для приема сигналов

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПРИЕМА CUf- НАЛОВ, содержагпее первый и второй элементы И, первые входы которых объединены и являются первым входом устройства, а также первый триггер и первый инвертор, вход которого является вторым входом устройства, а выход инвертора подключен ко B-f oрому входу второго элемента И, о тл и ч а ю щ е е с. я тем, что, с целью повышения помехоустойчивости приема, введены три триггера, два элемента И-НЕ, два элемента ИЛИ, элемент И-ИЛИ и второй инвертор, вход которого является первым входбм устройства, а выход второго инвертора подключен к первому входу третьего элемента И, второй вход которого объединен с D -входом первого триггера, входом первого инвертора и вторым входом первого элемента И, выход которого подключен к С-входу Грлл.лгч второго триггера, а ыход второго элемента И подключен к первым входам первого и второго элементов ИЛИ, выход третьего элемента И подключен к С-входу третьего триггера, при этом выходы первого и второго элементов ИЛИ подключены соответственно к Е-входам третьего и.второго триггеров, первый выход второго триггера подключен к первому входу первого элемента И-НЕ, а второй выход второго триггера подключен к второму входу первого элемента ИЛИ и к первому входу второго элемента И-НЕ, выход которого подключен к второму входу первого элемента ИЛИ и к первому входу второго элемента И-НЕ, I выход которого подключен к R-входу (Л четвертого триггера, к 5 -входу которого подключен выход первого элемента И-НЕ, к второму входу которого , а также к второму входу первого элемента ИЛИ подключен первый выход третьего триггера, второй выход которого подключен -к вторсзму входу второго элемента И-НЕ, при этом выход второго инвертора подключен к первому входу элемента , к второму и третьему входам которого подключены выходы четвертого триггера, четвертый вход элемента И-ИЛИ объединен с первым входом 4 устройства, а выход элемента И-ИЛИ j подключен к С-входу первого тригге- { 4 ра и является первым выходом устройства, вторым выходом которого явля- I ется выход первого триггера.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) 3(Я) Н 04 L 1/10 Н 04 L 7 02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ф Ф Фъ лл р

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3382570/18-09 (22) 11.01.82 (46) 30.06.84. Бюл. Р 24 (72) T.Е.Герасименко и Б.С.Корольков (53) 621..394.14(088.8) (56) 1. Справочник по интегральным микросхемам. Под ред.Тарабрина Б.В.

М., "Энергия",1980, с.730, рис.5-236.

2. Шварцман B,О. и др. Теория передачи дискретной информации, N., "Связь", 1980, с. 124, рис.3.29 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ПРИЕМА СИГHAJIOB, содержан(ее первый и второй элементы И, первые входы которых объединены и являются первым входом устройства, а также первый триггер и первый инвертор, вход которого является вторым входом устройства, а .выход инвертора подключен ко второму входу второго элемента И, о тл и ч а ю щ е е с.я тем, что, с целью повышения помехоустойчивости приема, введены три триггера, два элемента И-НЕ, два элемента ЙЛИ, элемент И-ИЛИ и второй инвертор, вход которого является первым входом устройства, а выход второго инвертора подключен к первому входу третьего элемента И, второй вход которого объединен с D -входом первого триггера, входом йервого инвертора и вторым входом первого элемента И, выход которого подключен к С-входу. второго триггера, а выход второго элемента И подключен к первым входам первого.и второго элементов ИЛИ, выход третьего элемента И подключен к С-входу третьего триггера, при этом выходы первого и второго элементов ИЛИ подключены соответственно к R-входам третьего и.второго триггеров, первый выход второго триггера подключен к первому входу первого элемента И-НЕ, а второй выход второго триггера йодключен к второму входу первого элемента ИЛИ и к первому входу второго элемента И-НЕ, выход которого подключен к второму входу первого элемента ИЛИ и к первому входу второго элемента И-НЕ, у выход которого подключен к В.-входу четвертого триггера, к 5 -входу которого подключен выход первого элемента И-НЕ, к второму входу кото- С, рого, а также к второму входу первого элемента ИЛИ подключен первый выход третьего триггера. второй выход которого подключен к второму входу второго элемента И-НЕ, при этом выход второго инвертора подключен к первому входу элемента И-. ИЛИ, к второму и третьему входам которого подключены выходы четвертого триггера, четвертый вход элемента

И-ИЛИ объединен с первым входом устройства, а выход элемента И-ИЛИ подключен к С-входу первого триггера и является первым выходом устрой- ства, вторым выходом которого является выход первого триггера.

1100744

Изобретение относится к технике связи и может использоваться,в высокоскоростной аппаратуре передачи и обработки данных.

Известно устройство для приема сигналов, выполненное в виде 0 триггера, т.е. триггера с однофазным приемом информации (1) .

Известное устройство позволяет работать в высокоскоростных системах, но при работе D -триггера существуют интервалы времени1„ „„,;„, ",,„„;„, когда запись информациойного сйгнала в триггер происходит неоднозначно. Эти ситуации соответствуют близкому расположению переднего Фронта сигнала синхронизации (стробирующего сигнала тактовой частоты) и фронта или среза информационного сигнала. В системах передачи и обработки данных возникают- зада- 20 чи фазирования. когда информационные сигналы и сигналы тактовой частоты синхронны, но не синфазны, т.е. положение импульса стробирования относительно принятого информа- 25 ционного сигнала хотя и постоянно, но произвольно . В этом случае указанные ситуации в D -триггере приводят к ошибкам при приеме сигналов.

Наиболее близким к предлагаемо- gp му является устройство для приема сигналов, содержащее первый и второй элементы И, первые входы которых объединены и являются первым входом устройства, а также пеРвый тРиггеР, Зу и первый инвертор, вход которого . является вторым входом устройства, а выход первого инвертора подключен ,ко второму,.входу второго элемента

И (2) .

Недостатком устройства является недостаточная помехоустойчивость приема, обусловленная наличием ошибок стробирования из-за смещения значащих моментов информационного 45 сигнала.в высокоскоростных системах.

Цель изобретения — повьпаение поме-. хоустойчивости приема..

Цель достигается тем, что в устройство для приема сигналов,.содержащее первый и второй элементы И, первые входы которь1х объединены и являются первым входом устройства, а также первый триггер и первый инвертор, вход которого является входом устройства, а выход первого инвертора подключен ко втброму входу второго элемента И, введены три триггера два элемента И-НЕ, два элемента ИЛИ, элемент И-ИЛИ и второй ин вертор, вход которого является пер- 60 вым входом устройства, а выход второго инвертора.подключен.к первому входу второго элемента И, второй вход которого объединен с O --входом первого триггера, входом первого ин- Я вертора.и вторым входом первого элемента И, выход которого подключен к

С-входу второго триггера, а выход второго элемента И подключен к первым входам первого и второго элементов ИЛИ, выход третьего элемента И подключен к С-входу третъего триггеРа, при этОм выходы ПервОго и втОРого элементов ИЛИ подключены соответственно к И-входам третьего и второго триггеров, первый выход второго триггера подключен к первому входу первого элемента И-НЕ, а второй выход второго триггера подключен к второму входу первого элемента ИЛИ и к первому входу второго элемента

И-НЕ, вЫход которого подключен к второМу входу первого элемента ИЛИ и к первому входу второго. элемента ИНЕ, выход которого подключен к R-входу четвертого триггера, к Б -входу которого подключен выход первого элемента И-НЕ, к второму входу которого, а также к второму входу первого элемента ИЛИ подключен первый выход третьего триггера„ второй выход которого подключен ко второму входу второго элемента И-НЕ, при этомвыход второго инвертора подключен к первому входу элемента И-ИЛИ, ко второму и третьему входу которого подключены выходы четвертого триггера, четвертый вход элемента И-ИЛИ объединен с первым входом устройства, а выход элемента И-ИЛИ подключен к С-входу первого триггера и является первым выходом устройства, вторым выходом которого является выход первого триггера.

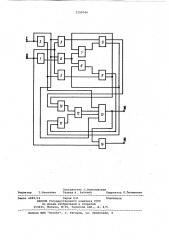

На чертеже приведена структурная электрическая схема устройства приема сигналов..

Устройство для приема сигналов содержит первый 1 и второй 2 инверторы, первый 3, второй 4 и третий 5 элементы И, первый. 6 и второй 7 элементы ИЛИ, первый 8 и второй 9 триггеры, первый 10 и второй 11 элементы И-НЕ..третий триЛ ер 12, элемент

И-ИЛИ 13, D -триггер 14.

Устройство для приема сигналов с неопределенной фазой работает следующим образом.

На первый вход,i устройства поступает сигнал тактовой частоты (тИ) местного генератора, на второй вход ll - информационный сигнал

1ИНФ). На выходе первого элемента

И 3 формируется результат совпадения инверсного сигнала и сигнала

ИНФ. Рассмотрим случай, когда информационный сигнал опережает сигнал тактовой частоты или находится с ним в противофазе. При этом в пределах единичной посылки информацибнного сигнала первым фЬрмируется сигнал на выходе третьего элемента И 5 по

1100744 сравнению с сигналом на выход первого элемента И 3. Сигнал с выхода третьего элемента И 5 поступает на

С-вход второго триггера 9, устанавливая его в состояние "1", Инверсный сигнал с выхода второго триггера 9

5 поступает через второй элемент ИЛИ

7 и запирает первый триггер 8, подтверждая его состояние "О".

Установка триггеров 8 и 9 в состояние "0" производится сигналом с выхода элементов ИЛИ 6 и 7 при совпадении прямого сигнала тактовой частоты и инверсного информационного сигнала на входах второго элемента

И 4. В случае, когда информационный сигнал запаздывает относительно сигнала тактовой частоты или находится с ним в фазе первым в пределах единичной посылки информационного сигнала формируется сигнал на выходе пер- 20 вого элемента И 3 по сравнению с сигналом на выходе третьего элемента И. 5. Сигнал с выхода первого элемента И 3 поступает на С-вход первого триггера 8, устанавливая его 25 в состояние "1". Инверсный сигнал с выхода первого триггера 8 поступает через первый элемент ИЛИ 6 и запирает второй триггер 9, подтверждая его состояние "О". 30

Таким образом, в случае опережения и противофазы на выходе второго триггера 9 формируются импульсы, а выход первого триггера 8 находится постоянно в состоянии"О,"..В случае за- З5 па здывания и Аазы на выходе пеРвого триггера 8 формируются импульсы,а выход второго триггера 9 находится постоянно в состоянии О. В результате совпадения на входах первого элемента И-НЕ 10 прямого сигнала с выхода первого триггера 8 и инверсного сигнала с выхода второго триггера

9 третий триггер 12 устанавливается в состояние 1, в результате совпадения на входах второго элемента И-HE 45

11 прямого сигнала с выхода второго триггера 9 и инверсного сигнала с выхода первого триггера 8 третий триггер 12 устанавливается в состояние "О", Таким образом, при опереже- 50 нии в противофазе третий триггер 12 устанавливается в состояние "О", а при запаздывании и фазе третий триггер 12 устанавливается в состояние "1". Прямой и инверсный сигналы с выходов третьего триггера 12 совместно с прямым и инверсным сигналами тактовой частоты поступают на входы элемента И-ИЛИ 13, на выходе которого в случае опережения и противофазы формируется прямой сигнал тактовой частоты, а в случае запаздывания и фазы — инверсный сигнал тактовой частоты. Этот сигнал явля-. ется выходным сигналом устройства приема сигналов с неопределенной фазой.

Таким образом, на D -.триггере 14 осуществляется нацежный прием информационного сигнала сигналом тактовой частоты, причем в случае запаздывания, так как стробирование на D -триггере 14 осуществляется инверсным сигналом тактовой частоты, то ситуаций, соответствующих момен-. О1 - <р там времени „„ и 4 ; йе возникает. За счет того, что анализ взаимного расположения информационного сигнала и сигнала тактовой частоты производится раньше, чем стробирование на D -триггере 14, на время, равное времени задержки на элементе И-ИЛИ 13, т ° е, большее чем времена, „и Сур которые определяются временем срабатывания только одного элемента совпадения Q Р -триггера 14, то в пред— лагаемом устройстве не возникает си туаций, соответствующих моментам О1 л<О оп в 1 "" on in

При искайениях информационных сиг; налов по длительности 2 -триггер 14 работает без ошибки, если искажение посылки не более величины рассогласования д1 . При искажениях более д 1 возникают ошибки стробирования.

В предлагаемом устройстве допустимое искажение посылки д2=д1+i строба, т.е. значительно выше,чем в известном устройстве, поскольку для рассмотренного случая стробирование производится инверсным сигналом тактовой частоты.

Таким образом, при использовании данного устройства для приема сигналов с неопределенной фазой в результате обеспечения приема тактов с неопределенной фазой уменьшения влияния ошибок стробирования достигается положительный эффект - улучшение одного из основных параметров систем обработки и передачи информации йомехоустойчивости приема и достоверности обработки информации.

1100744

Составитель С,Осмоловский

Редактор Т.Веселова Техред А. Бабинец Корректор Л.Пилипенко

Подписное

Заказ 4499/44 Тираж 635

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул, Проектная, 4