Устройство для приема избыточной информации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПРИЕМА ИЗБЫТОЧНОЙ ИНФОРМАЦИИ, содержащее приемник , вход которого является входом устройства, выход приемника соединён с первым входом вычитателя, через первый блок памяти - с первым входом коррелятора и через первый пороговый селектор - с входом перво го регистра, первым входом декодера и с вторым входом вычитателя, выход вычитателя соединен с входом второго блока памяти, выходы которого соединены с соответствующими первыми входами блока усилителей,первые выходы и второй вход которого соединены соответственно с входами и выходом второго порогового селектора , вторые выходы блока усилителей соединены с соответствующими первыми входами блока сумматоров,вторые входы которого подключены к соответствующим выходам первого регистра, выходы блока сумматоров соединены через третий пороговый селектор с соответствующими вторыми входами декодера г отличающееся тем, что, с целью упрощения устройI ства, в него введены второй .и третий регистры, ключ, счетчик и блок ОТ сравнения, выход декодера соединен с вторым входом коррелятора и через второй регистр с первым входом ключа , выход коррелятора соединен через блок сравнения с вторым входом ключа и через счетчик с первым входом третьего регистра, выход ключа соединен с вторыгч входом третьего регистра, выход которого является выходом устройства. оо сю

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(511 0 08 С 19 28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3586477/18-24 (72) 29.04.83 (46) 07.07.84, Бюл„ Р25 (72) B.A.Àíàìêèí, В.П.Зубков и P.Â.Àíàøêèí (53) 621.398(088,8) (56) 1. бринк Л.М. Теория передачи дискретных сообщений. N., "Советское радио", 1970, с.636, рис.10.1, 2. Бородин Л.Ф. Введение в теорию помехоустойчивого кодирования.

М., "Советское радио", 1968, с.270, рис. 3.03, 3. Авторское свидетельство СССР

Р 824263, кл. G 08 С 19/28, 1979 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ПРИЕМА ИЗБЫТОЧНОЙ ИНФОРМАЦИИ. содержащее приемник, вход которого является входом устройства, выход приемника соединен с первым входом вычитателя, через первый блок памяти — с первым входом коррелятора и через первый пороговый селектор — с входом первого регистра, первым входом декоде- ра и с вторым входом вычитателя, выход вычитателя соединен с входом

„„SU„„1 З A второго блока памяти, выходы которого соединены с соответствующими первыми входами блока усилителей, первые выходы и второй вход которого со единены соответственно с входами и выходом второго порогового селектора, вторые выходы блока усилителей соединены с соответствующими первыми входами блока сумматоров, вторые входы которого подключены к соответствующим выходам первого регистра, выходы блока сумматоров соединены через третий пороговый селектор с соответствующими вторыми входами декодера, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, в него введены второй и третий регистры, ключ, счетчик и блок сравнения, выход декодера соединен с вторым входом коррелятора и через второй регистр с первым входом ключа, выход коррелятора соединен через блок сравнения с вторым входом ключа и через счетчик с первым входом третьего регистра, выход ключа соединен с вторым входом третьего регистра, выход которого является выходом устройства.

1101873

Изобретение относится к области электросвязи и может быть использовано в системах передачи информации при приеме избыточнь1х сигналов в целом, использующих коды больщой мощности, 5

Известно устройство для приема избыточных сигналов в целом, состоящее из умножителей, интеграторов, генераторов опорных сигналов и блока выбора максимального сигнала. L13. 10

Недостатком данного устройства является сложность реализации блока выбора максимального сигнала °

Известна устройство для поэлементного приема сигналов, содержащее приемник, пороговый селектор и декодер 323.

Данное устройство реализуется технически несложно, но отличается низкой помехоустойчивостью. 20

Наиболее близким к предлагаемо— му по технической сущности является устройство для приема избыточной информации, содержащее приемник, вход которого является входом устройства, выход приемника соединен с первым входом вычитателя, через первый блок памяти — с первым входом коррелятора и через первый пороговый селектор — с входом первого регист- 30 ра, первым входом декодера и. с вторым входом вычитателя, выход вычитателя соединен с входом второго блока памяти, выходы которого соединены с соответствующими первыми входами 35 блока усилителей, первые выходы и второй вход которого соединены соответственно с входами и выходом второго порогового селектора, вторые вь1ходы блока усилителей соединены с 4О соответствующими первыми входами блока сумматоров, вторые входы которого подключены к соответствующим выходам первого регистра, выходы блока сумматоров соединены через третий пороговый селектор с соответствующими вторыми входами декодера, выход декодера соединен с первым входом блока регистров, первые выходь-: и вторые входы которых подключены соответственно к вторым входам и к выходам коррелятора, второй выход блока регистров является выходом устройства L3 3.

Недостатком, известного устройства является сложность, обусловленная больщим числом регистров в блоке регистров.

Целью изобретения является упрощение устройства.

Указанная цель достигается тем, 60 что в устройство для приема избыточной информации, содержащее приемник, вход которого является входом устройства, выход приемника соединен с первым входом вычитателя, через первый блок памяти — с первым входом коррелятора и через первый пороговый селектор — с входом первого регистра, первым входом декодера и с вторым входом вычитателя, выход вычитателя. соединен с входом второго блока памяти, выходы которого соеди— нены с соответствующими первыми входами блока усилителей, первые выходы и второй вход которого соединены соответственно с входами и выходом второго порогсвого селектора, вторые выходы блока усилителей соединены с соответствующими первь|ми входами блока сумматоров, вторые входы которого подключены к соответствующим выходам первого регистра, выходы блока сумматоров соединены через третий пороговь и селектор с соответствующими вторыми входами декодера, введены второй и третий регистры, ключ, счетчик и бгок сравнения, выход декодера соединен с вторым входом коррелятора и через второи регистр с первым входом ключа, выход коррелятора соединен через блок сравнения с вторым входом ключа и через счетчик с первым входом третьего регистра, выход ключа соединен с вторым входам третьего регистра, выход которого является выходом устройства.

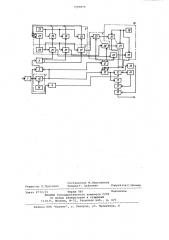

На чертеже представлена структурная схема предлагаемого устройства для приема избыточной информации.

Устройство содержит приемник 1. пороговый селектор 2, вычитатель 3, буоерные блоки 4 и 5 памяти, блок б усилителей, блок 7 сумматоров, регистр 8, пороговые селекторь1 9 и

10, регистр 11, коррелятор 12, декодер 13, блок 14 сравнения, регистр

15. счетчик 16 и ключ 17., Пороговый селектор 2 содержит элемент 18 сравнения и источник 19 порогового напряжения. Блок б усилителей содержит генератор 20 линейно изменяющегося напряжения и усилителя 21. Блок 7 сумматоров содержит сумматоры 22.

Пороговый селектор 9 содержит источник 23 порогового напряжения, элементы 24 сравнения и пороговый элемент 25„ Пороговый селектор 10 содержит источник 26 порогового напряжения и элементы 27 сравнения.

Устройство работает следующим образом.

На вход приемника 1 поступает сложный избыточный сигнал. На выходе приемника 1 появляется (последовательно ) совокупность аналоговых сигналов, соответствующих элементам входного сигнала. Каждый аналоговый сигнал подается на вход порогового селектора 2, а именно на вход элемента 18 сравнения, на другой вход которого постугает пороговое напря1101873 жение от источника 19 порогового напряжения (величина его устанавливается как и в известном устройстве вручную ).

В элементе 18 сравнения осуществляется сравнение величин входных сигналов с пороговым напряжением.

Если величина входного аналогового сигнала меньше величины порогового напряжения, то на выходе элемента сравнения появляется сигнал "0", в противном случае — "1".

В вычитателе 3 из величины двоичного сигнала вычитают величину соответствующего аналогового сигнала.

В результате в декодер 13 последовательно записывается кодовая комбинация, соответствующая посимвольному приему входного сигнала. Декодер 13 после соответствующих операций записывает (последовательно) в регистр 11 двоичную разрешенную кодовую комбинацию, являющуюся ближай:шей к двоичной посимвольной. В регистр 8 памяти также последователь,но записывается и хранится в нем двоичная кодовая комбинация посимвольного приема. B блок 5 буферной памяти записывается и хранится со вокупность аналоговых сигналов. полученных с вычитателя 3. Из блока 5 памяти эти.сигналы параллельно подаются на усилители 21 с регулируемыми коэффициентами усиления.

Запускается генератор 20 линейно изменяющегося напряжения и коэффициент усиления усилителей 21 увеличивается (начальный коэффициент усиления равен 1}. Выходные сигналы усилителей 21 подаются на элементы

24 сравнения, к другим входам которых подключен источник 23 порогового напряжения. 1<ак только в какомнибудь элементе ?4 сравнения выходной сигнал усилителя 21 превысит величину порогового напряжения, то сразу же сработает пороговый элемент 25 и генератор 20 выключается, Усиленные сигналы с выхода усилителей 21 подаются на входы соответствующих одноразрядных сумматоров 22, где суммируются с величинами сигналов, поступающих на другие входы сумматоров с ячеек регистра 8. Далее результирующие сигналы преобразуются в двоичные сигналы посредством элементов 27 сравнения и источника 2б порогового напряжения и параллельно поступают в декодер 13.

Оформированная декодером 13 разрешенная двоичная кодовая комбинация

15 записывается в регистр 11, сбрасывая из него предыдущую кодовую комбинацию.

Одновременно с поступлением в регистр 11 кодовая комбинация поступа29 ет в коррелятор 12, где вычисляется коэффициент корреляции между этой кодовой комбинацией и комбинацией аналоговых величин из блока 4 памяти.

25 Если вычисленный коэффициент корреляции больше предыдущего, то кодовая комбинация из регистра 11 через ключ 17, открывшийся по сигналу из блока 14 сравнения. поступает в регистр 15 памяти. Если коэффициент корреляции меньше предыдущего, то ничего не происходит, и кодовая комбинация, хранящаяся в регистре 11, заменяется на следующую из декодера 13 на очередном такте.

При поступлении на вход коррелятора 12 и-ой по счету кодовой комби-, нации, а значит и на вход счетчика

16, последний выдает сигнал, по которому кодовая комбинация из регист40 ра 15 памяти поступает на выход.

Таким образом, кодовая коМбинация, наиболее близкая к комбинации аналоговых величин, хранящейся в блоке 4 памяти, выдана получателю.

1101873

Составитель М.Никуленков

Техред Т. Дубинчак Корректор С.Мекмар,.

Редактор Л,Гратилло

Подписное

Филиал ППП "Патент", r, Ужгород, ул. Проектная, 4

Эаказ 4772/35 Тираж 569

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д, 4/5