Линия задержки

Иллюстрации

Показать всеРеферат

ЛИНИЯ. ЗАДЕРЖКИ,, содержащая последовательно соединенных ячеек задержки , -каждая из которых содержит последовательно соединенные усилитель с неинвертирующим входом и ключ с запоминающим конденсатором между выходом ключа и общей шиной, входы управления нечетными и четными ключами соединены соответственно с .двумя шинами управления, о т л и ч а ющ а я с я тем, что, с целью уменьшения затухания задерживаемого сигна - .,чч. ла и повышения быстродействия, в нее введены двухпозиционные переключатели и дополнительный усилит ель, .неинвертирующий вход которого подключен к выходу последнего ключа, а выход подключен к своему инвертирующему входу и к выходу устройства, при этом двухпозиционные .переключатели установлены параллельно каждому усилителю , кроме первого и дополнительного , выходы переключателей соединены с инвертирующими входами, а первые входы - с выходами соответствующих усилителей, вторые входы переключателей подключены к выходам последующих усилителей, при этом сосоояние одноименныхвходов нечетных и четных (Л переключателей противофазно, инвертирующий вход первого усилителя соединен с выходом второго усилителя, а выходы управления переключателями подключены к дополнительной шине управления .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) 111) А

З 11 Н 03 Н 7/30 Н 03 К 5 !53

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕН Я " ---, "

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ 3 (21) 3456004/18-21 (22) 22.06.82 (46) 07.07.84. Бюл. № 25 . (72) В.П. Реута (53) 621.316.727(088.8) (56) 1. Авторское свидетельство СССР

¹ 472441, кл. Н 03 Н 7/30, 01.09.72.

2. Авторское свидетельство СССР

N 420095, кл. Н 03 Н 7/30, 12. 06.72 (прототип).. (54)(57) ЛИНИЯ. ЗАДЕРЖКИ, содержащая последовательно соединенных ячеек задержки, каждая из которых содержит последовательно соединенные усилитель с неинвертирующим входом и ключ с запоминающим конденсатором между выходом ключа и общей шиной, входы

4 управления нечетными и четными ключами соединены соответственно с двумя шинами управления, о т л и ч а ющ а я с я тем, что, с целью уменьшения затухания задерживаемого сигнала и повышения быстродействия, в нее введены двухпозиционные переключатели и дополнительный усилитель,,неинвертирующий вход которого подключен к выходу последнего ключа, а выход подключен к своему инвертирующему входу и к выходу устройства, при этом двухпозиционные переключатели установлены параллельно каждому усилителю, кроме первого и дополнительного, выходы переключателей соединены с инвертирующими входами, а первые входы — с выходами соответствующих усилителей, вторые входы переключателей подключены к выходам последующих усилителей, при этом сосоояние одноименных входов нечетных и четных переключателей противофазно, инвертирующий вход первого усилителя соединен с выходом второго усилителя, а выходы управления переключателями подключены к дополнительной шине управления.

1102022

Изобретение относится к устройст- но соединенных ячеек задержки, каждая вам задержки сигнала и мож и может быть из которых содержит последовательно использовано в различных областях соединенные усилитель с неинвертируэлектроники для управляемои задержки ющим входом вхо ом и ключ с запоминающим аналоговых сигналов. 5 конденсатором между выходом ключа и

Известна линия задержки аналоговых общей шиной, входы управления нечетсигналов, содержащая последователь- ными и четными ключами соединены но соединенных ячеек зад "ржки каждая соответственно с двумя шинами управиз которых содержит ключ, например, ления, введены двухпозиционные пена полевом транзисторе, и и конденса- 10 реключатели и дополнительный усилитор памяти, а также о бщий для линии тель неинвертирующий вход которого

У задержки выходнои повтор итель напря- подключен к выходу последнего ключа, жения, а входы управ авления нечетными а выход подключен к своему инвертии четными ключами подключ ены соот- . рующему входу и к выходу устройства, ветственно к двум шинам шинам управления 1 ).15 при этом двухпозиционные переключатели установлены параллельно каждоНедостатками известной линии за- му усилителю, кроме первого и дополдержки являются низкое быстродействие нительного, выходы переключателей и значительное затухание сигнала при соединены с инвертиру щими входами, большом числе Ячеек задеРжки. ОбУслов-20 а первые входы — с входами соответлено это тем, что передача сигнала ствующих усилителей, вторые входы из одной ячейки в другую производит- переключателей подключены к выходам ся через ключи, обладающие конечным последующих усилителей, при этом сосвнутренним сопротивлением, которое, тояние одноименных входов нечетных и четных переключателей противофазно извести стопроцентную передачу сигнала инвертирующий вход первого усилителя из одной ячейки в другую а с ppyroH соединен с выходом второго усилителя, ограничивает минимальное время переа входы управления переключателями дачи этого сигнала. В результате подключены к дополнительной шине уп.чем с большей точностью надо передать 30 р задержанный сигнал, тем меньше должна

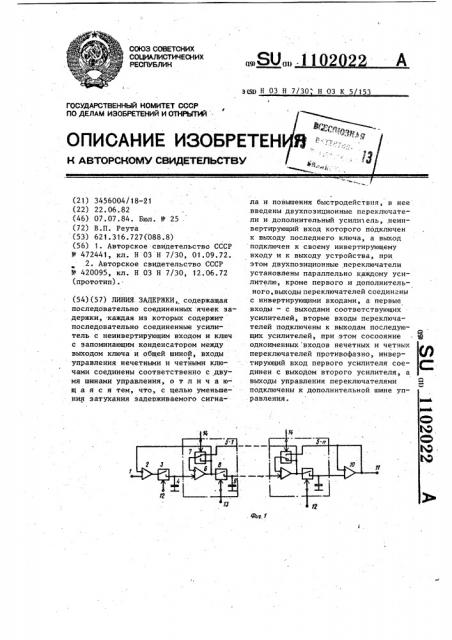

На фиг. 1 приведена схема линии быть частота коммутации ключей.

Наиболее близкои по технич задержки; на фиг. 2 — условная форма и временное расположение импульсов сущности к предлагаемои являет оследова- управления ключами и переключателями. ния задержки, содержащая IIoo 35

Вход 1 линии задержки соединен с .тельно соединенных ячеек задержки, каждая из которых содержит по следова- неинвертирующим входом первого усилии ующий теля 2 нагруженного через ключ 3 на тельно соединенные неинвертирующ "

У усилитель и ключ с запоминаю м ающим кон- запоминающий конденсатор 4. Далее следуют одинаковые по построению денсатором между выходом ключа 40 ния нечетны- ячейки 5-1 — 5-п, конденсатор 4 соеобщей шиной, входы управления н ми и четными ключами соедине ь, нены соот- динен также с входом первой 5-1 ветственно с двумя шинами управ авления . ячейки, содержащей усилитель 6, неустанов- инвертирующий вход которого является а на выходе линии задержки уст 2 . входом ячейки, а инвертирующий— повторитель напряжения 3 45 подключен к выходу двухпозиционного

Недостатками данной линии также переключателя 7 первый вход которого являются невысокое быстродеистви хание сигнала при соединен с выходом усилителя 6 и с значительное затухание сигнала еек за ержки из-за вторым выходом ячеики 5-, п д

5-1 по ключенбольшом числе ячеек задержки го вн т еннего сопротивления ным к инвертирующему входу усилите50 я 2 а второй его вход является ключей что не обеспечивает стопро- ля, а вто

У вторым входом ячейки. Выход усили ентн передачу сигнала из однои и- теля 6 в каждой ячейке подключен чеячейки в другую и ограничивает минио сигнала. рез ключ 8 к конденсатору 9 и к пермальное время передачи этого сигн ель изобретения. — ум

Цел р р — еньшение за- вому выходу ячейки.

55 Нервый выход и второй вход каждои я за е живаемого сигнала и тухания д р предыдущей ячейки 5-1 — 5-п соедиповышение быстродействия. линию иены соответственно с первым входом

Цель достигается тем, что в л сле ователь- и вторым выходом последующей ячеики. задержки, содержащую последовате з 1102022

Первый выход и второй вход последней ячейки 5-и соединены соответственно с неинвертирующим входом дополнительного усилителя IО и с его выходом, объединенным с его инвертирующим входом и с выходом 11 устройства.

Входы управления нечетными ключами подключены к шине управления 12„ входы управления четными ключами подключены к шине управления 13, входы управления переключателями подключены к шине управления 14.

При работе линии задержки входной (задерживаемый) сигнал подается на вход 1 линии задержки, а задержанный

4 (выходной) сигнал снимается с выхода 11, к которому обычно подключается фильтр (не показан) для восстановления огибающей входного сигнала.

Фильтр в общем случае может отсутствовать, например в случае, когда на выходе линии задержки устанавливается аналого-цифровой преобразователь.

Для работы линии задержки на шины управления 12, 13 и 14 подают от внешнего блока управления (не показан) тактовые импульсы (фиг. 2) где частота следования тактовых импульсов равна

1 =—

Входной сигнал с входа 1 через усилитель 2 поступает на разомкнутый ключ 3. При замыкании ключа 3 сигналом с шины 12 к выходу усилителя 2 подключается запоминающий конденсатор 4, который быстро заряжается до амплитуды входного сигнала за счет наличия замкнутой обратной связи через усилитель 6 первой ячейки

5-1, который в режиме заряда запоминающего конденсатора 4 работает как повторитель напряжения. Как только напряжение на запоминающем конденсаторе 4 станет равным входному, т.е. на обоих входах усилителя 2 напряжение станет равным друг другу, усилитель 2 прекратит заряд запоминающего конденсатора 4. Затем ключ 3 сигналом с шины 12 будет разомкнут, после чего сигналом с шины 14 переключатель 7 будет переведен в противоположное состояние, в результате чего усилитель 6 из режима повторителя будет переведен в режим компаратора, а его инвертирующий вход будет подключен через переключатель к выходу усилителя 6 последующей ячейки, у которого в это же время за счет переключения.переключателя 7 последующей ячейки сигналом с шины 14 выход окажется соединенным с инвертирующим входом, т.е. усилитель 6 последующей ячейки будет переведен своим переключателем 7 в режим повторителя напряжения. После этого сигналом с шины

13 будет замкнут ключ 8, который подключит запоминающий конденсатор 9 к выходу усилителя 6, который быстро зарядит запоминающий конденсатор до напряжения на запоминающем конденсаторе 4 за счет наличия обратной связи через усилитель 6 последующей ячейки. После этого сначала сигналом с шины 13 разомкнется ключ 8 через время < (фиг. 2), затем сигналом с шины 14 будут возвращены переключатели 7. Через время, равное ь после прихода первого импульса

2 управления по шине 12, цикл повторится. Все ключи и переключатели ра25 ботают синхронно (фиг. 1 и фиг. 2).

В итоге время задержки линии задержки составит интервал

Т

2 2 (2)

30 при нечетном числе запоминающих конденсаторов, где n — число запоминающих конденсаторов. Если число запоминающих конденсаторов четное,то . = (-" - 1) ii„(3)

Изменением частоты следов» *ия импуль40 сов управления по шинам 12 — 14 можно менять общее время задержки при постоянном числе ячеек линии задержки.

Пр имуществами линии задержки по сравнению с известной являются

45 малое затухание, так как каждый запоминающий конденсатор заряжается до полной амплитуды напряжения на пре- " дыдущем конденсаторе или входе линии задержки и высокое быстродействие, 50 т,е. большая максимальная частота тактовых импульсов, обусловленная малым временем заряда запоминающих конденсаторов.

Эти преимущества объясняются наличием переключателей, которые позволяют каждый усилитель, кроме первого и последнего, использовать в двух режимах работы — в режиме ком1102022

Составитель А. Титов

Редактор Н. Яцола Техред M.Íàäü Корректор Г. Решетник

Заказ 4782/43 Тираж 862 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 паратора напряжения.или в режиме повторителя напряжения, в результате чего каждый запоминающий конденсатор при заряде оказывается включенным в замкнутое следящее устройство выборки и запоминания.