Цифровой фазовращатель

Иллюстрации

Показать всеРеферат

ЦИФРОВОЙ ФАЗОВРАЩАТЕЛЬ по авт.св. 748840, отличающийся тем, что, с целью повышения его надежности в работе, в него введены буферный блок, два элемента И-НЕ, инвертор и D -Триггер, причем сигнальный вход D-триггера соединен с выходом сопряженного Тактируемого фильтра с памятью, тактовый вход .D -триггера соединен с входом счетчика , а инверсный выход D-триггера подключен X входу первого элемента И-НЕ,второй вход которого через инвертор соединен с первым входом второго элемента И-НЕ,выход первого элемента И-НЕ подключен к входу записи буферногоблока , выход второго элемента И-НЕ соединен с тактовым входом буферного блока, выходы которого подключены к соответствующим управляющим входам фазозадающего блока. (Л to о ю О)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 748840 (21) 3572580/18-21 (22), 04.04.83 (46 ) 07.07.84. Бюл. Р 25 (72) В.A.Глаголев и С.Н.Малюков (53) 621. 317.77(088.8) (56) 1. Авторское свидетельство. СССР

9 748840, кл. Н 03 K 5/153, 1978.

Ф (5 4 ) (57 ) ЦИФРОВОЙ ФАЗОВРА АТЕЛЬ по авт.св. Р 748840, о т л и ч а юшийся тем, что, с целью повьааения его .надежности в работе, в него введены буферный блок, два элемента

„„SU„„102026 А

3(51) Н 03 К 5/13; Н 03 К 5/153;

Н 03 K 13/02

И-НЕ, инвертор и 9 -триггер, причем сигнальный вход 9 -триггера соединен с выходом сопряженного тактируемого фильтра с памятью, тактовый вход

0 -триггера соединен с входом счет чика, а инверсный выход Р -триггера подключен к входу первого элемента

И-НЕ, второй вход которого через инвертор соединен с первым входом второго элемента И-НЕ, выход первого элемента

И-НЕ подключен к входу записи буферного блока, выход второго элемента И-HE соединен с тактовым входом буферного блока, выходы которого подключены к соответствующим управляющим входам фазозадающего блока. 2

1102026

Изобретение относится к радиотехнике и может использоваться в.качестве исполнительного элемента систем автоматического регулирования по фазе, частоте или временной задержке.

По авт.св. М 748840 известен цифро 5 вой фазовращатель, содержащий счетчик, вход которого подключен к шине опорного сигнала, блок сравнения, нходы которого соединены с выходами счетчика и фазозадающего блока, причем выходы блока сравнения подключены к сигнальным входам двух тактируемых фильтров с памятью, тактовые входы которых соединены со счетным входом счетчика, а ныходы тактируемых фильтров с памятью подключены к входам триггера с раздельным управлением f13.

Недостатком известного устройства является его низкая надежность в работе. Управляющий код0 „ может 20 поступать на вход фазозадающего блока как параллельно, так и последовательно в произвольные моменты времени, что приводит к сбоям в работе. 25

Цель изоберетния — повышение надежности.

Указання цель достигается тем, что в цифровой фазовращатель, содержащий счетчик, вход которого подклю- чен к шине опорного сигнала, блок сравнения, входы которого соединены с выходами счетчика и фазозадающего блока, а выходы блока сравнения подключены к сигнальным входам двух тактируемых фильтроь с памятью, тактовые входы которых соединены со счетным входом счетчика, выходы тактируемых фильтров с памятью подключены к входам триггера с раздельным управлением, введены буферный 40 блок, два элемента .И-НЕ, иннертор и D -триггер, причем сигнальный вход D -триггера соединен с выходом сопряженного тактируемого фильтра с памятью, тактовый ьход Э вЂ” тригге- 45 ра .соединен с входом счетчика, а инверсный выход D -триггера подключен к входу первого элемента И-НЕ, второй вход которого через инвертор соединен с первым входом второго 50 элемента И-НЕ, выход первого элемента И-НЕ подключен к входу записи буферного блока, выход второго элемента И-HE соединен с тактовым входом буфеРного блока, выходы которого подключены к соответствующим управляющим входам фазозадающего блока.

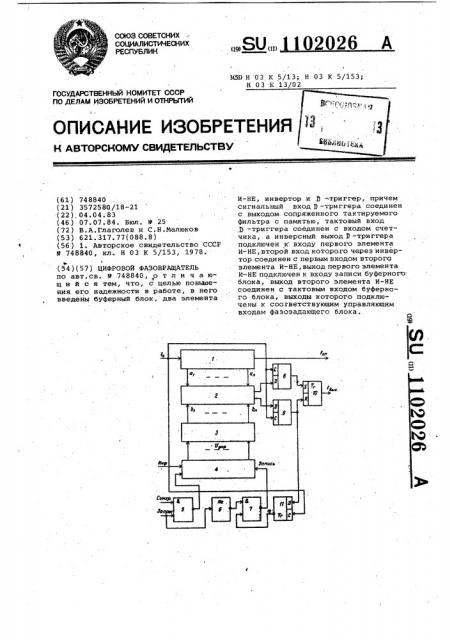

На чертеже приведена.функциональная схема предлагаемого устройства.

Цифровой фазонращатель содержит счетчик 1, выходы которого подклю- 60 чены к первым входам блока 2 сравнения, вторые входы которого соединены.. с выходами фазозадающего блока 3, буферный блок 4, элемент И-НЕ.5, инвертор 6, элемент И-НЕ 7, при 65 этом выходы блока 2 сравнения подключены к сигнальным входам двух тактируемых фильтров с памятью — основного 8 и сопряжен11ого 9, тактовые входы которых соединены с входом счетчика 1, а выходы подключены к входам триггера 10 с раздельным управлением, D --триггер 11; причем сигнальный ьход D -триггера 11 соединен с выходом сопряженного тактируемого фильтра 9 с памятью, тактовый вход D †тригге 11 соединен с входом счетчика 1, а инверсный выход

D †тригге 11 подключен к входу элемента И-НЕ 7, второй вход которого через иннертор 6 подклк|чен к входу элемента И-НЕ 5.Д выход элемента И-НЕ 7 подключен к входу записи буферного блока 4, выход элемента

И-HE 5 соединен с тактовым входом буферного блока 4, выходы которого подключены к соответствующим управляющим входам фазозадающего блока 3.

Цифровой фазонращатель работает следующим образом.

На счетный вход счетчика 1 поступают входные импульсы с частотой повторения . При этом происходит периодическое изменение кода, записанного в счетчике 1, с периодом вЂ,где К вЂ” коэффициент пересчета

К ! о счетчика 1, Изменяющийся код Р.; с выходов разрядов счетчика 1 поступает на первые входы блока 2 сравнения, на вторые входы которого поступает код j с выходов фазозадающего блока 3. На выходах блока 2 сравне— ния синхронно в моменты совпадения входных кодов формируются импульсы

1 с частотой повторения = —, сдвио

Иых нутые друг относительно друга на половину периода частоты f . Кроме

В1 1X полезных импульсов на этих выходах будут присутствовать и паразитные импульсы, наличие которых обусловлено влиянием конечных задержек и времени срабатывания реальных элементов устройства, а также их нестабильностью. Для фильтрации паразитных импульсов сигналы с выходов блока 2 сравнения подаются на входы двух тактирующих фильтров с памятью основного 8 и сопряженного 9, на тактовые входы которых поступает сигнал опорной частоты

В качестве тактируемых фильтров о с памятью могут быть использованы синхронные Д -триггеры.

Вследствие того, что длительность паразитных импульсов существенно меньше длительности полезных, на выходах тактируемых фильтроь 8 и 9 с памятью будут формироваться импульсы, соответствующие только полезным составляющим сигналов совпадения с выходов блока сравнения.

Таким образом, на входы триггера

1102026

10 с рa "3дельным управлением будут пос купать последователь ности только полезных импульсов, сдвинутых друг относительно друга на половину периодат и начальной фазой опреде5н>

I ляемой моментом совпадения кодов в блоке 2 сравнения.

Изменение кода на выходе фазоза дающего, блока 3 в соответствии с поступающим на его входы управляющим кодомU „ с выходов буферного блока 10

4 вызывает изменение фазы мендра на выходе триггера 10 с минимальным дискретом

ЛЧ,.„-- 360 /К. 15

При поступлении сигнала "Запрос" синхроимпульсы через элемент И-НЕ

5 поступают на тактовый вход буферного блока 4 и обеспечивают последовательно во времени запись информации в буферный блок 4. К моменту окончания сигнала "Запрос", происходящему по окончании информации, в буферный блок 4 записывается код управления фазой. По окончании сигнала "Запрос" на один из входов схемы И-HE 7 с выхода инвертора 6 поступает разрешающий потенциал.

Сигнал совпадения с выхода тактируемого фильтра с памятью 9 поступает на сигнальный вход 9 -триггера 11 30 в результате чего на выходе послед- . него формируется импульс, сдвинутый относительно основного импульса совпадения на В предлагаемом устройстве сигнал

"Запись", обеспечивающий изменение кода В, отстоит от последнего выходного импульса совпадения по фазе приблизительно на л (или по времени на Л радиан Т/2). H этом

40 случае совпадение момента изменения кода В с моментом формирования сигнала исключается полностью, что существенно повышает надежность работы фазовращателя по сравнению

45 с известным.

Составитель В.Шубин

Редактор Н.Яцола Техред Q.Неце Корректор Г.Решетник

Заказ 4782/43 Тираж 862 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4 Tc*e T/2 + 1/fo и синхронизированный с импульсами опорной частоты f . Сигнал с инверсного выхода D-rðéããåðà 11 через элемент И-НЕ 7 поступает на вход

"Запись" буферного блока 4 и обеспечивает изменение управляющего сигнала на его выходе0 и в соответствии с вновь записанной в буферном блоке

4 информацией, что в свою очередь вызовет соответствующее изменение кода В на выходе фазозадающего блока 3.

Вероятность сбоев в работе предлагаемого устройства в с,":щем случае будет определяться как

1/f 1

Со где — .коэффициент пересчета счетчика 1, что,по краиней мере, вдвое меньше, чем в известном устройстве.

При использовании изобретения в составе следящих сйстем,автоматического регулирования фазы, частоты- и задержки, сигнал на его выходе представляет собой узкополосный процесс, т.е. скорость изменения фазы (задержки ) импульсов намного меньше частоты их следования

1 Зч о

---- с(f

2Л d t, ых

В то же время частота смены кода в фазозадающем блоке 3, исходя из уловия эффективной работы системы автоматического регулирования, должна быть выбрана такой, чтобы о Ч

О dt пр где а уды- интервал смены кода; йЧ вЂ” ширина линейного участка дискриминационной характеристики системы автоматического регулирования.

Как правило all < и во всех случаях йЧ (2й.

Следовательно, при смене фазозадающего кода абсолютная величина изменения фазы импульсов выходного сигнала фазовращателя будет заведомо меньше Ti.

Положительная эффективность предла.аемого технического решения заключается в устранении сбоев, происходящих при изменении кода управления фазовым сдвигом, что обеспечивает. повышение надежности всего устройства.