Матричный коммутатор

Иллюстрации

Показать всеРеферат

МАТРИЧНЫЙ КОММУТАТОР, содержащий М- горизонтальных и М вертикальных коммутируемых шин, в каждой точке пересечения которых расположен 13 -триггер и ключевой транзистор , включенный между соответствующими горизонтальной и вертикальSU ....1102038 3

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

PECnVÜËÈН

ОПИСАНИЕ ИЗОБРЕ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ной шинами, систему М горизонтальных и М вертикальных управляющих шин, причем каждая горизонтальная управляющая шина подключена к.О -входам 3 -триггеров соответствующей строки,,а каждая вертикальная управляющая шина — к С -входам 3 -триггеров соответствующего столбца, о т л и ч а.ю шийся тем, что, с целью повышения производительности коммутатора путем уменьшения времени настройки, между каждым Э -триггером и соответствующим ему ключевым транзисторoM BBеден дополнительный 3— триггер, Q -вход которого соединен с выходом основного 1) -триггера, выход подключен к управляющему электроду ключевого транзистора; а С-входы всех дополнительных 3 -триггеров соединены с шиной разрешения перезаписи информации.

ГОС ДАРСТ ЕНН 1Й KOMHTET CCCP

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И 01НРЫТИИ (21) 3582047/18-21 (22) 21.04.83 (46) 07,.0?.84 Бюл. У 25 (72) P.Ñ.Кильметов, А.Г.Краснопольский, Р.А.Лашевский, Е.Б.Механцев и В.С.Хорик (53) 621.382 (088.8) (56) 1. "Электроника". Пер. с англ.

1975, т. 48, Р 12, с. 48..

2. Макаревич О.Б. и др. ИДП БИС для коммутационных систем телефонии.

"Зарубежная электронная техника", 19/7, Р 15, с. 62 (прототип). (54)(57) МАТРИЧНЫЙ КОММУТАТОР, содержащий N горизонтальных.и М вертикальных коммутируемых шин, в каждой точке пересечения которых рас- . положен 2 -триггер и ключевой транзистор, включенный между соответствующими горизонтальной и вертикаль„SU„,11 2038.

1102038 2

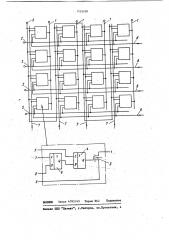

3-триггеров коммутатора соединены;. с шиной разрешения перезаписи информации, На чертеже представлена.функциональная схема предлагаемого коммутатора.

Матричный коммутатор состоит из

IA вертикальных 1, и N горизонтальных

2 коммутируемых шин, в каждом перем крестьи которых помещен ключевой

1о транзистор 3, соединенный с выходом

Q. дополнительного D -триггера 4, вход С которого соединен с шиной 5 перезаписи, вход Я соединен с выходом 62 -триггера б. Вход C3 -триг,гера б соединен с вертикальной управ ляющей шиной 7, вход } соединен с горизонтальной управляющей шиной 8.

Матричный коммутатор работает следующим образом.

Изобретение относится к электронной коммутационной технике, в частности к матричным коммутаторам с запоминанием сигналов управления, и может быть использовано в автоматике и вычислительной технике.

Известен коммутатор, состоящий из матрицы аналоговых ключей на ЩЦП транзисторах, управляемых устройство хранения программы настройки 1 1J, Недостатком этого коммутатора является невозможность передачи информации во время настройки.

Наиболее близким к предложенному является матричный коммутатор, содержащий М горизонтальных и М вертикальных коммутируемых шин,.в каждой точке пересечения которых расположен2 -триггер и ключевой транзистор, включенный между соответствующими горизонтальной и вертикальной шинами, систему 11 горизонтальных и вертикальных управляющих шин, причем каждая горизонтальная управляющая шина подключена к 3 -входам

Я-триггеров соответствующей строки, а каждая вертикальная управляющая шина — к С-входам 3 -триггеров соответствующего столбца (2 1.

Недостатком известного коммутаторазО является низкая производительность устройства в связи с многотактным ложным состоянием во время настройки.

Цель изобретения — повышение производительности коммутатора путем 35 уменьшения времени настройки.

Цель достигается тем, что в матричный коммутатор, содержащий 8 горизонтальных и М вертикальнь}х коммутируемых шин, в каждой точке пересечения 40 которых расположен D -триггер и ключевой транзистор, включенный между соответствующими горизонтальной и вертикальной шинами, систему } 1 горизонтальных и М вертикальных управ-45 ляющих шин, причем каждая горизонтальная управляющая шина подключена к D -входам D -триггеров соответствую- щей строки, а каждая вертикальная управляющая шина — к С-входам Э -триггеров соответствуюшего. столбца, между каждым f} -триггером и соответствующим ему ключевым транзистором введен дополнительный D -триггер, 3 -вход которого подключен к выходу основного

D-триггера, выход подключен к управляющему электроду .ключевого -транзистора,a С -входы всех дополнительных

В режиме установления соединений последовательно выбираются управляю— ,щие шины 7, одновременно выбирается одна из шин 8. При этом в 3 -триггер 6, связанный с выбранной вертикальной управляющей шиной 7, записываются коды, поступившие на соответствующие горизонтальные управляющие шины 8. После М тактов, когда во все столбцы матрицы записана информация о настройке, на шину 5 поступает сигнал разрешения перезаписи. По этому сигналу информация из 3 -триггера б переписывается в дополнительный D -триггер 4 за время, равное одному такту. Ключевые транзисторы 3 коммутатора принимают состояния, соответствующие ксду настройки, и коммутатор готов к передаче информации.

Во время записи новой программы настройки в 3 -триггеры б матричного коммутатора, дополнительные 3 -триггеры 4 хранят старую программу настройки и управляют ключевыми транзисторами 3 матрицы. Поэтому во время записи новой программы соединений коммутатор может передавать коммутируемые сигналы по старым сое% динениям. Переход на новую программу соединений осуществляется за один такт.

Технический эффект от использования предложенного матричного комму— татора заключается в повышении протГ изводительности путем уменьшения времени настройки при выполнении его в виде большой интегральной микросхе\ мы ° аццИПИ Заказ 4782/43 Тираж 862 Подписное

Филиал ППП "Пвтвит" г Ужгород уп Проектная ° 4