Псевдолинейное корректирующее устройство

Иллюстрации

Показать всеРеферат

ПСЕВДОЛИНЕЙНОЕ КОРРЕКТИРУЮЩЕЕ УСТРОЙСТВО, содержащее интегратор, вход которого соединен с входом устройства и с первым входом сумматора , а выход - с вторым входом сумматора , отличающееся тем, что, с целью упрощения устройства, в нем установлены последовательно соединенные запоминающий элемент и масщтабный блок и последовательно соединенные дифференцирующее звено и нуль-орган, выход которого подключен к управляющему входу запоминающего элемента , входы дифференцирующего звена и запоминающего элемента соединены с входом устройства, а выход масштабного блока подключен к третьему входу суммато-ра , выход которого является выходом устройства . 00 Х

,„SU„„1103197

СОЮЗ СОВКТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК з(д) б 05 В 5/Ol

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3492780/18-24 (22) 17.09.82 (46) 15.07.84. Бюл. № 26 (72) А. Б. Градусов; А. А. Галкин и Ю. А. Медведев. (71) Владимирский политехнический институт (53) 62-50 (088.8) (56) 1. Бесенерский В. А., Попов Е; П.

Теория систем автоматического регулирования. М., «Наука», 1975, с. 109 — 113.

2. Авторское свидетельство СССР № 640248, кл. G 05 В 5/01, 1876 (прототип) . (54) (57) ПСЕВДОЛИНЕЙНОЕ КОРРЕКТИРУЮЩЕЕ УСТРОЙСТВО, содержащее интегратор, вход которого соединен с входом устройства и с первым входом сумматора, а выход — с вторым входом сумматора, отличающееся тем, что, с целью упрощения устройства, в нем установлены последовательно соединенные запоминающий элемент и масштабный блок и последовательно соединенные дифференцирую щее звено и нуль-орган, выход которого подключен к управляющему входу запоминающего элемента, входы дифференци рующего звена и запоминающего элемента соединены с входом устройства, а выход масштабного блока подключен к третьему входу сумматора, выход которого является выходом устройства.

1103197

40

Изобретение относится к элементам систем автоматического управления и может быть использовано для улучшения качества систем путем введения астатизма.

Известно линейное корректирующее устройство, содержащее интегратор, сумматор и динамические звенья (1).

Основной недостаток этого устройства— взаимнооднозначная связь между амплитудой и фазовой характеристиками, ограничивающая его корректирующие свойства.

Наиболее близким к предлагаемому является псевдолинейное корректирующее устройство, содер жащее логически и блок управления, состоящий из двух линейных динамических звеньев, четырех. релейных блоков и трех блоков умножения, а также интегратора, вход которого соединен с входом устройства и с первым входом сумматора, а выход — с вторым входом сумматора (2).

Недостатком известного устройства является сложность его технической реализации из-за наличия в схеме трех блоков умножения и четырех релейных блоков. Кроме того, оно теряет псевдолинейные свойства при появлении на входе устройства постоянной соста вляющей.

Цель изобретения — упрощение устройства и сохранение корректирующих свойств при наличии постоянной составляющей на входе устройства.

Поставленная цель достигается тем, что в устройство, содержащее интегратор, вход которого соединен с входом устройства и с первым входом сумматора, а выход — с вторым входом сумматора, введены последовательно соединенные запоминающий элемент и масштабный блок и последовательно соединенные дифференцирующее звено и нуль-орган, выход которого подключен к управляющему входу запоминающего элемента, входы дифференцирующего звена и запоминающего элемента соединены с входом устройства, а выход масштабного блока подключен к третьему входу сумматора, выход которого является выходом устройства.

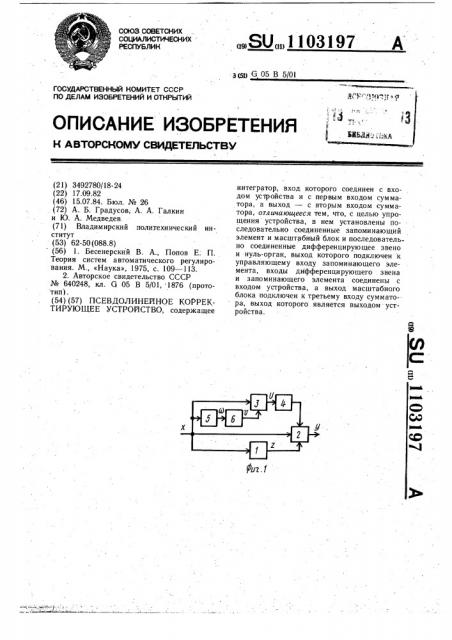

На фиг. 1 представлена структурная схема предлагаемого псевдолинейного корректирующего устройства; на фиг. 2 — формы сигналов, поясняющие работу устройства.

На фиг. 1 и 2 приняты следующие обозначения: входной сигнал х устройства; выходной сигнал у устройства; выходной сигнал z интегратора; выходной сигнал 4 дифференцирующего звена; выходной сигнал U нуль-органа; выходной сигнал и запоминающего элемента; смещение х; постоянная составляющая ио сигнала ц.

Устройство включает интегратор 1, вход и выход которого соединены соответственно с первым и вторым входом сумматора 2, 5

55 к третьему входу которого через масштабный блок 4 подключен выход запоминающего элемента 3. Вход последнего непосредственно соединен с входом устройства, а также с входами интегратора 1 и дифференцирующего звена 5, выход которого через нуль-орган 6 подключен к управляющему входу запоминающего элемента 3. Выходом устройства является выход сумматора 2.

Устройство работает следующим образом.

Входной сигнал Х (t) поступает на первый вход сумматора 2, а также на входы интегратора 1, запоминающего элемента 3 и дифференцирующего звена 5. Сигнал W,(t) с выхода дифферен цирующего звена 5 поступает на вход нуль-органа 6, выходной сигнал которого v,(t) представляет последовательность импульсов, возникающих в моменты t;,равенства нулю сигнала K(t).

Эти импульсы поступают на управляющий вход запоминающего элемента 3, который фиксирует входной сигнал х (1) в моменты

t îõðàíÿÿ постоянным зафиксированное значение амплитуды сигнала на промежутке времени (t;, 11,,),, В результате сигнал

x (t) преобразуется запоминающим элементом 3 в кусочно-постоянный сигнал %(t), который через масштабный блок 4 с инвертированием подается на третий вход сумматора 2, на второй вход которого поступает сигнал z (t) с выхода интегратора 1. На отрезке времени между двумя запоминаюшими (11, ti,) для сигнала на выходе устройства (t) можно записать

Y(t) =x(t) +K3X(t) +Kou(t), (1) где z (t) = z (t;),.+ i (t) dt;

4 ПОСтояиное на отРезке

U(t)"- X(ts) — времени (t;, t; ) зафиксированное значение сигнала x(t;);

-моменты запоминания;

14 кг — постоянные коэффициенты.

Проводя гармоническую линеаризацию выражения (1) для передаточной функции дифференцирующего звена 5, вида

N(S) =к — — —, (2) что соответствует реальйому дифференциатору, получают следующее значение эквивалентной передаточной функции устройства

Ц = Aebp, (3)

Где А= (1+ 4 бай т и Я 1 ку

". ° -*т* к т+ш*т ш1* к ц = агс Ц мт

<+ к4. -т,— тгКак видно из соотношений (3), эквивалентные амплитуды и фазовая характеристики устройства не зависят от амплитуды входного сигнала х (t) и, следовательно, оно является псевдолинейным.

По явлен ие на входе корректирую щего устройства сигнала смещения х приводит

1103197

Составитель Г. Вышковский

Редактор С. Лисина Техред И. Верес Корректор И. Муска

Заказ 4978/35 Тираж 842 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и от крытий

I 13035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 лишь к смещению выходного сигнала и (t) запоминающего элемента 3 на величину хо без изменения формы этого сигнала м..(t). Так как выходной сигнал Ю .(t) дифференцирующего звена не содержит постоянной составляющей, то изменения -моментов запоминания t .,,äî сравнению с симметричным режимом не происходит. Таким образом, запоминающий элемент 3, а следовательно, и все устройство в целом осуществляет линейное преобразование постоянной составляющей входного сигнала x.(t) и псевдолинейное преобразование переменной составляющей.

В резульгате предлагаемое псевдолинейное корректирующее устройство позволяет получать системы, показатели качества которых не изменяются при возникновении в сигнале ошибки смещения х.