Устройство управления с контролем переходов

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО УПРАВЛЕНИЯ С КОНТРОЛЕМ ПЕРЕХОДОВ, содержащее регистр управления переходами, регистр адреса, блок памяти микрокоманд, регистр микрокоманд и первый блок ассоциативной памяти, причем входы регистра управления переходами соединены с входами устройства, а выходы - с входами старших разрядов регистра адреса, выходы которого соединены с адресными входами блока памяти микрокоманд, выходы которого соединены с входами регистра микрокоманд , выходы младших разрядов которого соединены с входами младших разрядов регистра адреса, о т л и ч а ющ е е с я тем, что, с целью расширения функциональных возможностей путем увеличения глубины тестирования в него введены регистр хранения адресов команд перехода, даиифратор кода операции, два блока сравнения, два буферных регистра, втоцой блок . ассоциативной памяти, два элемента задержки, формирователь адреса и два регистра индикации, причем выходы старших разрядов регистра микрокоманд соединены с входами деишфратора кода операции, выход которого соединен с входами синхронизации первого и второго буферпых регистров и регистра хранения адреса команд переходов и че1/ез первый элемент задержки подключен к входам разрешения записи первого и второго буферных регистров , а через второй элемент задержки соединен с входами разрешения чтения первого и второго блоков ассоциативной памяти, выходы регистра соединены с информационными входами - регистра хранения адресов команд переходов, выходы которого соединены с первыми группами входов первого и второго блоков сравнения, выход первого блока сравнения соединен с входом первого регистра индикации и с первым входом формирователя адреса, выход второго блока сравнения соединен с входом второго регистра индикации и с вторым входом формирователя адреса, выходы которого соединены с адресными входами первого и второго § блоков ассоциативной памяти, выходы (Л первого блока ассоциативной памяти соединены с информационными входами первого буферного регистра., выходы которого соединены с второй группой входов первого блока сравнения, выходы второго блока ассоциативной памяти соединены с информационными входами второго буферного регистра, выходы которого соединены с второй группой входов второго блока сравнения. 2. Устройство по п. 1, о т л и чающееся тем, что формирователь адреса содержит генератор импульсов , одновибратор, два счетчика адреса, две группы элементов И и 00 группу элементов ИЛИ, причем первый вход формирователя соединен с первыми , входами элементов И первой группы и входом генератора импульсов , выход которого соединен со счетным входом -.первого счетчика адреса , выходы которого соединены с вторыми входами элементов И первой группы, выходы которых соединены с первыми входами элементов ИЛИ группы, ,выходы которых соединены с выходами .Формирователя, второй вход формирователя соединен с первыми входами элементов И второй группы и входом

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) g(5D G 06 F 11 00

ОПИСАНИЕ ИЗОБРЕТ

Н ABTOPCKOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

:(21) 3553833/18-24 (22) 15.02.8.3 (46) 15.07.84. Бюл. )). 26 (72) Г.И.Макаренко, A.Ô.Kèðüÿêoâ, А.В.Королев и Н.Г.Топольский (53) 681. 32 (088. 8) (56) 1. Авторское свидетельство СССР

Р 711573, кл. G 06 F 11/00, 1978.

2. Авторское свидетельство СССР

9 807289, кл. G 06 F 11/00, 1978 (прототип) . (54) (57) 1. УСТРОЙСТВО УПРАВЛЕНИЯ С

КОНТРОЛЕМ ПЕРЕХОДОВ, содержащее регистр управления переходами, регистр адреса, блок памяти микрокоманд, регистр микрокоманд и первый блок ассоциативной памяти, причем входы регистра управления переходами соединены с входами устройства, а выходы — с входами старших разрядов регистра адреса, выходы которого соединены с адресными входами блока памяти микрокоманд, выходы которого соединены с входами регистра микрокоманд, выходы младших разрядов которого соединены с входами младших разрядов регистра адреса, о т л и ч а ющ е е с я тем, что, .с целью расширения функциональных возможностей путем увеличения глубины тестирования в него введены регистр хранения адресов команд перехода, дешифратор кода операции, два блока сравнения, два буферных регистра, второй блок ассоциативной памяти, два элемента задержки, формирователь адреса и два регистра индикации, причем выходы старших разрядов регистра микрокоманд соединены с входами деиифратора кода операции, выход которого соединен с входами синхронизации первого и второго буферных регистров и регистра хранения адреса команд переходов и че. ез первый элемент задержки подключен к входам разрешения записи первого и второго буферных регистров, а через второй элемент задер жки соединен с входами разрешения чтения первого и второго блоков ассоциативной памяти, выходы регистра соединены с информационными входами регистра хранения адресов команд переходов, выходы которого соединены с первыми группами входов первого и второго блоков сравнения, выход первого блока сравнения соединен с входом первого регистра индикации и с первым входом формирователя адреса, выход второго блока сравнения соединен с входом второго регистра индикации и с вторым входом формирователя адреса, выходы которого соединены с адресными входами первого и второго блоков ассоциативной памяти, выходы первого блока ассоциативной памяти соединены с информационными входами первого буферного регистра., выходы которого соединены с второй группой входов первого блока сравнения, выходы второго блока ассоциативной памяти соединены с информационными входами второго буферного регистра, выходы которого соединены с второй группой входов второго блока сравнения.

2. ) стройство по и. 1, о т л и ч а ю щ е е с я тем, что формирователь адреса содержит генератор импульсов, одновибратор, два счетчика адреса, две группы элементов И и группу элементов ИЛИ, причем первый вход формирователя соединен с первыми. входами элементов И первой группы и входом генератора импульсов, выход которого соединен со счетным входом .первого счетчика адреса, выходы которого соединены с вторыми входами элементов И первой группы, выходы которых соединены с первыми входами элементов ИЛИ группы, выходы которых соединены с выходами формирователя, второй вход формирователя соединен с первыми входами элементов И второй группы и входом

11032 38 рыми входами элементов И Второй группы ю ВыхОды кОтОрых соединены вторыми входами элементов ИЛИ группы. одн о ви бр ат ора, выход которого соеди— нен со счетным входом счетчика адреса, выходы которого соединены с вто1 2

Изобретение относится к цифровой Целью изобретения является увеливычислительной технике и может быть чение глубины тестирования програмиспользовано при отладке в динамике много обеспечения цВМ, путем аналипрограммного обеспечения цифровых вы- за ветвей на дереве программы, числительных машин (ЦВМ) „ 5

Известно устройство, в котором

Поставленная цель достигается тем, KoHTpoJIb хОда прОграммы IlpH естест— венной последовательности операций, управления перехо ами реса, блок памяти микрокоман а также при условных и безусловных ро оманд, регистр микрокоманд и первый блок ас-. переходах основан на использовании из-.1 быточности информации в кодах команд, 10социативной памяти, причем вхо ы егистра. управления переходами сое а также использовании контрольных меР ре одами соединены с входами устройства а выхо ток, т. е. специальных команд, расположенных на ветвях программ t 1 j. с входами старших разрядов егист а адреса, выходы которого соединены

Недостатками таких устройств явля- 15 с адресными входами блока памяти микется большой объем оборудования (в рокоманд, выходы которого соединены частности, запоминающих устройств) с входами регистра микрокоманд выили же увеличение времени счета.

Р Р р оманд, выходы младших разрядов которого соеНаиболее близким по техническому динены с входами младших разрядов решению к предлагаемому является мик-, Ä perzczpa адреса, введены регистр храропрограммное устройство управления, нения адресов команд перехода, деши.— содержащее регистр адреса, блок памя- фратор кода операции, два блока сравРегистР начала Участка, блск Управле- блок а нения, два бу ерных регистра, второй лок ассоциативной памяти, два эления переходами, два регистра сдвига з адержки формирователь адре и блок ассоциативной памяти, причем са и два регистра индикации, причем выходы регистра адреса соединены с выходы старших разрядов регистра па-. входами блока памяти микрокоманд, вымикрокоманд соединены с входами деходы котОрого соединены с входами шифратора кода опера ши ратора кода операции, выход которегистра микрокоманд, выходы котоРо- рого соединен с входами си хр н рого соединен с входами синхронизаго соед иены с первыми гРУппами вхо- 30 ции первого и второго буФерных регидов регистра адреса и первого регист стров и регистра хранения адресов кора сдвига., а также с входами регис р манд перехода и через первый элемент начала участка, выходы котоРого соеди задержки подключен к входам разрешенены с первой группой входов блока ния записи первого и второго буферассоциативной памяти, вторая и треть 35 ных регистров а через второй э ем нт группы входов которого подключены сс — задержки соединен с входами разрешеответственно к выходам первого и вто- ния чтения первого и второго блоков рого регистров сдвига, а выходы соеди- ассоциативной памяти, выходы регистнены с вторыми входами регистРов сдви ра а)1реса соединены с информационныга, выходы блока управления перехода 40 ми входами регистра хранения адресов ии подключены к входам регистРа ре команд переходов, выходы которого .соеса и второго регистра сдвига (2 ). динены с первыми группами входов первого и второго блоков сравнения, выНедостатки данного устройства за- .ход первого блока сравнения соединен ключаются в том, что в программу вие.45 с входом первого регистра индикации дены дополнительные метки, что тре и с первым входом формирователя адребует увеличение памяти кроме того са, выход второго блока сравнения соеэто устройство при ложных переходах динен с входом второго регистре индивозвратных, пропусках одной или нес- кации и с вторым входом формироватекольких микрокоманд, ложных выпол- 50 ля адреса, выхбды которого соединены нениях микрокоманд условного пере- с адресными входами первого и второго хода не позволяет обнаруживать место блоков ассоциативной памяти, выходы ошибки в ходе выполнения программы, первого блока ассоциативной памяти т.е. обеспечивает контроль всего соединены с информационными .входами тракта и не обеспечивает контроль первого буферного регистра, выходы элементов, входящих в тракт. которого соединены с второй группой

1103238 счетчика 21 через элементы И 19 и

ИЛИ 17 поступает на выход формирователя.

Таким образом, в зависимости от состояний входов формирователя адреса 24 и 25 на его выходе будет присутствовать адрес с выхода счетчика

20 или 21.

Лва элемента 16 задержки обеспечивают формирование на выходе стробов записи и чтения для соответствующих элементов устройства.

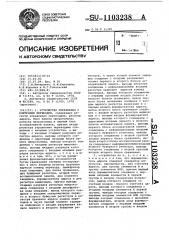

Устройство работает следующим образом.

В ходе исполнения программы нз блока 1 памяти микрокоманд ЦВМ по адресу, формируемому в регистре 2 адреса, выбираются микрокоманды, которые заносятся в регистр 3 микрокоманд. При этом адрес микрокоманд каждый раз запоминается в регистре адреса микрокоманд переходов. Как только на вход дешифратора 6 кода операций с выхода регистра 3 микрокоманд поступает код операции одной из микрокоманд переходов, .адрес этой микрокоманды перехода считыва ется из регистра адреса и поступает на входы двух блоков 7 и 8 сравнения.

На другие входы их по .сигналу чтения, поступающуму с выхода дешифратора 6 микрокоманд, поступают значения адресов микрокоманд переходов, предварительно записанные в блоках 11 и 12 ассоциативной памяти, В результате сравнения значения те-. кущего адреса микрокоманды перехода с адресами, выбранными из блоков ассоциативной памяти,на выходе блоков

7 и 8 формируются сигналы 0, 1 или 1, 0, т.е. определяется одно из двух возможных направлений ветвления программы. С выхода блоков 7 и 8 информация о направлении ветвления программы поступает на входы регистров 13 и 14 индикации, а также на вход формирователя

15 адреса, где по этой информации формируется адрес следующих двух значений адресов микрокоманд переходов.

Эти .значения по адресу, поступающему с выхода формирователя адреса, и по сигналу чтения из ассоциативной памяти записываются в буферные регистры 9 и 10. На входы блоков 7 и 8 информация с выходов буферных регистров 9 и 10 поступает в момент прихода следующей микрокоманды перехода, т.е. каждый раз после прихода очередной микрокоманды перехода на дереве программы (фиг. 3) идентифицируется уход или на правую 25, или на левую 24 ветвь программы, что отражается на регистрах 13 и 14 индикации.

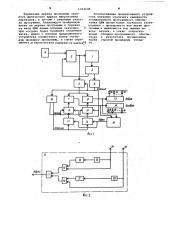

На фиг. 4 показаны значения регистров индикации, соответствующие отработанной ветви, показанной на дереве программы фиг.3 пунктирной линией, входов первого блока сравнения, выходы второго блока ассоциативной памяти соединены с информационными .входами второго буферного регистра, выходы которого соединены с второй группой входов второго блока сравне- 5 ния..

Формирователь адреса содержит генератор импульсов, одновибратор, два счетчика адреса, две группы элементов И и группу элементов ИЛИ, причем первый вход формирователя сое. динен с первыми входами элементов

И первой группы и входом генератора импульсов, выход которого соединен со счетным входом первого счетчика 15 адреса, выходы которого соединены с вторыми входами элементов И первой группы, выходы которых соединены с первыми входами элементов ИЛИ группы, выходы которых соединены с

- выходами формирователя, второй вход формирователя соединен с первыми входами элементов И второй группы и входом одновибратора, выход которого соединен со счетным входом счет- 2 чика адреса, выходы которого соединены с вторыми входами элементов И второй группы, выходы которых соединены с вторыми входами элементов ИЛИ группы.

На фиг. 1 представлена блок-схема устройства; на фиг. 2 — структура формирователя адреса; на фиг. 3 пример дерева программы; на фиг. 4 состояния регистров индикации для пути, показанного на дереве программы.

Устройство содержит блок 1 памяти микрокоманд, регистр 2 адреса, регистр 3 микрокоманды, блок 4 управления переходами, регистр 5 хранения адресов команд переходов, дешифратор 40

6 кода операций, блоки 7 и 8 сравнения, буферные регистры 9 и 10, блоки

11 и 12 ассоциативной памяти, регистры 13 и 14 индикации, формирователь

15 адреса, группу 16 элементов з адерж-45 ки.

Формирователь 15 адреса (фиг. 3) содержит группу 17 элементов ИЛИ, две группы 18 и 19 элементов И, счетчики 20 и 21 адреса, одновибратор 22, генератор 23 импульсов, входы 24 и

25 формирователя адреса.

Формирователь работает следующим образом.

При поступлении сигнала на вход формирователя адреса запускается генератор 22 одиночных импульсов, после чего состояние счетчика 20 адреса увеличивается на 1 . Адрес с выхода счетчика 20 через элементы

И 18 и ИЛИ 17 поступает на выход. При 60 поступлении сигнала на вход формирователя адреса запускается генератор 23 импульсов, кратных двум, после чего происходит наращивание состояния счетчика 21. Адрес с выхода 65

l 103238

Вершинами дерева программы являются физические адреса микрокоманд переходов, а дугами — линейные участки программы. Анализируя пройденную ветвь на дереве програмваа и подавая на вход ЦВМ новые входные значения, 5 при которых будет пройдена следующая ветвь, можно с помощью предложенного устройства осуществить болев глубокую проверку программы, а также опре делить,в каких ветвях содержатся ошибки1О

Использование предлагаемого устройства позволит увеличить надежность отлаживаемого программного обеспечения.ЦВМ путем более глубокого тестирования — проверяются все ветви програмьм и выявляются все ошибки во всех ветвях, а также сократить время отладки программного обеспечения в результате организации более строгой процедуры отладки.

1103238

Фиг.,1

Составитель A,×åêàíoâ

Редактор Л.Веселовская Техред Т.Дубинчак Корректор A.Òÿñêo

Заказ 50 30/38 Тираж 699 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д. 4/5

Филиал ППП Патент, г. Ужгород, ул, Проектная р 4