Цифровой фазометр

Иллюстрации

Показать всеРеферат

ЦИФРОВОЙ ФАЗОМЕТР, содержащий первый умножитель частоты, последовательно соединенные входной блок, первый блок управления и первый счетчик , при этом вход входного блока через первый умножитель частоты соединен с первым блоком управления, о тличающийся тем, что, с целью повышения точности, в него введены последовательно соединенные первый элемент задержки, второй счетчик и регистр, а также последовательно соединенные второй умножитель частоты, второй блок управления, RS-триггер и ключ, вход которого соединен с выходом первого блока управления, а выход - с входом второго элемента задержки , выход которого подключен к соответствующим входам первого счетчика и RS-триггера, причем выход входного блока соединен с входами вто рого блока управления, первого элемента задержки и регистра, выход которого соединен с управляющим входом второго умножителя частоты, информационный вход которого соединен с входом первого-умножителя частоты, кро-.S ме того, вход второго счетчика сое (Л динен с выходом первого умножителя частоты, при этом первый счетчик выполнен реверсивным. Uf и 2 4 1 С СО

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

3(59 1 25 08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3529085/18-21 (22) 28. 12.82 (46) 2 3. 07. 84. Бюл. Р 27 (72) Ю.М .Вешкурцев, Б.Г.Бронштейн и В.A .Мироненко (71) Омский политехнический институт (53) 621. 317. 772 (088,8) (56) 1. Авторское свидетельство СССР

9 486284, кл, G 01 R 25/00, 1975.

2. Авторское свидетельство СССР

Р 387302,. кл, G 01 R 25/2, 1973. (54) (57) ЦИФРОВОЙ ФАЗОМЕТР, содержащий первый умножитель частоты, последовательно соединенные входной блок, первый блок управления и первый счетчик, при этом вход входного блока через первый умножитель частоты соединен с первым блоком управления, о тл-и ч а ю шийся тем, что, с целью повышения точности, в него введены последовательно соединенные первый

„„SU„„9 A элемент задержки, второй счетчик и регистр, а также последовательно соединенные второй умножитель частоты, второй блок управления, RS-триггер и ключ, вход которого соединен с выходом первого блока управления, а выход — с входом второго элемента задержки, выход которого подключен к соответствующим входам первого счетчика и RS-триггера, причем выход входного блока соединен с входами второго блока управления, первого элемента задержки и регистра, выход которого соединен с управляющим входом второго умножителя частоты, информационный вход которого соединен с входом первого- умножителя частоты, кро- Е

И ме того, вход второго счетчика соединен с выходом первого умножителя частоты, ггри этом первый счетчик выполнен реверсивным.

1104439

Изобретение относится к измерительной технике и- может быть использ овано для и змерени я мгновенных фазовых сдвигов электрических колебаний в диапазоне низких и инфранизких частот .

Известен цифровой фазометр, содержащИй формирователи импульсов, элект— ронный ключ, счетчик импульсов и умножитель частоты (1 .

Недостатком фазометра является 10 наличие погрешности измерения сдвига фаз за счет нелинейности выходной характеристики умножителя частоты, вызванной погрешностью дискретности, присущей всем цифровым устройствам, 15 максимальное значение которой ограничено достижижам быстродействием современной элементной базы.

Наиболее близким к изобретению по технической сущности является устройство для измерения фазового сдви-. га между двумя переменными напряжениями, содержащее входной блок, блок управления с двумя входами, включенный между выходом умножителя частоты . и входом счетчика, выход входного бло ка подключен к второму входу управляющего блока, а первый вход объединен с входом умножителя частоты и является входом фазометра, другим входом которого является второй вход нходно- З0 го блока f2 3.

Недостатком известного устройства является наличие погрешности измерения, пропорциональной нелинейности характ ери стики умножителя, используемого в фазометре.

Цель изобретения — повышение точности измерения.

Поставленная цель достигается тем, что в цифровой фазометр, содержащий 40 первый умножитель частоты, последовательно соединенные входной блок, первый блок управления и первый счетчик, при этом вход .входного блока через первый умножитель частоты сое- 45 динен с первМм блоком управления, введены последовательно соединенные первый элемент задержки, второй счетг чик и регистр, а также последователь" но соединенные второй умножитель 50 частоты, второй блок управления, RSтриггер и ключ, вход которого соединен с выходом первого блока управления, а выход — с входом второго элемента задержки, выход которого подключен к соответствующим входам первого счетчика и RS — òðèããåðà, причем выход входного блока соединен с входами второго блока управления, первого элемента задержки и регистра, выход которого соединен с управляющим входом второго умножителя частоты, информационный вход которого соединен с входом первого умножителя частоты, кроме того, вход второго счетчика соединен с выходом первого умно- 65 жителя частоты, при этом первый счетчик выполнен реверсивным.

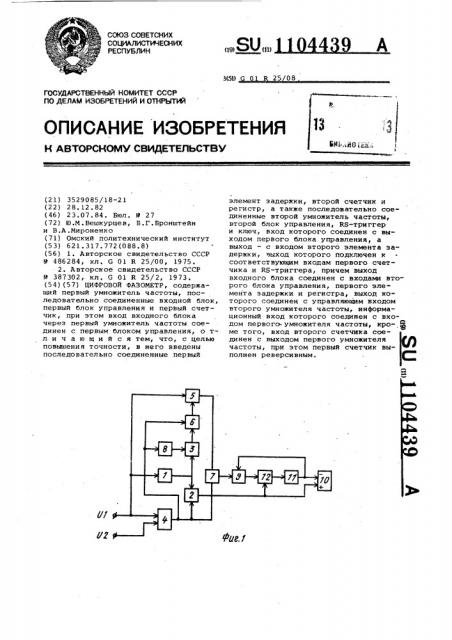

На фиг. 1 приведена структурная схема фазометра на фиг, 2 — временные диаграммы, поясняющие его работу.

Фазометр содержит первый умножитель 1 частоты, первый управляющий блок 2, нторой счетчик 3 импульсов, входной блок 4, второй умножитель

5 частоты, регистр 6 памяти, второй управляющий блок 7, первый элемент

8 задержки, RS-триггер 9, первый счетчик 10 импульсов, второй элемент

11 задержки, ключ 12, Выход первого умножителя 1 частоты подключен к первому входу первого управляющего блока 2 и к входу второго счетчика 3 импульсов. Второй вход первого управляющего блока 2 присоединен к выходу входного блока 4, первый вход которого объединен с входом первого умножителя 1 частоты и с входом второго умножителя 5 частоты

Выход второго счетчика 3 импульсов подключен к информационному входу регистра 6 памяти, выход которого присоединен к управляющему входу второго умножителя 5 частоты, выходом подключенного к первому входу второго управляющего блока 7, второй вход которого объединен с вторым входом пер вого управляющего блока 2, а также с управляющим входом регистра 6 памяти и входом первого элемента 8 задержки, выход которого присоединен к входу установки нуля второго счетчика 3 импульсов, Выход второго управляющего блока 7 подключен к S-входу триггера

9, R-вход которого объединен с нычитающим входом первого счетчика 10 импульсов и соединен с ныходом второго элемента 11 задержки, нход которого присоединен к выходу электронного ключа 12. Один из входов элект-. ронного ключа 12 подключен к выходу триггера 9, а другой объединен с сусуммирующим входом первого счетчика

10 импульсов и подключен к выходу первого управляющего блока 2. Входы входного блока 4 являются входами фазометра. Первый счетчик 10 импульсоВ.âûïoëíåH реверсивным.

Фазометр работает следующим образом.

В исходном положении управляющий блок 2, второй управляющий блок 7 и электронный ключ 12 закрыты. Первый счетчик 10 импульсов, второй счетчик

3 импульсов, а также RS-триггер находятся в нулевом состоянии. В регистр 6 памяти записано число, равное нулю. Коэффициент умножения второго умножителя 5 частоты равен нулю, а коэффициент умножения первого умножителя 1 частоты равен К .

Исследуемые напряжения б1 и U2 (фиг, 2а) поступают на входы фазометра. При этом на выходе входного

1104439 блока 4 появляются импульсы (фиг. 2б) с периодом следования Т и длительностью

360 где Т вЂ” период колебаний исследуемых напряжений;

Ч - измеряеьый сдвиг фаз между входными сигналами, Эти импульсы поступают на второй вход первого управляющего блока 2, который открывается и в течение интервала времени обеспечивает прохождение на суммирующий вход первого счетчика 10 с выхода первого умножителя 1 частоты импульсов (фиг.2г) с периодом следования Т/14, где Кф =

K„+ «11Кн K„(1 + коэффициент умножения первого умножителя 1 частоты; К„ - номинальное значение коэффициента умножения первого умножителя 1 частоты; — относительная нелинейность выходной характеристики первого умножителя 1 частоты, которая является функцией от частоты входного сигнала.

Пока первый управляющий блок 2 открыт, на суммирующий вход первого счетчика 10 поступает количество импульсов

1 „(1+yj.

K cb

За указанный период Т на вход второго счетчика 3 импульсов с выхода первого умножителя 1 частоты постуN = К„(1 + y„) импульсов, Так как емкосТь второго счетчика 3 выбрана равной Кк, то к концу периода Т следования импульсов во второй счетчик 3 запишется N = К„(1 + 1 )

K „= у K èìïóëüñîâ. По переднему фронту импульса с выхода входного блока 4 регистр 6 памяти запоминает код второго счетчика 3 импульсов, численное значение которого равно

N = 1„К„, и подает этот код на управляющий вход второго умножителя 5 частоты. Кроме того, после задержки во времени элементом 8 импульса (фиг.

2б и в) с выхода блока 4 по переднему фронту задержанного импульса (фиг. 2в) установится в исходное состояние второй счетчик 3. Длительность задержки Ы элемента 8 должна быть достаточной (например, сотни наносекунд), чтобы обеспечить надежную запись информации в регистр 6 памяти до того, как по переднему фронту импульса с выхода элемента 8 второй счетчик 3 перейдет в исходное состояние.

После этого коэффициент умножения второго умножителя 5 частоты станет равным, К „(1 + i „), где 1 — нелинейность выходной характеристики второго умножителя 5 частоты. Частота сигнала на выходе второго умножитепя 5 частоты установится в )) К„(1+ф1) раз большей, чем на его входе, т.е, она будет равна

Т "" + ).

1о

Второй управляющий блок 7 т ах же, как и первый управляющий блок 2, открыт в течение интервала времени Г; за который с выхода второго умножите-.

)5 ля 5 частоты на вычитающий вход первого счетчика 10 через цепочку, состоящую из триггера 9, электронного ключа 12 и второго элемента 11 задержки, поступит количество импульсов (фиг. 2д) го

4 0 н("2) 65 от значения относительной нелинейЦепочка, состоящая из триггера 9, ключа 12 и элемента 11 задержки, предназначена для исключения моментов совпадений импульсов, поступаю- щих на суммирующий и вычитающий входы первого счетчика 10 импульсов.

Работает цепочка следующим образом.

Импульсом с выхода блока 7 триггер 9 устанавливается в единичное состояние (фиг, 2а), что обеспечивает открывание электронного ключа. Им35 пульс, поступающий на суммирующий вход первого счетчика 10, через открытый электронный ключ 12 и элемент

11 задержки подается на вычитающий вход счетчика 10(фиг. 2ж), Импульсом

4О с выхода элемента 11 задержки триггер 9 возвращается в исходное состояние и закрывает электронный ключ 12 до прихода очередного импульса в второго управляющего блока 7, Длитель45 ность временной задержки элемента 11 должна быть не менее А (фиг. 2ж) для того, чтобы обеспечить надежную работу счетчика 10, т.е. чтобы на суммирующий и вычитающий входы счетчика

10 поступали импульсы в разные моменты времени. Так как частота следствия импульсов с выхода второго управляющего блока 7 всегда меньше частоты сигнала с выхода первого управляющего блока 2, то потеря импульсов цепочкой, состоящей из триггера

9, электронного ключа 12 и элемента

11 задержки, происходить не будет.

Таким образом, к началу следующего интервала времени в счетчике 10 импульсов окажется записанной разность

1 — N4 = 3600 K„(1 — 1112).Эа разность прямо пропорциональна измеряемому сдвигу фаз Y и зависит не

11044 39

Составитель C,Ìîðîçîâ

Редактор О.Юрковецкая Техред Л.Мартящова Корректор С.Черни

Заказ 5205/32 Тираж 7 11 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 ности выходной характеристики первого умножителя 1 частоты 1„, а от произведения относительных нелинейностей выходных характеристик первого умножителя 1 частоты и второго умножителя 5 частоты 1 . Причем 1 ((«1„), так как всегда справедливо условие, („ 1, ) (: 1, Следовательно, включение в схему второго умножителя частоты позволяет уменьшить погрешность от нелинейности выходной характеристики умножителя частоты и эа счет этого

5 повысить точность измерения сдвига Фаз на низких и инфранизких частотах.