Устройство для определения ранга числа

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ РАНГА ЧИСЛА, содержащее k регистров, k блоков памяти, причем входы регистров являются входами устройства, выход каждого регистра соединен с входом соответствующего блока памяти, отличающееся тем, что, с целью сокращения аппаратных затрат, оно содержит (k+1) групп элементов И, группу элементов ИЛИ, группу элементов НЕ, |( вспомогательных регистров и регистр ранга, причем входы каждого из элементов ИЛИ группы соединены с выходами Элементов И соответствующей группы, входы вспомогательных, регистров являются установочными входами устройства, выход которого соединен с выходом регистра ранга, входы которого соединены с выходами соответствующих вспомогательных регистров , входы разрешения чтения которых соединены соответственно с выходами соответствующих элементов И (k+1)-и группы и выходом k -го элемента ИЛИ группы, первые входы элементов И (}; + 1)-й группы соединены с выходами соответствующих элеменi тов ИЛИ группы, выходы элементов ИЛИ группы с второго по k -исоединены соответственно с входами элементов НЕ группы, входы каждого из элементов И (+1)-й группы, начиная со второго, соединены соответственно с выходами элементов НЕ группы с номерами не меньшими номера элемента И, t-й выходр-и группы 1 -го блока памяти подключен к i -му входу 6 -го элемента И р -и группы (С 1,Lp, СП 1,0 1...k , где Lp - количество наборов вычетов).

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(5g С 06 F 5 02 .

OllHCAHHE ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3572530/18-24 (22) 04.04.83 (46) 23.07.84. Бюл. ¹ 27 ,(72) В.Н.Ахременко, А.А.Коляда, В.К.Кравцов, В.В.Ревинский и А.М.Старовойтов (71) Научно-исследовательский институт прикладных физических проблем им. акад. А.М.Севченко (53) 68 1.33(088.8) (56) 1. Авторское свидетельство СССР № 365701, кл. 0 06 F 5/02, 1973.

2. Авторское свидетельство СССР № 800989, кл. С 06 F 5/02, 1979 (прототип). (54) (57) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ

РАНГА ЧИСЛА, содержащее k регистров, блоков памяти, причем входы регистров являются входами устройства, выход каждого регистра соединен с входом соответствующего блока памяти, о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратных затрат, оно содержит (k+1) групп элементов И, группу элементов ИЛИ, группу элементов НЕ, вспомогательных регистров и регистр ранга, причем входы каждоÄÄSUÄÄ 1104501 A го из элементов ИЛИ группы соединены с выходами элементов И соответствующей группы, входы вспомогательных регистров являются установочными входами устройства, выход которого соединен с выходом регистра ранга, входы которого соединены с выходами соответствукнцих вспомогательных регистров, входы разрешения чтения которых соединены соответственно с выходами соответствующих элементов И (k+ 1)-й группы и выходом k -го элемента ИЛИ группы, первые входы элементов И (k+1)-й группы соединены с выходами соответствующих элементов ИЛИ группы, выходы элементов ИЛИ группы с второго по 4 -й соединены соответственно с входами элементов НЕ группы, входы каждого из элементов И (k+ 1)-й группы, начиная со второго, соединены соответственно с выходами элементов НЕ группы с номерами не меньшими номера элемента И, 1-й выход Р --й группы 1 -го блока памяти подключен к: i -му входу 3 -ro элемента И р -й группы (С = 1 Lp, ,р = t...k, где LР— количество наборов вычетов).

1 1 104501

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих цифровых вычислительных устройствах, работающих в остаточных системах счисления, для выполнения немодульных операций ,над числами невысокой разрядности (до 24 бит).

Известно устройство для формирования позиционных признаков непозици- 1ð онного кода, содержащее входной регистр, блок памяти для хранения конс, тант, входы которого подключены к выходам входного регистра, а выходык соответствующим входам блока после- 15 довательно соединенных двоичных сумматоров и дополнительного двоичного сумматора, по выходу подключенного к входу блока сумматоров, сумматор ранга числа, входы которого соединены с выходами переносов двоичных сумматоров, выходной сумматор, входы которого соединены с соответствующими выходами блока двоичных сумматоров, соединенными также через схему формирования переносов с входом сумматора ранга, выходной регистр и схему анализа содержимого старших разрядов результата, входы которых соединены с выходом выходного сумматора (1) .

Недостатком данного устройства является низкое быстродействие вслед" ствие использования последовательного. алгоритма формирования поправ35 ки Амер баев а.

Наиболее близким к изобретению по технической сущности является устройство для определения ранга числа„ содержащее ц регистров, блоки памя- 40 ти, сумматор ранга, П блоков суммирования, и -1 элемент сравнения, блок задания знака и дополнительный блок памяти, причем выход 1 -ro регистра () = 1, ..., П ) соединен с 4 входом (1,k, k +1) и (j,k, k +2)-ro блоков памяти (k = j -1,... и ) входы

1l -го блока суммирования (k = 3,...

N) соединены соответственно с выходами (i, k +2, k )-го (i, k 1 — К, )-ro 5О и (k, k — 1, k )-го блоков памяти (1 = 1, ..., k -1), 1 -й вход первого блока суммирования соединен с выходом (>,n, п )-го блока памяти (j = 1, ..., П ), первый и второй входы второ-55 го блока суммирования соединены соответственно с выходами (1,0,2) и (2, 1,2) блоков памяти, выходы 1 -ro u (+1)-го блоков суммирования подключены соответственно к первому и второму входам 1 -го элемента сравнения (1 2,..., Р -1), выходы первого и и -ro блоков суммирования подключены соответственно к первому и второму входам дополнительного блока памяти, выход которого подключен к первому входу сумматора ранга, выходы элементов сравнения соединены с соответствующими входами блока задания знака, выход которого соединен с вторым входом сумматора ранга, выход которого является выходом устройства (21.

Недостатками известного устройст ва являются большой обч.ем оборудования и низкое быстродействие.

Цель изобретения — сокращение аппаратурных затрат и повышение быстродействия устройства.

Поставленная цель достигается тем, что устройство для определения ранга числа, содержащее k регистров, k блоков памяти, причем входы регистров являются входами устройства, выход каждого регистра соединен с входом соответствующего блока памяти, содержит (k+1) групп элементов И, группу элементов ИЛИ, группу элементов НЕ, k вспомогательных регистров и регистр ранга, причем входы каждого элемента ИЛИ группы соединены с выходами элементов И соответствующей группы, входы вспомогательных регистров являются установочными вхоДами устройства, выход которого соединен с выходом регистра ранга, входы которого соединены с выходами соответствующих вспомогательных регистров, входы разрешения чтения которых соединены соответственно с выходами соответствующих элементов И (4+1)-й группы и выходом k, -го элемента ИЛИ группы, первые входы элементов И (4+1) и группы соединены с выходами соответствующих элементов ИЛИ группы, выходы элементов ИЛИ группы с второго по 1 -й соединены соответственно с входами элементов НЕ группы, входы каждого из элементов И (+1)-й группы начиная со второго, соединены соответственно с выходами элементов НЕ группы с номерами не меньшими номера элемента И, F -й выход р -й груп пы -ro блока памяти подключены к

-му входу Г -ro элемента И Р -й

1104501 группы (1=1, ... L 1,p =1,...

l() .

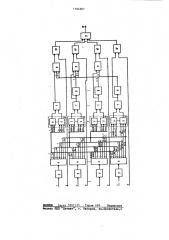

На чертеже приведена структурная схема устройства для определения ранга числа.

Устройство для определения ранга числа содержит входы 1 устройства, установочные входы 2 устройства, регистры 3, блоки 4 памяти, группы 5 элементов И 6, группу элементов ИЛИ 7, группу элементов НЕ 8, группу элементов И 9, вспомогательные регистры 10, регистр 11 ранга, выход 12 устройства.

Устройство для определения ранга числа работает следующим образом.

Остаточный код (of «„M >,...ф„„) исходного целого числа А через входы 1 устройства поступает во входные регистра 3, после чего 1 -я цифра й;„ кода подается на адресный вход 1 -го блока 4 памяти и из него считываются

<-е компоненты A e логических шкал

Ле= (К к,....,М кк ), (0 = 1,2,...

L) где

О, если оС1 oL, ,(.;) =

1, если в „> с ; — число наборов вычетов (е, кк )

Посредством установочных вводов 2 параллельно во вспомогательные регистры 10 устройства записываются константы 0,1,... к -1 соответственно.

Компоненты, считанные из блока 4 памяти поступают на входы элемента И 6, и на его выходе формируется Булова величина .A e.e(aL;„). Величины, полученные на вйходах элементов И 6 -й группы 5, подаются на соответствующие входы 1 -ro элемента ИЛИ 7, в результате чего на его выходе сформируется признак

L;

k . g>= V A аЕ,к ) Е; = 1;.

1=(,. 5=1

1-1

Если (= 1, то число (-1 рассмзт ривается в качестве значения нормированного ранга P (A) исходного .числа А.

Полученные величины у; поступают на первые входы элементов ИЛИ 7, на вторые входы которых через элементы HE 8 поступают проинвертированные значения („ . В результате на

10 выходе 1 -го элемента И 9 имеем п =9, ;„" Чк, который подается на вход разрешения !

5 чтения информации 1 -го вспомогательного регистра 10. На вход разрешения чтения информации " -го вспомогательного регистра 10, с выхода k -ro ..лемента ИЛИ 7 подается сигнал ь, = к . и л л

Среди сигналов а1,, ..., к, ненулевым является лишь 1,„, поэтому чтение информации происходит только из одного i -го вспомогательного регистра. Содержимое 1 -1 этого регистра, представляющее собой информационный ранг p (A) исходного числа А, передается в регистр 11 ранга числа, откуда он поступает на выход 12 устройства, на этом операция формирования нормированного ранга числа заканчивается.

Время работы предлагаемого устройства не зависит от числа модулей системы счисления и определяется временем срабатывания блоков памяти и логических элементов. Быстродействие известного устройства уменьшается пропорционального >k и уже при

40 к = 4 примерно в 2 раза меньше, чем у предлагаемого устройства.

Аппаратурные затраты предлагаемого устройства для k =- 4 примерно в пол45 тора раза меньше, чем у известного устройства.

1104S01

ВН1ВПй Заказ 5261/35 Тираж 699 По сное — — и — — и- У

Фнлнал ШШ Патент, г. Ужгород, ул.Проектная,4