Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ, содержащий входной дифференциаль( каскад на первом и втором транзисторах, имеющих одну структуру, эмиттеры которых объединены, а коллекторы через первый и второй резисторы соеданены с первой шиной источника питания, выходной каскад на третьем и четвертом транзисторах , имеющих другую структуру, включенных по схеме с общим эмиттером, базы которых соединены с коллекторами соответственно первого и второго транзисторов,, а коллекторы через соответственно гретий и четвертый резисторы - с первым выводом резистора обратной связи, второй вывод которого соединен с второй шиной источника питания, причем коллектор четвертого транзистора соединен с нагрузкой, отличающийся тем, что, с целью расщирения входного синфазного диапазона при одновременном увеличении нагрузочной способности, введены первый и второй дополнительные транзисторы, имеющие ту же структуру, что и структура первого и второго указанга 1х транзисторов, база и коллектор перi вого и база второго дополнительных транзисторов объединены, эмиттер первого дополнитель (Л ного транзистора подключен к второй шине истошика питашя, эмиттер второго дополнительного транзистора - к первому выводу резистора обратной связи, а его коллектор - к эмиттерам первого и второго транзисторов.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН а9) (10

3 Я9 Н F 45!

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

1 у.-аа «s ° Н ЙЯ.

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

AO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3308847/) 8-09 (22) 26.06.81 (46) 23.07.84. Бюл. У 27 (72) В. Я. Грошев (71) Научно-исследовательский институт элек тронной интроскопии при Томском ордена Октябрьской Революции и ордена Трудового Красного Знамени политехническом институте им. С.М. Кирова (53) 621.375.024(088.8) (56) 1. Патент США N 3959733, кл. Н 03 F 3/45, 25.05.76, 2. Патент CILIA N 3168709, кл. Н 03 F 3/45, 02.02.65 (прототип). (54) (57) ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ, содержащий входной дифференциальцай каскад на первом и втором транзисторах, имеющих одну структуру, эмиттеры которых объединены, а коллекторы через первый и второй резисторы соединены с первой шиной источника питания, выходной:каскад на третьем н четвертом транзисторах, имеющих другую структуру, включенных по схеме с общим эмиттером, базы которых соединены с коллекторами соответственно первого и второго транзисторов„а коллекторы через соответственно третий н четвертый резисторы - с первым выводам резистора обратной связи, второй вывод которого соединен с второй шиной источника питания, причем коллектор четвертого транзистора соединен с нагрузкой, о r л и ч а ю шийся тем, что, с целью расширения входного синфазного диапазона при одновременном увеличении нагрузочной способности, введены первый и второй дополнительные транзисторы, имеющие ту же структуру, что и структура первого и второго указанных транзисторов, база и коллектор первого и база второго дополнительных транзисто- cg

Ф ров объединены, эмиттер первого дополнительного транзистора подключен к второй шине источника питанин, амиттар второто Полонин. тельного транзистора - к первому выводу резистора обратной связи, а его коллектор- к эмиттерам первого и второго транзисторов.

1104648

Изобретение относится к радиотехнике и может использоваться в устройствах радиоэлектроники широкого применения, а именно в качестве составного элемента операционных усилителей, компараторов и цифровых схем. 5

Известен дифференциальный усилитель, содержаший два дифференциальных каскада усиления, источник тока смещения для первого дифференциального каскада, элементы нагрузки этого каскада, источник тока смещения для второго дифференциального каскада, причем элементы нагрузки входного и выходного каскадов подключены к разным шинам источника питания, причем цепь обратной связи по синфазному сигналу дифференци 15 аль ного усилителя (ДУ) содержит биполярный транзистор. структура которого совпадает с структурой транзисторов выходного каскада, эмиттер этого транзистора соединен с соответствующей шиной источника питания, а база 20 и коллектор подключены соответственно к выходам источников тока смешения выходного и входного дифференциальных каскадов (11, За счет обратной связи в этой схеме устанавливается необходимый ток смегцения вход- 25 ного дифференциального каскада и всего ДУ в целом. Диапазон изменения тока на выходе этого устройства равен току, отдаваемому .источником тока смещения выходного каскада, поэтому нагрузочную способность и скорость gp нарастания усилителя можно увеличивать лишь за счет увеличения токов смещения в каскадах, т.е. при снижении экономичности устройства.

Выходное сопротивление ДУ велико, поэтому для работы с низкоомными нагрузками необходим усилитель мощности.

Наиболее близким по технической сущности к изобретению является дифференциальный усилитель, содержашии входнои дифференци- 40 альный каскад на первом и втором транзис.торах, имеюших одну структуру, эмиттеры которых объединены, а коллекторы через первый и второй резисторы соединены с первой шиной источника питания, выходной каскад на третьем и четвертом транзисторах, имеюших

I другую структуру, включенных по схеме с общим эмиттером, базы которых соединены с коллекторами соответственно первого и второго транзисторов, а коллекторы через соот50 ветственно третий и четвертый резисторы - с первым выводом резистора обратной связи, второй вывод которого соединен с второй шиной источника питания, причем коллектор четвертого транзистора соединен с нагрузкой (2).

Однако рабочий режим каскадов дифференциального усилителя зависит от приложенного к его входам синфазного напряжения, причем изменение этого напряжения сопровождается

1 изменением важнейших параметров ДУ, таких как дифференциальный коэффициент усиления, частотные характеристики и тд.

Цель изобретения - расширение входного синфазного диапазона при одновременном увеличении нагрузочной способности, Цель достигается тем, что в дифференциальный усилитель, содержащий входной дифференциальный каскад на первом и втором транзисторах, имеющих одну структуру, эмиттеры которых объединены, а коллекторы через первый и второй резисторы соединены с первой шиной источника питания, выходной каскад на третьем и четвертом транзисторах, имеющих другую структуру, включенных по схеме с общим эмиттером, базы которых соединены с коллекторами соответственно первого и второго транзисторов, а коллекторы через соответственно третий и четвертый резисторы - с первым выводом резистора обратной связи, второй вывод которого соединен с второй шиной источника питания, причем коллектор четвертого транзистора соединен с нагрузкой, введены первый и второй дополнительные транзисторы, имеющие ту же структуру, что и структура первого и второго указанных транзисторов, база и коллектор первого и база второго дополнительных транзисторов объединены, эмиттер первого дополнительного транзистора подключен к второй шине источника питания, эмиттер второго дополнительного транзистора - к первому выводу резистора обратной связи, а его коллектор - к эмиттерам первого и второго транзисторов.

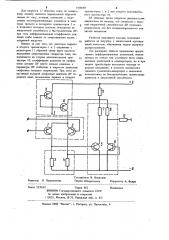

На чертеже представлена принципиальная электрическая схема дифференциального усилителя.

Дифференциальный усилитель, содержащий входной дифференциальный каскад (ДК) на первом и втором транзисторах 1 и 2, первый и второй резисторы 3 и 4, выходной каскад на третьем и четвертом транзисторах 5 и 6, третий и четвертый резисторы 7 и 8, первый и" второй дополнительные транзисторы 9 и 10, резистор 11 обратной связи, нагрузка 12.

Дифференциальный усилитель работает следующим образом.

Ток смещения для первого и второго транзисторов 1 и 2 задается вторым дополнительным транзистором 10, база. которого подключена к первому дополнительному транзистору 9 в диодном включении, а эмиттер через резистор 11 обратной связи подключен к шине источника питания.

ДУ охвачен отрицательной обратной связью по синфаэлому сигналу за счет подключения третьего и четвертого резисторов 7 и 8 к эмиттеру второго дополнительного транзистора 10.

Составитель И. Водяхина

Техред Л.Мартяшова Корректор А. Фоври

Редактор H. Пушненкова

Заказ 5320/42 Тираж 862

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 з 110464

Лля нагрузки 12 обратная связь пп сипфазному сигналу является параллельной обратной связью по току, которая, совместно с отсутствием токоограничивающнх элементов в эмит. тсрах третьего и четвертого транзисторов 5 и

6 позволяет получить высокие показатели по нагруэочной способности и быстродействию ДУ, при этом дифференпиальный коэффициент уси.ления слабо зависит от сопротивления несим- . метричной нагрузки. 1О

Однако за счет того, что эмиттеры первого и второго транзисторов 1 и 2 соединены с резистором 11 обратной связи через высокое внутреннее сопротивление генератора тока, выполненного на втором дополнительном транзисторе 10, коэффициент усиления по синфазному сигнапу ДУ много меньше единицы, а параметры ЛУ стабильны в широком диапазоне синфазных входных напряжений. При этом допустимый входной синфаэный диапазон ЛУ ограничен лишь насыщением первого и второго транзисторов l и 2 или второго дополнительного транзистора 10.

ДУ обладает также широком динамическим диапазоном по выходу, что совместно с высокой нагруэочной способностью ДУ позволяет использовать его без специалнзированн го усилителя мощности.

Свойства выходного каскада позволяют работать на нагрузку с значительной шунтируюшей емкостью, обеспечивая малую задержку распространения.

Это расширяет область применения предлагаемых дифференциальных усилителей, используемых не только как составную часть операционных усилителей и компараторов, но и при защите транзйсторов выходного каскада от режима насыщения, в качестве логического элемента (усилителя-инвертора) с высокими показателями по быстродействию, помехоэащищенности и нагрузочной способности.