Устройство для управления переключением скользящего резерва

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРЕКЛЮЧЕНИЕМ СКОЛЬЗЯЩЕГО РЕЗЕРВА , содержащее ко|р1утатор, элементы контроля основных и резервных блоков и матрицу логических узлов, включенную мелду выходами элементов контроля основных и резервных блоков и входами коммутатора,причем выход элемента контроля казвдого резервного блока соединен с первыми входами логических узлов соответствующей строки матрицы, о т л ичающееся тем, что, с целью упрощения устройства, коммутатор выполнен из независимых подкоммутаторов , каждый из которых содержит входы управления по числу резервных блоков, матрица логических узлов содержит один дополнительный столбец и по числу резервных блоков допоп- . нительные строки, причем выход элемента контроля каждого основного блока соединён с первыми вxoдa 0l всех логических узлов соответствующей строки матрицы, второй и третийвходы (i,j)-ro логического узла матрицы соединены с первым выходом d-t,j)-го логического узла и вторым выходом (, j-1)-ro логического узла матрицы соответственно, причем третьи выходы всех логических узлов i-й строки матрицы соединен, с соответствующими вхЬдами управления .t -го подкоммутатора. 2. Устройство по П.1, о т л ичающе .еся тем, что логический узел матрицы состоит из трех двухвходовых элементов И-НЕ, причем «ервый и второй входы первого элемента И-НЕ соединены соответственно с первым и вторьи входами узла, первый и второй входы второго элемента И-НЕ соединены соответственно с выходомпервого элемента И-НЕ и вторым входом узла, и второй входы третьего элемента И-НЕ соединены соответственно с третьим входом узла и выходом первого элемента И-НЕ, причем выход первого элемента И-НЕ соединен с третьим выходом узла.

СОЮЗ СОВЕТСНИХ

INVIIO

РЕСПУБЛИК

G 06 F 11/20; H 05 К 10/OC

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬПЗФ ф "гРх и @л 1„, ОПИСАНИЕ ИЗОБРЕТЕНИЯ 1

К ILB TOPCNOMV СЗИДЕТВВСТВМ

ЮФ

5Щ 110 1.; (21) 3543125/18-24 (22) 10.01 .83 (46) 07.08.84. Бюл. 9 29 (72) В.И. Варшавский, О.В. Маевский, Ю.В. Мамруков, В.Б. Мараховский, Л.Я. Розенблюм и В.И. Тимохин (71) Ленинградский ордена Ленина электротехнический институт им. В.И. Ульянова (Ленина) (53) 681. 3-19 (088.8) (56) 1. Авторское свидетельство ССС"

Р 237463, кл. С 06 F 11/00, 1967.

2. Авторское свидетельство СССР

У 545985, кл. G 06 F 11/00, 1974. (54) (57) 1. УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРЕКЛЮЧЕНИЕМ СКОЛЬЗЯЩЕГО РЕ3ЕРВА, содержащее коммутатор, элементы контроля основных и резервных блоков и матрицу логических узлов, включенную между выходами элементов контроля основных и резервных блоков и входами коммутатора,причем выход элемента контроля каждого резервного блока соединен с первыми входами логических узлов соответствующей строки матрицы, о т л ич а ю щ е е с я тем, что, с целью упрощения устройства, коммутатор выполнен из независимых подкоммутаторов, каждый из которых содержит входы управления по числу резервных

„Я0„„1107127 A блоков, матрица логических узлов содержит один дополнительный столбец и по числу резервных блоков дополнительные строки, причем выход элемента контроля каждого основного блока соединен с первыми входами всех логических узлов соответствующей строки матрицы, второй и третий входы (i, j )-ro логического узла матрицы соединены с первым выходом (1-1, j)-го логического узла и вторым выходом (1, j -1)-ro логического узла матрицы соответственно, причем третьи выходы всех логических узлов

j-й строки матрицы соединены, с соответствующими вхЬдами управления .1-го подкоммутатора.

2. Устройство по п.1, о т л ич а ю щ е е с я т зм, что логический узел матрицы состоит из трех двухвходовых элементов И-НЕ, причем первый и второй входы первого элемента И-НЕ соединены соответственно с первым и вторым входами узла, первый и второй входы второго элемента И-НЕ соединены соответственно с выходом. первого элемента И-НЕ и вторым входом узла, перйый и второй входы третьего элемента И-НЕ соединены, соответственно с третьим входом узла и выходом первого элемента И-НЕ, причем выход первого элемента И-НЕ соединен с третьим выходом узла. с числом строк, равным числу резервных блоков, и с числом столбцов, равным числу основных блоков (2 ).

Недостатком известных устройств является их большая сложность.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что в устройстве для управления переключением скользящего резерва, содержащем коммутатор, элементы контроля основных и резервных блоков и матрицу логических узлов, включенную между выходами элементов контра- 5 ля основных и резервных блоков и входами коммутатора, причем выход элемента контроля каждого резервного блока соединен с первыми входами логических узлов соответствующей строки матрицы, коммутатор выполнен из независимых подкоммутаторов, каждый из которых содержит входы управления по числу резервных блоков, матрица логических узлов содержит один дополнительный столбец и по числу резервных блоков дополнительные строки, причем выход элемента контроля каждого основного блока соединен с первыми входами всех логических узлов соответствующей строки матрицы, второй и третий входы (1 j )-ro логического узла матрицы соединены с первым выходом (1 -1,j)-го логического узла и вторыми выходом (i 1-1)-го логического узла матрицы соответственно, причем третьи вьпсоды всех логических узлов

Ф 11071

Изобретение относится к автоматике и вычислительной технике и может быть использовано для резервированияфункционально законченных узлов радиоэлектронной аппаратуры, каналов

5 связи. и передачи данных.

Известно устройство для управления переключением скользящего резерва, содержащее коммутатор, управляющие входы которого соединены с элементаьи1б контроля основных и резервньгх блоков (1).

Наиболее близким техническим решением к изобретению является устройство для управления переключением скользящего резерва, содержащее коммутатор, элементы контроля основных и резервных блоков и матрицу из элементов И-НЕ, включенную между элементами контроля и коммутатором, 27 2

1-й строки матрицы соединены с соответствующими входами управления i-ro подкоммутатора.

Логический узел матрицы со тоит из трех двухвходовых элементов И-НЕ, причем первый и второй входы первого элемента И-НЕ соединены соответственно с первым и вторым входами узла, первый и второй входы второго элемента И-НЕ соединены соответственно с выходом первого элемента И-HE u вторым входом узла, первый и второй входы третьего элемента И-НЕ соединены соответственно с третьим входом узла и выходом первого элемента И-НЕ, причем выход первого элемента И-НЕ соединен с третьим выходом узла.

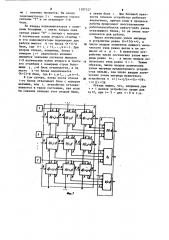

На фиг.1 представлена схема устройства, на фиг.2 — схема логичес- кого узла матрицы.

Устройство содержит (фиг.1) элементы 1 контроля основных и резервных блоков, коммутатор 2, состоящий из независимых подкоммутаторов 2 1 и матрицу 2 логических узлов 3 i,> с входами 4-6 и выходами 7-9.

Логический узел содержит (фиг.2) первый 10, второй 11 и третий 12 элементы И-НЕ.

Устройство работает следующим образом.

Прн исправных основных и резервных блоках на выходах всех элементов 1 присутствуют сигналы "1". На вход 5 логического узла первой строки первого столба подается сигнал

На остальные входы 5 логических узлов первой строки подается сигнал "0". На входы 6 логических узлов первой строки подается сигнал "1". При этом на выходах

7-9 логических узлов первого столбца устанавливаются соответственно сигналы "1", "1" и "0". На выходах 7-9 остальных логических узлов матрицы 3 устанавливаются соответственно сигналы "0", "0" и "1™.На входах подкоммутаторов 2i, только один сигнал равен "0" - сигнал с выходов 9 логических узлов первого столбца, а остальные сигналы равны

В этом состоянии подкоммутатор 2i подключает для работы

1-й блок. При отказе, например,;1-го блока с выхода i --го элемента 1 контроля подается сигнал "0".

Значения сигналов на выходах 7-9 логических узлов первого и второго столбцов с номерами строк больши3 110 ми 1 взаимно меняются. На входы подкоммутатора 2 1 . подаются только сигналы "1" и он отключает 1-й блок.

На входах подкоммутаторов с номерами большими ) опять только один сигнал равен "0™ — сигнал с выходов

9 логических узлов второго столбцаи эти подкоммутаторы подключают для работы вместо k -го блока (K+1)-й блок, где K - =i, i +1,...,n+r-1. При втором отказе, например, блока с номером j »i аналогично взаимно меняются значения сигналов выходов

7-9 логических узлов второго и треть" его столбцов с номерами строк большими J j-й блок отключается, а на место К -го блока подключается (К+2)-й блок, где К = 1, j+1 М+г-2.

В том случае, когда после отказа

i-ro блока отказывает блок с.номером .меньшим, чем 1, устройство устанавливается в такое состояние, как если бы сначала отказал этот второй блок, пп а затем блок:, . При большей кратности отказов устройство работает аналогично, причем если в процессе работы происходит восстановление

5 работоспособности какого-либо ранее отказавшего блока, то он вновь подключается для работы.

Число логических узлов матрицы в устройстве равно (1",+1)(й+ ); а

1б число входов элементов каждого логического узла равно шести и ие зависит от ь и . В известном устройстве число логических узлов матрицы равно nr, а число входов ло-15 гического узла равно ll + г. Таким образом, число входов логических узлов матрицы предлагаемого устройства меньше, чем число входов логических узлов матрицы известного

2О устройства в пr (л+e)/(и+r)(r+1) &=

= п I (r 1)6, Откуда видно, что, например. при

1 данное устройство проще для п»12, при г= 3 — для и> 8 и т.д.

1102127

Составитель В. Максимов

Техреду.Ф.Дубинчак. Корректор И. Шулла ф

Редактор С. Пекарь

Тиран 699 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

3!3035, Москва, Ж-35, Рауаская наб., д . 4/5

Заказ 5760/34

Филиал ППП "Патент", r.Óàãîðîä, ул. Проектная,4