Операционное устройство мультимикропроцессорной системы

Иллюстрации

Показать всеРеферат

ОПЕРАЦИОННОЕ УСТРОЙСТВО МУЛЬТИМИКРОПРОЦЕССОРНОЙ СИСТЕМЫ,содержащее дешифратор кода микрокоманды , первый информационный вход которого соединен с первым информационным входом устройства, а выход - с информационным входом первого регистра, выход которого соединен с управляющими входами арифметикологического блока, первого, второго, третьего и четвертого коммутаторов и блока регистров общего назначения, информационный вход которого соединен с первым информационным входом первого коммутатора, информационным входом второго регистра, выходом третьего коммутатора и является выходом устройства, второй информационный вход устройства соединен с вторым информационным входом первого коммутатора и первыми информационными входами второго и четвертого коммутаторов, вторые информационные входы которых соединены соответственно с выходами второго регистра и блока регистров общего назначения, выход первого коммутатора соединен с информационным входом третьего регистра , выход которого соединен, с третьим информационным входом второго коммутатора, выход которого соединен с первьм информационным входом арифметико-логического блока, второй информационный вход которого соединен с выходом четвертого коммутатора и первым информационным входбм третьего коммутатора, второй информационный вход которого соединен с выходом арифметико-логического блока, отличающееся тем, что, с целью повышения гибкости функционирования , оно содержит блок модификации , содержащий элемент ИЛИ и группу элементов И, первые входы которых соединены с выходом элемента ИЛИ, вторые входы - с управляющим входом устройства, а выходы элемен .тов И группы соединены с вторым информационным входом дешифратора кода микрокоманды, первый и второй входы элемента ИЛИ соединены соответственно с третьим информационным входом устройства и с признаком модификации устройства.

СОЮЗ СОВЕТСНИХ

Р,ИЦ

РЕСПУБЛИК

09) Ol) зш

ГОСУДАРСТВЕННЫЙ HOMHTET СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТЬСЯ

ОПИСАНИЕ ИЗОБРЕТЕНИ

Ъйь. ЙИ сна

N ABTOPctloMV % (21) 3433142/18-24 (22) 30.04.82 (46) 07.08.84. Бюл. Р 29 (7 2) Б. Г. Фрадкин (71) Таганрогский радиотехнический институт им. В.Д. Калмыкова (53) 681. 32 (088.8) (56) 1. Авторское свидетельство СССР

Р 860078, кл. G 06 F 15/32, 1979.

2. Танкелевич P.Ë. Моделирующие микропроцессорные системы. М., "Энергия", 1979 (прототип). (54)(57) ОПЕРАЦИОННОЕ УСТРОЙСТВО

МУЛЬТИМИКРОПРОЦЕССОРНОЙ СИСТЕМЫ,содержащее дешифратор кода микрокоманды, первый информационный вход которого соединен с первым информационным входом устройства, а выход — с информационным входом первого регистра, выход которого соединен с управляющими входами арифметикологического блока, первого, второго, третьего и четвертого коммутаторов и блока регистров общего назначения, информационный вход которого соединен с первым информационным входом первого коммутатора, информационным входом второго регистра, выходом третьего коммутатора и является выходом устройства, второй информационный вход устройства соецинен с вторым информационным входом первого коммутатора и первыми информационными входами второго и четвертого коммутаторов, вторые информационные входы которых соединены соответственно с выходами второго регистра и блока регистров общего назначения, выход первого коммутатора соединен с информационным входом третьего регистра, выход которого соединен. с третьим информационным входом второго коммутатора, выход которого соединен с первым информационным входом арифметико-логического блока, второй информационный вход которого соединен с выходом четвертого коммутатора и первым информационным входом треть- Е его коммутатора, второй информационный вход которого соединен с. выходом арифметико-логического бпока, о т л и ч а ю щ е е с я тем, что, с целью повышения гибкости функцио- Н нирования, оно содержит блок модйфикации, содержащий элемент ИЛИ и группу элементов И, первые входы которых соединены с выходом элемеи та ИЛИ, вторые входы — с управляющим входом устройства, а выходы элементов И группы соединены с вторым информационным входом дешифратора кода микрокоманды, первый и второй входы элемента ИЛИ соединены соответственно с третьим информационным входом устройства и с признаком модификации устройства. Ъ

1107128

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке и конструировании мультимикропроцессорных вычислительных систем.

Известно устройство для решения дифференциальных уравнений, содержащее регистры, блок умножения и сумматор Р17.

Недостатком данного устройства является ограниченность функциональных возможностей.

Наиболее близким по технической сущности к изобретению является микропроцессор, содержащий дешифратор кода микрокоманды, соединенный с регистром, выходы которого соединены с управляющими входами коммутаторов, блока регистров общего назначения (POH) и арифметико-логического блока (АЛБ), выход которого соединен через коммутаторы с другими регистрами и блоком РОН, выходы которых соединены через другие коммутаторы с входами АЛБ (2).

1О

Недостатком известного устройства является ограниченная гибкость функционирования в мультимикропроцессорной системе с одним потоком команд.

Здесь при выполнении условных переходов различным микропроцессорам требуютсяя р а зличные ми кр ок оманды из общей микропрограммы, что приводит к необходимости дублирования микропрограммы для каждого микропроцессора или к необходимости специальной синхронизации вычислений, ограничивающей возможности их параллельного выполнения.

Цель изобретения — повышение гиб40 кости функционирования .

Поставленная цель достигается тем, что в операционное устройство мультимикропроцессорной системы, содержащее дешифратор кода микроко45 манды, первый информационный вход которого соединен с первым информационным входом устройства, а выход — с информационным входом первого регистра, выход которого подключен к управляющим входам арифме- тико-логического блока, первого, второго, третьего и четвертого коммутаторов и блока регистров общего назначения, информационный вход которо- 5 го соединен с первым информационным входом первого коммутатора, информационным входом второго регистра, выходом третьего коммутатора и является выходом устройства, второй информационный вход устройства соединен с вторым информационным входом первого коммутатора и первыми информационными входами второго и четвертого коммутаторов, вторые информационные входы которых соединены соответственно с выходами второго регистра и блока регистров общего назначения, выход первого коммутатора соединен с информационным входом третьего регистра, выход которого соединен с третьим информационным входом второго коммутатора, выход которого соединен с первым информационным входом арифметико-логического блока, второй информационный вход которого соединен с выходом четвертого коммутатора и первым информационным входом третьего коммутатора, второй информационный вход которого соединен с выходом арифметико-логического блока, введен блок модификации, содержащий элемент ИЛИ и группу элементов И, первые входы которых соединены с выходом элемента ИЛИ, вторые входы— с управляющим входом устройства, а выходы элементов И группы соединены с вторым информационным входом дешифратора кода микрокоманды, первый и второй входы элемента ИЛИ соединены соответственно с третьим информационным входом устройства и с признаком модификации устройства.

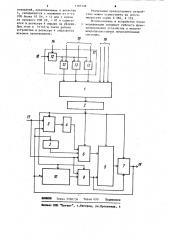

На чертеже представлена структурная схема устройства.

Устройство содержит дешифратор

1 кода микрокоманды, первый 2,второй 3, третий 4 регистры, первый 5, второй 6, третий 7, четвертый 8 коммутаторы, АЛБ 9, блок 10 РОН, бпок 11 модификации, содержащий элемент ИЛИ 12 и группу элементов И 13.

Входы 14-18 являются входом признака модификации и соответственно управляющим и первым, вторым, третьим информационными входами устройства, выход 19 - выходом устройства.

Дешифратор 1 кода микрокоманды предназначен для преобразования кода микрокоманды, поступающего на его входы, в совокупность управляющих сигналов, записываемых в регистр 2.

Регистры 3 и 4 и блок 10 POH служат для хранения операндов и

1107128

Код микрокоманды при такте

Вход

) 2-м ) 3-м

15, 16

А В

1 1

17

18

М„М„„

Результатов операций, выполняемых в АЛБ 9.

Коммутаторы 5-8 предназначены для организации обмена данными в уст-. ройстве.

Блок 11 модификации предназначен для модификации части кода микрокоманды, поступающей на вход 15 устройства, путем ее стробирования на элементах И 13 информацией на входе

18. При этом элемент ИЛИ 12 служит для маскирования процесса модификации, если признак модификации, поступающий на вход 14, равен "1".

Вход 16 служит для подачи немодифицируемой части кода микрокоманды, вход 17 — для подачи операнда.

Таблица составлена с учетом совмещения во времени приема данной микрокоманды и выполнения предыдущей микрокоманды. При этом при подаче кода микрокоманды В,С на входы 15 и 16 на входы 15 подаются разряды кода, содержащие адрес К -ro РОН,на входы 16. — остальные разряды кода.

Одновременно на вход 14 поступает признак модификации, для которого в формате микрокоманды предусматривается дополнительный разряд.

На первом такте работы устройства сигнал "1" с входа 14 поступает через элемент ИЛИ 12 блока 11 на группу элементов И 13, которые открываются, и в дешифратор 1 кода микрокоманды поступает код Д микрокоманды. Во втором такте она выполняется, и нулевая информация на входе 17 записывается в регистр 4. Одновременно в дешифратор 1 поступает код Ь микрокоманды и дешифрируется в нем.

Соответственно в третьем такте микрокоманда В выполняется и параллельный код множимого М записываУстройство работает следующим образом.

Пусть, например, выполняется умножение положительных чисел . При этом пусть А — двоичный код микрокоманды "Передать информацию с входа 17 в регистр 4;  — двоичный код микрокоманды Передать информацию с входа 17 в k-й РОН"; С вЂ” двоичный код микрокоманды "Сложить информацию в регистре 4 и в k-м POH и сдвинуть результат в регистре 4 вправо"; Мпараллельный код множимого, М вЂ” i -й (1 = 1,..., n) разряд множителя, считая со стороны старших разрядов.

Тогда выполнение умножения обеспечивается при потактном распределении информации на входах устройства в соответствии со следующей таблицей. м

4-м 5-м ° ° . (N-3)-м ется с входа 17 в K -й POH блока 10.

35 Одновременно в дешифратор 1 поступает код В микрокоманды, модифицированный в блоке 11 следующим образом. Значение "0" признака модификации на входе 14 пропускает

40 через элемент ИЛИ 12 информацию с входа 18, на котором в третьем такте содержится "0". Элементы И 13 закры-ваются и взамен адреса к-го РОН в коде В на входе 15 блок 11 мо45 дификации передает в дешифратор

t нулевую информацию, определяющую адрес нулевого POH. При выполнении в четвертом такте модифицированной таким образом микрокоманды информа5О ция с входа 17 "О" запишется в нулевой POH.Аналогично в блоке 11 происходит модификация кода С мнкрокоманды и в зависимости от значения "1" или "0" разряда множителя H. на

55 входе 17 в (v+4-i)-м такте в дешифратор 1 поступает адрес К-ro или нулевого POH. Соответственно при выполнении микрокоманды в следующем (й +3-i)-м такте сумма частичных про1107128

ВНИИПИ Заказ 57бО/34 Тираж б99 Подписное

Филиал ППП."Патеит", r.Óæãîðîä, ул.Проектная, 4 изведений, накапливаемая в регистре

4, складывается с множимым из И -го

POH блока 10 (M; = 1) или с нулем из нулевого POH (М; = О) и сдвигается в регистре 4 вправо на разряд.

При,этом в (е+4)-м такте работы устройства в регистре 4 образуется искомое произведение.

Реализацию предлагаемого устройства можно осуществить íà основе микросхем серии К 584, К 155.

Использование в устройстве блока

5 модификации повышает гибкость функционирования устройства в мультимикропроцессорных вычислительных системах.