Запоминающее устройство

Иллюстрации

Показать всеРеферат

СОЮЗ СОБЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

3(51) 0 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВ, /

ГОСУДАРСТБЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3586483/18-24 (22) 29. 04. 83 (46) 07.08.84. Бюл. Р 29 (72) Г.A.Áoðîäèí, Е.A.Âåðíèêîâñêèé, В. К. Коноп ель к о и В. В. Лосев (71 ) Минский радиотехнический институт (53) 681.327(088.8) (56) 1. Авторское свидетельство СССР

Р 957273, кл. G 11 С 11/00, 1982.

2. Экспресс-информация. Сер. "Вычислительная техника", 1981, 9 28, с. 7-11 (прототип). (54)(57) 1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блоки памяти, первые и вторые входы которых соответственно объединены и являются одним из адресных и управляющим входами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения эффективной емкости устройства, в него введены блоки выборки информации, блоки реконфигурации памяти, группы элементов И с первого по пятый, мажоритарные элементы, группы элементов ИЛИ, причем входы блоков выборки информации являются другим адресным входом устройства, выходы блоков выборки информа. ции соединены с первыми входами первых элементов ИЛИ групп, вторые вх6ды которых и входы соответствующих блоков реконфигурации памяти являются контрольными входами устройства, первые входы элементов И каждой группы подключены к выходам одноименного блока реконфигурации памяти, вторые входы элементов И каждой группы с первого по четвертый подключены к выходу одноименного блока памяти, второй вход пятого элемента И каж„.,BU„,3 К7 À дой группы соединен с выходом второго элемечта ИЛИ одноименной группы, входы которого соединены с выходами первого элемента одноименной группы и одноименного мажоритарного элемента, первый, второй и третий входы которого соединены соответственно с выходами второго, третьего и четвертого элементов И одноименной группы, выход первого элемента ИЛИ каждой группы соединен с третьим входом одноименного блока памяти и третьими входами третьего, четвертого и пятого элементов И одноименной группы, выходы пятых элементов И групп являются выходом устройства, выходы третьих и четвертых элементов И группа соответственно объединены.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что каждый блок выборки информации содержит первую д группу элементов памяти и блок сравнения, одни из входов которого являются входами блока, а другие соединены с выходами элементов памяти пер вой группы, причем выход блока сравнения является выходом блока.

3. Устройство по п. 1, о т л ич а ю щ е е с я тем, что каждый блок реконфигурации памяти содержит вторую группу элементов памяти и элементы ИЛИ, причем первые входы элементов ИЛИ с первого по четвертый являются входом блока, вторые входы соединены с выходами элементов памяти второй группы, выходы первого и вто- 1, рого элементов ИЛИ соединены с.входа- ми пятого элемента ИЛИ, выходы элементов ИЛИ являются выходами блока.

1107177

Изобретение относится к вычислительной технике и может быть использовано при изготовлении запоминающих устройстн с матричной организацией на одном кристалле.

Изобретение целесообразно исполь3онать при производстве cBерхбольших интегральных схем памяти с матричной организацией, имеющих большую площадь кристалла, где требуется нысокая емкость памяти. 10

Известно запоминающее устройство, содержащее элементы памяти, схемы логики обрамления, позволяющие производить обращение при записи и считывании информации только к одному эле- 15 менту памяти матрицы и осуществлять коррекцию сигналов с дефектных элементов памяти (11.

Недостатками этого запоминающего устройства являются невысокие надежность и быстродействие из-за сложности блоков контроля, большой задержки сигналов в них, введения большого числа разрядных элементов памяти.

Наиболее близким техническим реше- 5 ни ем к изобретению является система памяти, содержащая устройства памяти, первые и вторые адресные входы, управляющие входы, выход системы, соединенный с первыми выходами устройств, причем первые адресные и управляющие входы системы соединены с первыми и вторыми входами запоминающих блоков в каждом из устройств. Эта система позволяет производить коррекцию как отдельных дефектных элементов памяти, слов, разрядов в запоминающих блоках,-так и замену дефектных блоков на исправ ные (2 ).

Однако известная система характеризуется большой избыточностью и не 40 позволяет использовать для хранения отдельные дефектные блоки, что уменьшает эффективно используемую емкость памяти.

Целью изобретения является повышение эффективной емкости устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее блоки памяти, первые и вторые входы которых соответственно объединены и являются одним из адресных и управляющим входами устройства, введены блоки выборки информации, блоки реконфигурации памяти, группы элементов И с первого по пятый, мажоритарные элементы, группы элементов

ИЛИ, причем входы блоков ныборки информации являются другим адресным входом устройства, выходы блоков вы.борки информации соединены с первыми входами первых элементов ИЛИ групп, вторые входы которых и входы соответствующцХ блоков реконфигурации памяти являются контрольными входами устройства, первые входы элементов

И каждой группы подключены к выхо- 6> дам одноименного блока реконфигурации памяти, вторые входы элементов И каждой группы с первого по четвертый подключены к выходу одноименного блока памяти, второй вход пятого элемента И каждой группы соединен с выходом второго элемента ИЛИ одноименной группы, входы которого соединены с выходами первого элемента одноименной группы и одноименного мажоритарного элемента, первый, второй и третий входы которого соединены соответственно с выходами второго, третьего и четвертого элементов И одноименной группы, выход первого элемента ИЛИ каждой группы соединен с третьим входом одноименного блока памяти и третьими входами третьего, четвертого и пятого элементов И одноименной группы, выходы пятых элементов И групп являются выходом устройства, выходы третьих и четвертых элементов И групп соответственно объединены.

При этом каждый блок выборки информации содержит первую группу элементов памяти и блок сравнения, одни из входов которого являются входами блока, а другие соединены с выходами элементон памяти первой группы, причем выход блока сравнения янляется выходом блока.

Кроме того, каждый блок реконфигурации памяти содержит вторую группу элементов памяти и элементы ИЛИ, причем первые входы элементов ИЛИ с перного по четвертый являются входом блока, вторые входы соединены с выходами элементов памяти второй группы, выходы первого и второго элементов

ИЛИ соединены с входами пятого элемента ИЛИ, выходы элементов ИЛИ являются выходами блока.

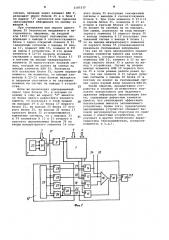

На фиг. 1 показана структурная схема части запоминающего устройства, относящейся к одному блоку памяти; на фиг. 2 — соединение указанных частей в единое запоминающее устройство.

Запоминающее устройство содержит блоки 1 памяти, адресные входы 2 и 3, управляющий вход 4, выход 5. Каждый блок 1 памяти имеет выход 6. Устройство также содержит (по числу блоков 1 памяти) блоки 7 выборки информации с выходами 8, группы элементов

ИЛИ 9 и 10, группы элементов И 11-15 с первого по пятый, мажоритарные элементы 16, блоки 17 реконфигурации памяти, имеющие выходы 18-22 ° Каждый блок 7 содержит первую группу элементов 23 памяти и блок 24 сравнения.

Каждый блок 17 содержит вторую группу элементов 25 памяти и элементы

ИЛИ 26-30. Одни из входов элементов

ИЛИ 9 и 26-30 соответственно объединены и являются управляющими входами 31 устройства. Элемент ИЛИ 9 имеет выход 32. Элементы И 13 и 14 имеют

1107177 выходы 33 и 34. Все блоки и элементы, показанные на фиг. 1, составляют запоминающий блок 35.

Элементы. И 13-15 работают следующими образом.

Когда уровни сигналов на выходе

32 элемента ИЛИ 9 и выходах 20-22 блока 17 высокие, элементы И 13-15 находятся в пРоводящем состоянии. сли же эти сигналы имеют низкий уро- 0 ень, то элементы И 13-15 находятся закрытом состоянии, характеризующемся высоким выходным сопротивлением, и не влияют на сигналы на шинах, к которым они подключены.

Элементы 23 и 25 памяти представляют собой программируемые элементы памяти и содержат плавкие вставки, занесение информации в которые (пере-. жигание вставок) может осуществляться, например, с помощью лазера. 20

Устройство работает следующим образом.

При изготовлении до пережигания вставок в элементах 23 и 25 происходит вначале функциональный контроль 25 исправности каждого из блоков 35 путем подачи на вход 31 соответствующего блока единичного сигнала и сигналов на входы 2 и 4. При этом на выходе 32 элемента ИЛИ 9 опрашиваемого 30 блока 35 (на входе 31 которого содержится единичный сигнал) присутствует единичный сигнал, который разрешает опрос блока 1 для записи и считывания информации. КРоме того, единичный сигнал на входе 31 устанавливает на всех выходах 18-22 блока 17 реконфигурации единичные сигналы, которые удерживают открытыми элементы И 14, 15, 11 и 12. Благодаря это му на выходе опрашиваемого блока 35 считывается без изменения сигнал с выхода 6 соответствующего блока 1.

В это время остальные все блоки 35 не опрашиваются (закрыты), так как на выходе 32 элемента ИЛИ 9 этих бло-45 ков присутствует нулевой сигнал, который удерживает элементы И 13-15 в закрытом состоянии.

В зависимости от исправности опрашиваемых блоков 35 в элементы 23 и

25 памяти блоков 35 заносится информация следующим образом.

Вначале поочередно проверяется исправность всех блоков 35. Блоки 35

55 называют исправными, если в соответствующих блоках 1 не содержится дефектных элементов или они заменены внутренним резервом блока. При исправности соответствующего блока 35 в элементы 23 памяти заносится код

60 адреса этого блока (в .порядке очередности следования исправных блоков ).

Например, если необходимо собрать запсминающее устройство из 16-ти блоков 35, то адресные входы 3 состоят из четырех шин. Тогда»ри:»Реп..»енин первого исправного б»ока 3 . ему присваивается код 1000 и пережигаются соответствующие вега зк и <- элемента 23, настраивающие блок 7 на этот код. При определении c",åлующего и".и— равного блока 35 в элементы 23 этого блока заносится уже код 0100 и т.д. Кроме того, в элемент 25 памяти, соединенный выходом с нхоцом первого элемента ИЛИ 26 блока 17 каждого из исправных блоков 35, заносится единичный сигнал путем персжигания вставки.

Пусть, например, в запоминающем устройстве исправных блоков 35 оказалось двенадцать, т.е. последнему из исправных блоков 35 присвоен номер

0011, который хранится в элементах

23 памяти этого блока.

Одновременно с проверкой исправности блоков 35 в память контролирующей установки (не показана), осуществляющей функциональный контроль, заносятся адреса дефектных элементов, обойти которые внутренним резервом блока 1 не удалось из-за превышения числа дефектов над резервом блока.

Установка определяет триады дефектных блоков, в которых по одному и тому же адресу "2" содержится не более одного дефектного элемента. Таких блоков достаточно много, поскольку дефекты распределяются, в основном, случайно и равномерно по кристаллу.

При этом происходит нумерация триад и присвоение им адресов исправных блоков 35 в порядке очередности.

Так, для приведенного примера первой триаде присваивается код 1011 (тринадцатый исправный блок 35), второй0111 и т.д. Эти адреса заносятся в элементы 23 памяти каждого из блоков

35 триады. Кроме того, произвольньж образом устанавливается очередность блоков 35 в триаде и в зависимости от этого пережигается плавкая вставка элементов 25 памяти в каждом блоке. Например, если блок 35 в триаде первый, в элемент 25 памяти, соединенный выходом с входом элемента

ИЛИ 27 блока 17, заносится единичный сигнал путем пережигания вставки.

Если же блок 35 второй в триаде, пережигается вставка в элементе памяти 25, соединенном выходом с входом элемента ИЛИ 28 блока 17 и т.д.

Благодаря подобного рода занесению программируемой информации в процессе изготовления при записи информации в процессе эксплуатации при подаче адресного сигнала на входы 3 устройства происходит опрос одного или трех блоков 35, поскольку на выходе 8 блока 7 этих блоков 35 устанавливается единичный сигнал. Этот

1107177 сигнал, проходя через элемент ИЛИ 9, разрешает опрос блоков 35 и н блок 1 по адресу "2" заносится для хранения записываемая информация по одному из входов 4.

При счи анин при опросе одного 5 блока 35 (полностью исправного и на строенного, например, на входной код 1000) происходит считывание информации с выхода б соответствующего блока 1 через открытый элемент И 11 (единичным сигналом с выхода 18 блока 17, элемент ИЛИ 10, элемент И 15) на выход 5 устройства. 8 это время элементы И 12-14 закрыты нулевыми сигналами с выходов 19-21 блока 17 15 и поэтому на выходе мажоритарного элемента 16 присутствует нулевой сигнал, который не нлияет на сигнал на выхода элемента ИЛИ 10. Поскольку все остальные блоки 35, кроме опраши-20 ваемого, не включены, то выхоцы элементов И 13-15 этих блоков находятся в закрытом состоянии и не оказЫвают влияния на сигнал на выходе 5 устройства. 25

Если же происходит одновременный опрос трех блоков 35, в которых по одному и тому же адресу "2" имеется не более одного дефектного элемента памяти, то поскольку в этой триаде на выходах 19 и 22 блока 17 первого блока 35, на выходе 20 блока 17 второго блока 35, на выходе 21 блока 17 третьего блока 35 устанавливаются единичные сигналы, то с выходоь 33 и 34 элементов И 13 и 15 второго и . третьего опрашиваемых блоков 35 на входы мажоритарного элемента 16 перного блока 35 поступают считываемые сигналы с выходов б соответствующих блоков 1. При этом элементы И 13 и 14 . н первом блоке 35, элементы И 15 во втором и третьем блоках 35 закрыты и не влияют на сигналы на их выходах.

Тем самым, поскольку на вход мажоритарного элемента 16 первого блока 35 с выхода элемента И 12 поступает счи. тываемый сигнал с выхода 6 блока 1, то на выходе мажоритарного элемента

16 первого блока 35 устанавливается правильно считываемая информация (так как из трех одновременно опрашиваемых элементов памяти два нсегда исправны ), которая поступает через элементы ИЛИ 10, элемент И 15 на выходы первого блока 35 и далее на выход 5 устройства. Сигнал на втором выходе элемента ИЛИ 10 первого блока 35 н этом режиме работы равен нулю, так как элемент И 11 закрыт нулевым сигналом с выхода 18 блока 17 и поэтому не влияет на считываемый сигнал через первый вход элемента ИЛИ 10.

Таким образом, предлагаемое устройство н отличие от известного позволяет использовать для надежного хранения информации запоминающие блоки, содержащие дефектные элементы памяти, что увеличивает эффективно используемые емкости запоминающего устройства. Кроме того, предлагаемое запоминающее устройство обладает высокой регулярностью структуры по сравнению с известным устройством, что улучшает и другие технические характеристики (быстродействие, воспроизнодимость и т.д.) .

1107177

Фие. 2

Составитель В. Рудаков

Редактор A.Øèøêèíà Техред М. Кузьма Корректор В.Петраш

Заказ 5764/37 Тираж 575 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г.ужгород, ул. Проектная, 4