Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕ-ПЬ, содержащая входной дифференциальный каскад на первом и втором транзисторах одной структуры, объединенные эмиттеры которых через первый генераг тор тока соединены с одной шиной первого источника питания, коллектор первого транзистора - с одной шиной второго источника питания, первый регулирующий транзистор, коллектор которого является выходом дифференциального усилителя и соединен с первым выходом второго генератора тока, а эмиттер - с первым выводом первого резистора, второй регулирующий транзистор, второй и третий резисторы , третий генератор тока, о тличающийся тем, что, с целью повьш1ения точности коэффициента передачи, в него введены дополнительный дифференциальный каскад на третьем и четвертом транзисторах и дополнительный источник питания, при этом второй транзистор выполнен двухколлекторным , аструктура первого и второго регулирующих транзисторов, третьего и четвертого транзисторов противоположна структуре первого и второго транзисторов, причем эмиттеры третьего и четвертого транзисторов объединены и через третий генератор тока соединены с одной шиной дополнительного источника питания,, коллекторы - с соответствующими коллекторами второго транзистора и с базами соответственно второго и первого регулирующих транзисторов, (Л эмиттеров второго регулирующего транзистора соединен с базой третьего транзистора и через второй резистор с одной щиной второго источника питания , к которой подключен второй вывод первого резистора, а коллектор второго регулирующего транзистора соединен с базой первого транзистора и через третий резистор - с общей шиной, при этом баз-а четвертого транзистора соединена с эмиттером первого регулирующего транзистора, база второго транзистора - с источником входного напряжения , а второй вывод второго генератора тока - с одной шиной первого источника питания, причем другие шины всех источников питания подключены к общей шине.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

0% (И) з(50 Н 03 F 3/45 У" к

/ -®фар

-9 -а с =" тр

ОПИСАНИЕ ИЗОБРЕТЕНИЯ м.,"„-,," -- Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3546289/18-09 (22) 28.01.83 (46) 07.08.84. Бюл. Р 29 (72) В.В. Васильев и В.И, Капустников (71) Научно-исследовательский институт управляющих вычислительных машин

Научно-производственного объединения

"Импульс" (53) 621.375.024(088.8) (56) 1. Патент США У 4004247, кл. Н 03 F 3/45, опублик. 16.01.77.

2. Патент США 11 3689848, кл. Н 03 F 3/68, опублик. 05.09.72 (прототип). (54)(57) ДИФФЕРЕНЦИАЛЬНЬЙ УСИЛИТЕЛЬ, содержащая входной дифференциальный каскад на первом и втором транзисторах одной структуры, объединенные эмиттеры которых через первый генера-. тор тока соединены с одной шиной первого источника питания, коллектор первого транзистора — с одной шиной второго источника питания, первый регулирующий транзистор, коллектор которого является выходом дифференциального усилителя и соединен с первым выходом второго генератора тока, а эмиттер — с первым выводом первого резистора, второй регулирующий транзистор, второй и третий резисторы, третий генератор тока, о т" л и ч а ю шийся тем, что, с целью повышения точности коэффициента передачи, в него введены дополнительный дифференциальный каскад на третьем и четвертом транзисторах и дополнительный источник питания, при этом второй транзистор выполнен двухколлекторным, аструктура первого и второго регулирующих транзисторов, третьего и четвертого транзисторов противоположна структуре первого и второго транзисторов, причем эмиттеры третьего и четвертого транзисторов объединены и через третий генератор тока соединены с одной шиной дополнительного источника питания,. коллекторы — с соответствующими коллекторами второго транзистора и с базами соответственно второго и I первого регулирующих транзисторов, эмиттеров второго регулирующего транзистора соединен с базой третьего транзистора и через второй резистор— с одной шиной второго источника питания, к которой подключен второй вывод первого резистора, а коллектор второго регулирующего транзистора соединен с базой первого транзистора и че- рез третий резистор — с общей шиной, при этом база четвертого транзистора соединена с эмиттером первого регулирующего транзистора, база второго тран зистора — с источником входного напряжения, а второй вывод второго генератора тока — с одной шиной первого источника питания, причем другие шины всех источников питания подключены к общей шине.

1107283

Изобретение относится к промьпвленной э.пектронике и может использоваться -в управляемых источниках эталонных сигналов в качестве преобразователя напряжения в ток. 5

Известен преобразователь напряжения в ток, содержащий первый и второй входные транзисторы, эмиттеры которых соединены с объединенными эмиттерами транзисторов соответственно 10 первого и второго отражателей тока, входы которых соединены между собой через нормирующее сопротивление, а также первый и второй генераторы тока, включенные между шиной источника пита 15 яия и базами соответственно первого и второго выходных транзисторов, эмиттеры которых подключены к соответствующим выводам нормирующего сопротивления, а базы - к выходам соот- 20 ветственно первого и второго отража= телей тока C13 °

Однако данного преобразователя напряжения в ток недостаточна точность коэффициента передачи, обусловленная 25 погрешностями генераторов тока, Наиболее близким к изобретению по технической сущности является дифференциальный усилитель, содержащий входной дифференциальный каскад яа ЗО первом и втором транзисторах .одной структуры, объединенные эмиттеры кото-, рых через первый генератор тока соединены с одной шиной первого источника питания, коллектор первого транзистора — с одной шиной второго источника питания, первый регулирующий транзистор, коллектор которого явля- ется выходом дифференциального усилителя и соединен с первым выводом второго генератора тока, а эмиттер— с первым выводом rrepsoro резистора, второй регулирующий транзистор, второй и третий резисторы, третий генератор тока 423, 45

Однако в известном устройстве не1 остаточная точность коэффициента передачи обусловлеяа погрешностями второго генератора, тока и первого источника питания.

Цель изобретения — повышение точности коэффициента передачи.

Поставленная цель достигается тем, что в дифференциальный усилитель, содержащий входной дифференциальный каскад на первом и втором транзисторах одной структуры, объединенные эмиттеры которых через первый генератор тока соединены с одной шиной первого источника питания, коллектор первого транзистора — с одной шиной второго источника питания, первый регулирующий транзистор, коллектор которого является выходом дифференциального усилителя и соединен с первым выходом второго генератора тока, а эмиттер с первым выходом первого резистора, второй: регулирующий транзистор, второй и третий резисторы, третий генератор тока, введены дополнительный дифференциальный каскад на третьем и четвертом транзисторах и дополнительный источник питания, при этом второй транзистор выполнен двухколлекторным, а структура первого и второго регупирующих транзисторов, третьего и четвертого транзисторов противоположна структуре первого и второго транзисторов, причем эмиттеры третьего и четвертого транзисторов объединены и через третий генератор тока соединены с одной шиной дополнительного источника питания, коллекторы — с соответствующими коллекторами второго транзистора и с базами соответственно второго и первого регулирующих транзисторов, эмиттер второго регулирующего транзистора соединен с базой третьего транзистора и через второй резистор — с одной шиной второго источника питания, к которой подключен второй вывод первого резистора, а коллектор второго регулирующего транзистора соединен с базой первого транзистора и через третий резистор — с общей шиной, при этом база четвертого транзистора соеI динена с эмиттером первого регулирующего транзистора, база второго транзистора — с источникам входного напряжения, а второй вывод второго генератора тока — с одной шиной первого источника питания, причем другие шины всех источников питания подключены к общей шине.

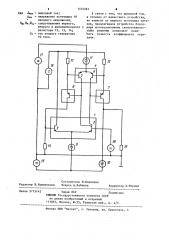

На чертеже представлена принципиальная электрическая схема дифференциального усилителя.

Дифференицальный усилитель содер" жит входной дифференциальный каскад 1 на первом и втором транзисторах 2 и 3, дополнительяый дифференциальный каскад 4 на третьем и четвертом транзисторах.5 и 6, первый и второй регулирующие транзисторы 7 и 8, первый, второй и третий генераторы 9-11 тока, 1107283.5 дифференциальный усилитель работает следующим образом.

В одной из схем реализации величина тока первого генератора 9 тока в два раза больше величины тока третье го генератора 11 тока, величина напряжения второго источника 16 питания меньше величины напряжения дополнительного источника 17 питания. В качестве двухколлекторного второго транзистора 3 входного дифференциального каскада 1 используе гся транзистор, коллекторные области которого имеют одинаковые геометрические размеры. В ка.честве первого и второго регулирую- 20 щих транзисторов 7 и 8 используются составные транзисторы. орным током второго регулирующего транзистора 8 ° Напряжение на базе вт

25 рого регулирующего транзистора 8 меняется таким образом, чтобы выравнить укаэанные токи. В результате ток, протекающий через третий резистор 14, равен коллекторному току второго регулирующего транзистора 8.

Коллкторный ток второго регулирую.— щего транзистора 8 с учетом величин базовых токов транзисторов равен его эмиттерному току, а следовательно то ку, протекающему через второй резис35 тор 13. Падение напряжения на втором резисторе 13, вызванное протеканием тока, с учетом сделанного замечания о равенстве напряжений на базах третьего и четвертого транзисторов

40 5 и 6 дополнительного дифференциального каскада 4, равно падению напряжения на первом резисторе 12. В ре- . зультате, величина тока, протекающего через первый резистор 12, про45 порциональна току, протекающему через второй резистор 13. Коллекторный ток первого регулирующего транзистора 7, равный току, протекающему через первый резистор 12, суммирует50 ся на нагрузке 19 с током второго генератора 10 тока.

Величина выходного тока, протекаюЫ его через нагрузку 19, определяешься

55 соотношением

3ьы в

Рщ

Рд 1 „ первый, второй и третий резисторы

12-14, первый второй и дополнительный источники 15- 17 питания, источник 18 входного напряжения, нагрузка 19.

В целях упрощения пренебрегаем величинами базовых токов транзисторов в силу их малости. Так как токи, протекающие через третий и четвертый транзисторы и 6 дополнительного дифференциального каскада 4 равны коллекторным токам двухколлекторного второго транзистора 3 входного диф. ференциального каскада 1, а коллектор ные токи второго транзистора 3 в силу одинаковости геометрических размеров его коллекторных областей равны друг другу, то токи, протекающие через третий и четвертый транзистор

5 и 6 дополнительного дифференциального каскада 4, равны друг другу, а следовательно напряжения на базах третьего и четвертого транзисторов

5 и 6 также равны друг другу. Ввиду того, что эмиттерный ток второго транзистора 3 равен сумме коллекторных токов второго транзистора 3, а сумма упомянутых коллекторных токов равна сумме эмитттерных токов третьего и четвертого транзисторов 5 и 6, которая, в свою очередь, равна току. третьего генератора 11 тока, то эмиттерный ток второго транзистора 3 также равен току третьего генератора ff тока. Учитывая вышеизложенное и то, что ток первого генератора 9 тока, подключенного к эмиттерам первого и второго транзисторов 2 и 3 в два раза больше тока третьего генератора

11 тока, приходим к выводу о равенстве эмиттевных токов первого и второго транзисторов 2 и 3. Так как эмиттерные токи первого и второго тран.зисторов 2 и 3 входного дифференциаль,ного каскада 1 равны друг другу, то напряжения на базах упомянутых транзисторов также равны друг другу.

Следовательно напряжение, прикладываемое к третьему резистору 14, равно напряжению источника 18 входного напряжения. В итоге, величина тока, протекающего через третий резистор 14, прямо пропорциональна величине напряжения источника 18 входного напря" жения и обратно пропорциональна сопротивлению третьего резистора 14, Второй регулирующий транзистор 8 включен в контур отрицательной обратной связи входного дифференциального каскада 1. Ток, протекающий через третий резистор 14, суммируется на базе первого транзистора 2 с коллект о1107283

Составитель И.Водяхина

Редактор H.Ïóøíåíêîâà Техред А.Бабинец Корректор А.Ференц

Заказ 5775/42

Тираж 862 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул, Проектная, 4 выходной ток, напряжение источника 18 входного напряжения, сопротивления первого, второго и дополнительного резистора 12, 13, 14; ток второго генератора

10 тока.

В связи с тем, ло выхолной ток, в отличие пт известного устройства не зависит от первого источника питания предлагаемое устройство благо5 даря использованному схемотехническому решению позволяет повысить точность коэффициента пере1 дачие