Устройство синхронизации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО СИНХРОНИЗАЦИИ, содержащее формирователь нулевых пересечений , выход которого подключен к установочному входу первого делителя частоты на два, к счетному входу которого подключен выход формирователя сигнала коррекции, а выход первого делителя частоты на два через блок фазовой автоподстройки частоты (ФАПЧ) подключен к входу формирователя синхросигнала, о т л и ч а rant е е с я тем, что, с целью повьшения точности синхронизации при дрейфе частоты следования сигнала, введены последовательно соединенные делитель частоты на п/2 (где п/2 « 1,2,3,..., п/2), второй делитель частоты на два и элемент И, выход ко торого подключен к входу формирователя сигнала коррекции, а к второму входу элемента И подключен выход делителя частоты на п/2, к установочному входу которого, а также к (Л установочному входу второго делитес ля частоты на два подключен выход формирователя нулевых пересечений, а к счетному входу делителя частоты на 1Л /2 подключен дополнительный выход блока ФАПЧ.

СОЮЗ СОВЕТСКИХ

РЕСПУБЛИН

acro Н 04 L 7 02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3521358/18-09 (22) 09. 12. 83 (46) 07.08.84. Бюл. Ф 29 (72) В.О. Вяземский и С.Н. Данилин (71) Ленинградский ордена Ленина электротехнический институт им. В.И. Ульянова (Ленина) и Муромский филиал Владимирского политехнического института (53) 621. 394. 662(088. 8) (56) 1. Авторское свидетельство СССР

11 457183, кл. Н 04 L 7/02, 1982.

2. Авторское свидетельство СССР

Ф 790356, кл. Н 04 Ь 7/02, 1978 (прототип). (54)(57) УСТРОЙСТВО СИНХРОНИЗАЦИИ, содержащее формирователь нулевых пересечений, выход которого подключен к установочному входу первого делителя частоты на два, к счетному входу которого подключен выход формирователя сигнала коррекции, а выход первого делителя частоты на два через блок фазовой автоподстройки частоты (ФАПЧ) подключен к входу формирователя синхросигнала, о т л и ч а ющ е е,с я тем, что, с целью повыщения точности синхронизации при дрейфе частоты следования сигнала, введены последовательно соединенные делитель частоты на и/2 (где n/2 =

1,2,3,..., n/2), второй делитель частоты на два и элемент И, выход ко» торого подключен к входу формирователя сигнала коррекции, а к второму входу элемента И подключен выход делителя частоты íà n/2, к установочному входу которого, а также к установочному входу второго делителя частоты на два подключен выход формирователя нулевых пересечений, а к счетному входу делителя частоты на б /2 подключен дополнительный выход блока ФАПЧ.

1107

Изобретение. предназначено для использования в технике связи, а так« же в системах цифровой магнитной записи.

Известен формирователь опорной части иэ случайной последовательности биимпульсных посылок, содержащий двухполупериодный выпрямитель . и резонансный контур, причем к входу двухполупериодного выпрямителя под- 10 ключен блок вычитания, на первый вход которого подана последовательность биимпульсных посылок непосредственно, а на второй через линию задержки, при этом между двухпопу- !5 периодным выпрямителем и резонансным контуром включен блок временной селекции (Ц .

Однако устройство обладает низкой помехоустойчивостью. 20

Наиболее близким к предлагаемому является устройство синхронизации, содержащее формирователь нулевых пересечений, выход которого подключен к установочному входу первого дели- 25 теля частоты на два, к счетному входу которого подключен выход формирователя сигнала коррекции, а выход первого делителя частоты на два через блок ФАПЧ подключен к входу фор" 3т! мирователя синхросигнала, а также последовательно соединенные ключ, генератор пилообразного напряжения и пороговый блок, выход которого подключен к входу формирователя сигнала З

35 коррекции, а к входу ключа подсоединен выход формирователя нулевых пересечений Г21 °

Однако известное устройство синхронизации обладает низкой точностью 4О синхронизации при дрейфе частоты следования синхросигнала.

Цель изобретения — повьппение точности синхронизации при дрейфе часто" ты следования сигнала.

Для достижения поставленной цели в устройство синхронизации, содержащее формирователь нулевых пересечений, выход которого подключен к установочному входу первого делителя 50 частоты на два, к счетному входу которого подключен выход формирователя сигнала коррекции, а выход первого делителя частоты на два через блок (ФАПЧ)подключен к входу формирова- 55 теля синхросигнала, введены последовательно соединенные делитель частоты на n/2 (где п/2 = 1, 2,3,..., 314 2

n/2), второй делитель частоты на два и элемент И, выход которого подключен к входу формирователя сигнала коррекции, а к второму входу элемента И подключен выход делителя частоты n/2, к установочному входу второго делителя частоты на два подклю— чен выход форьирователя нулевых пересечений, а к счетному входу делителя частоты на и/2 подключен дополнительный выход -блока ФАПЧ.

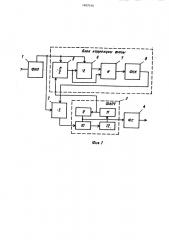

На фиг. 1 представлена структурная электрическая схема устройства синхронизации, на фиг. 2 — временные диаграммы, поясняющие его работу.

Устройство синхронизации содержит формирователь 1 нулевых пересечений, делитель 2 частоты на два, блок 3

ФАПЧ, формирователь 4 синхросигнала, делитель 5 частоты на g/2, второй делитель 6 частоть на два, элемент

И 7, формирователь 8 сигнала коррекции, блок 3 ФАПЧ содержит делитель

9 частоты на два фазовый детектор 10, генератор 11, управляемый напряжением, фильтр 12 °

Устройство синхронизации работает следующим образом. !

Фаэоманипулированный сигнал (фиг.

23) поступает на вход формирователя

1 нулевых пересечений, выходные импульсы которого (фиг. ?5) воздействуют на счетный вход первого делителя

2 частоты на два и установочные входы делителя 5 частоты на h/2, и второго делителя 6 частоты на два. На счетный вход делителя 5 частоты на два поступает с дополнительного выхода блока 3 ФАПЧ сигнал частотной в h раз превышающий частоту импульсов, синхронизации. Сигналы делителя 5 частоты на т /2 (фиг. ?г) и второго делителя 6 частоты на два (фиг. 24.) объединяются элементом И 7.

Полджительньтй период на выходе элемента И 7, вызывающий появление в формирователе 8 сигнала коррекции (фиг. >) возникает при величине паузы между смежными импульсами формирователя 1 нулевых пересечений не менее 0,75/f (где — среднее значение частоты следования информационных посылок).

Поскольку это условие выполняется для сигналов, соответствующих двоичному нулю, и не выполняется для двоичных "единиц", импульсы коррекции появляются лишь при поступле1107314, нии на вход устройства "нулевых" сигналов.

При принятом в блоке коррекции фазы способе детектирования сигнала ("логическое" детектирование) двоичным нулем считается сигнал, интервал меж-; ду смежными точками пересечения которого с нулевой линией при отсутствии искажений равен точно 1/7

За двоичную "единицу" принимаются два примыкающих друг к другу интервала, каждый из которых равен при отсутствии искажений 0,5/ Å . При наличии временных искажений за порог различия "нуля" от "единицы" принимается уровень 0,75/У, как одинаково удаленный от средних длительностей !!нулей!! и !!единиц! 1

В результате воздействия импульсов коррекции на установочный вход первого делителя 2 частоты на два, каждый неискаженный "нуль" устанавливает фиксированную фазу делителя, устраняя таким обарзом "скачки" фазы, 25 возникающие в результате воздействия помех на делитель.

Каждая информационная "единица" вызывает появление двух сигналов нулевых пересечений на выходе формирователя 1 нулевых пересечений, разделенных интервалами 0,5/f так, что цель коррекции в этом случае не срабатывает, и на .выходе первого делителя 2 частоты на два образуется один п риод частоты f . При информаци- 35 онном "нуле" сброс в исходное состояние названного делителя происходит по сигналу коррекции. Таким образом, на вход блока ФАПЧ поступают сигналы с частотой У и фиксированной фазой 40 положительных перепадов вне зависимости от вида входной информации.

При воздействии помех (фиг. 2a) формирователь 1 нулевых пересечений выдает импульсы, как при пересечении 45 информационным сигналом нулевой линии, так и в момент появления импульсной помехи (фиг. 2Ь). Импульсы, порожденные помехами (импульсы 13-15, фиг. 2ь), осуществляют дополнительные сбросы делителя 5 частоты на й/2 и второго делителя 6 частоты на два в "нуль" (фиг. 2 г, ) и вызывают появление лишних перепадов в выходном напряжении первого делителя

2 частоты на два (импульсы 16-18 фиг.

2а). Сигналы, сформированные из положительных перепадов (импульсы 1921 фиг. 2В), диаграмма не формируется в устройстве и приведена с целью пояснить по какому из фронтов первого делителя 2 частоты на два производится подстройка по фазе), воздействуют на блок ФАПЧ как помехи, ксторые приведут только к отклонению фазы выходного сигнала блока ФАПЧ (фиг. 2u) от начальной, но не изменят числа синхроимпульсов с выхода формирователя 4 синхросигнала (фиг. 2 ). Последнее объясняется тем, что сигнал коррекции от первого же не пораженного информационного "нуля"(фиг. 2е) поступает на установочный вход первого делителя 2 частоты на два и устанавливает (или подтверждает) правильное значение его фазы по отношению к фазе информационных символов.

Цепь коррекции вырабатывает сигнал коррекции строго по истечении

0,75 периода средней частоты следования и не зависит от дрейфа. параметров элементов его составляющих и изменения средней частоты следования информации. Точность поддержания порога различейия определяется соотношением

Предлагаемое устройство синхронизации характеризуется однозначностью начальной фазы синхросигнала после вхождения устройства в синхрониэм, неизменностью числа синхросигналов между кодами групповой синхронизации, а так же исключением потерь информации, обусловленных спонтанными скачками фазы в процессе приема сигнала.

1107314

11073 14 н

„д

Ф

„0

1Р 78

18 РО

Фиг. 2

Составитель Г. Лерантович

Техред А.Бабинец Корректор M.làðoøè

Редактор Е. Лушникова

Тираж 635 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5778/44

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4