Демодулятор дискретных сигналов с фазоразностной модуляцией

Иллюстрации

Показать всеРеферат

ДЕМОДУЛЯТОР ДИСКРЕТНЫХ СИГНАЛОВ С ФАЗОРАЗНОСТНОЙ МОДУЛЯЦИЕЙ , содержащий два основных сумматора , выходы которых подключены к входам решающего блока, а в каядой ветви разнесения четьфе перемножителя , причем входы первого и второго, а также третьего и четвертого перемножителей соединены вместе , дополнительный сумматор, генератор линейно изменяющегося напряжения , выход которого подключен к управляющим входам двух компараторов , выход одного из которых подключен к управляющим входам первого и третьего перемножителей,а выход другого - к управляющим входам второго и четвертого перемножителей , выходы первого и четвертого перемножителей через первьвТ интегратор , а выходы второго и третьего перемножителей через второй интегратор подключены к соответствующим входам первого и второго основных сумматоров, отличающийся тем, что, с целью расширения выходного динамического диапазона, введены два квадратора и вычислительный блок, при этом входы первого и третьего перемножителей через квадраторы соединены с входами дополнительного сумматора, выход которого подключен к входу вычислительного блока, выход которого соединен с соответствующим входом генератора линейно изменяющегося напряжения .

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН ()9) (И) Р1д)) Н 04 1. 27/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCK0IVIV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3501981/18-09 (22) 18. 10.82 (46) 07.08.84. Бюл. У 29 (72) В.М. Вишняков и С.Т. И)ртаев (53) 621.394.62 (088,8) (56) 1. Заездный А.М., и др. Аппаратура передачи дискретной информации МС-5. М., "Связь", 1970, с. 59-69.

2. Авторское свидетельство СССР

Р 502518, кл. Н 04 L 27/22, 1974 (прототип) . (54) (57) ДЕМОДУЛЯТОР ДИСКРЕТНЫХ

СИГНАЛОВ С ФАЗОРАЗНОСТНОЙ МОДУЛЯЦИЕЙ, содержащий два основных сумматора, выходы которых подключены к входам решающего блока, а в каждой ветви разнесения четыре перемножителя, причем входы первого и второго, а также третьего и четвертого перемножителей соединены вместе, дополнительный сумматор, генератор линейно изменяющегося напряжения, выход которого подключен к управляющим входам двух компараTopoB выход одного из KQTopblx подключен к управляющим входам первого и третьего перемножителей,а выход другого - к управляющим входам второго и четвертого перемножителей, выходы первого и четвертого перемножителей через первый интегратор, а выходы второго и третьего перемножителей через второй интегратор подключены к соответствующим входам первого и второго основных сумматоров, отличающийся тем, что, с целью расширения выходного динамического диапазона, введены два квадратора и вычислительный блок, при этом входы первого и третьего перемножителей через квадраторы соединены с входами дополнительного сумматора, выход которого подключен к входу вычислительного блока, выход которого соединен с соответствующим входом генератора линейно изменяющегося напряжения .

1107325

Изобретение относится к связи и может найти применение в системах передачи информации.

Известен демодулятор дискретных сигналов с фазоразностной модуляцие 1, содержащий входные ключевые переключатели, интеграторы, сумматоры, компараторы, генера op линейно изменяющегося напряжения, сумматоры аналоговых величин и решающий блок 511.

Недостаток демодулятора заключается в узком выходном динамическом диапазоне.

Наиболее близким к предлагаемому является демодулятор дискретных сигналов с фазоразностной модуляцией, содержащий два основных сумматора, выходы которых подключены к входам решающего блока, а в каждой ветви разнесения четыре перемножителя, причем входы первого и второго, а также третьего и четвертого перемножителей соединены вместе, дополнительный

25 сумматор, генератор линейно изменяющегося напряжения, выход которого подключен к управляющим входам двух компараторов, выход одного из которых подключен к управляющим входам первого и третьего перемножителей, а выход другого — к управляющим входам второго и четвертого перемножителей, выходы первого и четвертого перемножителей через первый интегратор, а выходы второго и третьего перемножителей через второй интегратор подключены к соответствующим входам первого и второго основных сумматоров 523.

Недостаток известного демодулято40 ра заключается в узком выходном динамическом диапазоне.

Цель изобретения — расширение выходного динамического диапазона.

Для достижения поставленной цели

45 в демодулятор дискретных сигналов с фазоразностной модуляцией, содержащий два основных сумматора, выходы которых подключены к входам решающего блока, а в каждой ветви разнесения четыре перемножителя, причем входы пер— вого и второго, а также третьего и четвертого перемножителей соединены вместе, дополнительный сумматор, генератор линейно изменяющегося напряжения, выход которого подключен к управляющим входам двух компараторов, выход одного из которых подключен к управляющим входам первого и третьего перемножителей, а выход другого — к управляющим входам второго и четвертого перемножителей, выходы первого и четвертого перемножителей через первый интегратор, а выходы второго и третьего перемножителей через второй интегратор подключены к соответствую= щим входам первого и второго основных сумматоров, введены два квадратора и вычислительный блок, при этом входы первого и третьего перемножнтелей через квадраторы соединены с входами дополнительного сумматора, выход которого подключен к входу вычислительного блока, выход которого соединен с соответствующим входом генератора линейно изменяющегося напряжения.

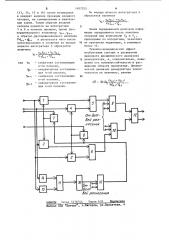

На чертеже изображена структур-. ная электрическая схема демодулятора.

Демодулятор дискретных сигналов с фазоразностной модуляцией содержит первый 1., второй 2, третий 3, четвертый 4 перемножители, первый 5 и второй 6 интеграторы, компараторы 7 и 8, первый 9 и второй 10 основные сумматоры, дополнительный сумматор 11, решающий блок 12, генератор 13 линейно изменяющегося напряжения, квадраторы 14 и 15, вычислительный блок 16.

Устройство работает следующим образом.

Сигналы из канальных фильтров приемника, содержащие синфазные и квадратурные составляющие п-oé посылки, поступают на ключевые перемножители 1-4, а синфазные и квадратурные составляющие (п-1)-ой посылки — на компараторы 7 и 8, которые сравнивают входные сигналы с линейно изменяющимся напряжением генератора 13 линейно изменяющегося напряжения и формируют временные интервалы, в течение которых входные сигналы подаются на интеграторы 5и 6.

Генератор линейно изменяющегося напряжения 13 формирует линейно изменяющееся напряжение, скорость изменения которого прямо пропорциональна величине модуля вектора посылки, которая формируется на выходе вычислительного блока 16.

Величина модуля вектора посылки входного сигнала формируется в блоках

1107325 где Хи ию-Ф

3 (l1 14, 15 и 16) путем возведения в квадрат величин проекции входного сигнала, их суммирования и извлечения корня. Таким образом входные сигналы подаются на интеграторы

С и 6 в течение времени, прямо пропорционального значениям Х„ „ u„ „ ю1-4(и0 4 и обратно пропорционального величине

ЧХ „ Я, в результате чего после интегрирования и сложения на выходе первого интегратора 5 образуется величина синфазная составляющая и-ой посылки, квадратурная составляющая п-ой посылки, си нфа э на я с ос та вляющая и-ой посылки, квадратурная составляющая и-ой посылки.

На выходе второго интегратора 6 образуется величина

ХиЪ- (+ и и- <

Знаки передаваемой двоичной информации определяются после линейных операций над величинами V и V

2 приводимых по алгоритмам, зависящих

10 от кратности модуляции, в решающем блоке 12.

Технико-экономический эффект изобретения состоит в расширении выходного динамического диапазона

15 демодулятора, а, следовательно, повышении его помехоустойчивости и расширении области применения . Динамический диапазон демодулятора увеличивается на величину, равную

БНКИПЦ Заказ 5778!44 Тираж 635 Подписное

Филиал ППП ЯПатент, г.ужгород, ул.Проектная, 4