Формирователь сигналов сброса для блоков памяти

Иллюстрации

Показать всеРеферат

.ФОРМИРОВАТЕЛЬ СИГНАЛОВ СБРОСА ДЛЯ БЛОКОВ ПАМЯТИ, содержащий ограничительные и накопительные элементы , причем первый вывод первого ограничительного элемента соединен с первой шиной питания, а второй: вывод - с первым выводом первого накопительного элемента, второй вывод которого соединен с шиной нулевого потенциала, первый вывод второго ограничительного элемента соединен с второй шиной питания, а второй 1ЧЫВОД - с первым выводом второго накопительного элемента, второй вывод которого соединен с шиной нулевого потенциала, о т л и. ч а ю щ и йс я тем, что, с целью расширения области применения формирователя за счет обеспечения формирования сигналов сброса в различных режимах работы блоков памяти и при различных напряжениях питания, в него введены третий, четвертый и пятый ограничительные элементы, элементы НЕ, элементы НЕРАВНОЗНАЧНОСТЬ и элементы И-НЕ, причем вход элемента НЕРАВНОЗНАЧНОСТЬ соединен с выходом первого элемента НЕ, вход которого соединен с вторьм выводом первого ограничительного элемента и первым выводом третьего ограничительного элемента, второй вывод которого соединен с шиной нулевого потенциала, второй вход элемента НЕРАВНОЗНАЧНОСТЬ и первьш вывод пятого ограничительного элемента являются первым входом формирователя, второй вывод пятого (Л ограничительного элемента соединен с третьей шиной питания, выход элес мента НЕРАВНОЗНАЧНОСТЬ и первый вход элемента И-НЕ являются первым выходом устройства, второй вход элемента И-НЕ является вторым входом устройства , а третий вход соединен с вторым выводом второго ограничиЭ6 тельного элемента и первым выводом :л четвертого ограничительного элемента , второй вывод которого соединен с шиной нулевого потенциала, выход элемента- И-НЕ и . вход второго элемента НЕ являются вторым выходом устройства третьим выходом которого является выход второго элемента НЕ.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

09) 01) а 11 C 7/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3595565/24-06 (22) 26.05.83 (46) 15.08 .84 . Бюп . № 30 (72) А.Г.Забуранный, Н.Р.Журавский, В.Н.Загребной и В.Я.Мусиенко (71) Киевский ордена Трудового Красного Знамени завод электронньх вычислительных и управляющих машин (53) 681. 327 (088. 8) (5á) 1. Авторское свидетельство СССР № 773722, кл. 8 11 С 7/00, 1979.

2, "Радио", 1980, № 1, с. 61. (54)(57),ФОРМИРОВАТЕЛЬ СИГНАЛОВ

СБРОСА ДЛЯ БЛОКОВ ПАМЯТИ, содержащий ограничительные и накопительные элементы, причем первый вывод первого ограничительного элемента соединен с первой шиной питания, а второй; вывод — с первым выводом первого накопительного элемента, второй вывод которого соединен с шиной нулевого потенциала, первый вывод второго ограничительного элемента соединен с второй шиной питания, а второй

«ывод — с первым выводом второго накопительного элемента, второй вывод которого соединен с шиной нуле" вого потенциала, о т л и. ч а ю щ и йс я тем, что, с целью расширения области применения формирователя за счет обеспечения формирования сигналов сброса в различных режимах работы блоков памяти и при различных напряжениях питания, в него введены третий, четвертый и пятый ограничительные элементы, элементы HE элементы НЕРАВНОЗНАЧНОСТЬ и элементы И-НЕ, причем вход элемента

НЕРАВНОЗНАЧНОСТЬ соединен с выходом первого элемента НЕ, вход которого соединен с вторым выводом первого ограничительного элемента и первым выводом третьего ограничительного элемента, второй вывод которого соединен с шиной нулевого потенциала, второй вход элемента НЕРАВНОЗНАЧНОСТЬ и первый вывод пятого ограничительного элемента являются первым входом формирователя, второй вывод пятого ограничительного элемента соединен с третьей шиной питания, выход эле" мента НЕРАВНОЗНАЧНОСТЬ и первый вход элемента И-НЕ являются первым выходом устройства, второй вход элемента

И-НЕ является вторым входом устройства, а третий вход соединен с вторым выводом второго ограничительного элемента и первым выводом четвертого ограничительного элемента, второй вывод которого соединен с шиной нулевого потенциала, выход элемента И-НЕ и.вход второго элемен. та НЕ являются вторым выходом устройства, третьим выходом которого является выход второго элемента НЕ.

1 1 108504. 3

Изобретение относится к вычисли. тельной технике и может быть использовано в запоминающих устройствах, s которых требуется автоматическая установка в исходное состояние в

5 момент включения источника питания.

° Известен формирователь сигналов. в котором для автоматической установки блока в исходное состояние используется разделительный элемент, 10 подключенный к источнику питания и синхровходам триггеров, информацион ные входы которых подключены к шине нулевого потенциала, а в качестве

paspesIHTelIbHor элемента использует- 15 ся резистор Е11.

Недостатками этого устройства являются ограниченные функциональные возможности, обусловленные отсутствием организации отладочных режимов 2р и невозможностью формирования сигналов сброса по включению источника питания с напряжением, превышающим напряжение питания микросхем, а также недостаточно высокая надежность g5 функЦионирования устройства.

Наиболее близким техническим решением к изобретению является формирователь сигналов установки в исходнОе состояние при включении пита-,з0 ния устройства задержки импульсов, содержащий резистор, конденсатор, одновибратор, шину питания и шину нулевого потенциала, причем первый вывод резистора соединен с шиной

35 питания, а второй вывод - с входом одновибратора и первым выводом конденсатора, второй вывод которого соединен с шиной нулевого потенциала t2 1„

Однако этот формирователь не поз- 46 воляет формировать. сигналы сброса по включению источника питания с напряжением, превышающим напряжение питания микросхемы, а также организовывать отладочные режимы, 4 что ограничивает его область применения.

55

Цель изобретения - расширение области применения формирователя за счет обеспечения формирования сигналов сброса в различных режимах работы блоков памяти и при различных напряжениях питания, Поставленная цель достигается тем, что в формирователь сигналов сброса для блоков памяти, содержащий ограничительные и накопительные элементы, причем первый вывод первого ограничительного элемента сое- динен с первой шиной питания, а второй вывод — с первым выводом перво-! го накопительного элемента, второй вывод которого соединен с шиной нулевого потенциала, первый вывод второго ограничительного элемента соединен со второй шиной питания, а второй вывод — с первым выводом второго накопительного элемента, второй вывод которого соединен с шиной нулевого потенциала, введены третий, четвертый и пятый ограничительные элементы, элементы НЕ, элементы НЕРАВНОЗНАЧНОСТЬ и элементы И-НЕ, причем вход элемента НЕРАВНОЗНАЧНОСТЬ соединен с выходом первого элемента НЕ, вход которого соединен с вторым выводом первого ограничительного элемента и первым выводом третьего ограничительного элемента, второй вывод которого соединен с шиной нулевого потенциала, второй. вход элемента НЕРАВНОЗНАЧНОСТЬ и первый вывод пятого ограничительного элемента являются первым входом формирователя, второй вывод пятого ограничительного элемента соединен с третьей шиной питания, выход элемента НЕРАВНОЗНАЧНОСТЬ и первый вход элемента И-НЕ являются первым выходом устройства» второй вход элемента И-HE является вторым входом устроиства, а третий вход соединен с вторым выводом второго ограничительного элемента и первым выводом четвертого ограничительного элемента, второй вывод которorо соединен с шиной нулевого потенциала, выход элемента И-НЕ и вход второго элемента НЕ являются вторым выходом устройства, третьим выходом которого является выход второго элемента НЕ.

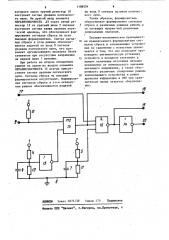

На чертеже представлена принципиальная схема формирователя сигналов сброса для блоков памяти.

Формирователь сигналов сброса содержит первую 1, вторую 2 и третью

3 шины питания, первый 4 и второй 5 ограничительные элементы, например резисторы, первый 6 и второй 7 накопительные элементы, например конденсаторы, шину 8 нулевого потенциа- ла, первый вход 9, третий 10, четвертый 11 и пятый 12 ограничительные элементы, например резисторы, первый 13 и второй 14 элементы НЕ, эле1 108504 4 вход элемента НЕРАВНОЗНАЧНОСТЬ 15 и на его выходе формируется сигнал уровнем логической единицы, что соответствует отсутствию сигнала сброса на первом выходе !8. Сигналы сброса также снимаются с второго

19 и третьего 20 выходов. Таким образом обеспечивается автоматии- ческое формирование сигналов сброса ! б в момент включения источника питания.

При переходе в режим резервного хранения информации, например в динамическом ОЗУ, питающее напряжение с второй шины 2 питания снимается и через четвертый резистор 11 делителя, состоящего иэ второго 5 и четвертого 11 резистороз, на

0 вход элемента И-НЕ 16 подается сиг2п нал уровнем логического нуля, обеса печивая тем самым формирование

ТЕ сигналов сброса на втором 19 и . и- третьем 20 выходах, чем обеспечивается -сохранность хранимой s дмма2 25 мическом ОЗУ инфОрмации;

После вьдачи напряжения питания на вторую шину 2 питания сигналы сброса с втсфцго-:19- и.третьего. 20 выходов снимаш ся, что обеспечивает переход форм!рователя или системы о- в режим нормального функциониррвания.

3 мент HEPABH03HAЧНОСТЬ 15, элемент

И-НЕ 16, второй вход 17, первый 18, второй 19 и третий 20 выходы.

Формирователь работает следующим образом.

При включении источника питания питающие напряжения подаются на вто рую 2 и третью 3 шины питания, а также на интегральные микросхемы, п тание микросхем (не показаны) осуществляется от третьей шины 3 питания. На первую шину 1 питания напряжение подается после установки номинальных значений напряжений на второй 2 и третьей 3 шинах питания, .т.е. с некоторым запаздыванием. До подачи напряжения на первую шину 1 питания иа вход первого элемента НЕ

13 подается через третий резистор 1 сигнал уровнем логического нуля, а с выхода первого элемента НЕ 13 н первый вход элемента НЕРАЬНОЗНАЧНОС

15 — сигнал уровнем логической един цы. На второй вход элемента НЕРАВНО

ЗНАЧНОСТЬ 15 через пятый резистор,1 от третьей шины 3 питания подается сигнал уровнем логической единицы и на выходе .элемента НЕРАВНОЗНАЧНОСТЬ

15 формируется сигнал сброса уровнем логического нуля. Этот сигнал поступает на первый 18 выход формир вателя для установки необходимых це пей, например цепей регЕнерации информации в динамическом оперативном запоминающем устройстве, в ис35 ходное состояние, а также поступает на вход элемента И-НЕ 16, который формирует сигнал сброса уровнем логической единицы, поступающий на второй выход-19 формирователя. Вто- 4 . рой элемент НЕ 14 формирует сигнал сброса, поступающий на третий выход.

20 формирователя уровнем логического нуля. Последние два сигнала сброса устанавливают в исходное состояние 45 остальные цепи формирователя или системы, например, динамического оперативного запоминающего устройства (ОЗУ).

I

После подачи питающего напряжения на первую шину 1 питания с помощью делителя, состоящего из пер. вого 4 и третьего 10 резисторов, обеспечивается формирование сигнала на входе первого элемента НЕ 13. уров-55 нем логической единицы. С выхода первого элемента НЕ 13 сигнал уров- нем логического нуля поступает на

При подаче сигнала сброса уровнем логического нуля на вход 17 . формирователь формирует сигналы сброса на втором 19 и третьем 20 выходах.

Работа формирователя сигналов сброса обеспечивается в двух отладочных режимах: при отсутствии питания на первой шине 1 питания (например при отладке элементов блоков памяти, на которых реализован описанный формирователь сигналов.сброса,:на уивер" сальном технологическом оборудовании), при наличии питания на первой шине 1 питанйя (например пр@ отладice запоминающего устройства при постоянно включенном источнике питания).

При работе в первом отладочном режиме.на один из входов элемента

НЕРАВНОЗНАЧНОСТЬ 15 подается сигнал уровнем логической единицы с выхода первого элемента НЕ 13, на вход

1 108504

ВНИИПИ Заказ 5874/38 Тираж 575 Подписное

Филиал ППП "Патент", г.Ужгород, ул.Проектная, 4 которого через третий резистор 10 поступает сигнал уровнем логического нуля. На другой вход элемента

НЕРАВНОЗНАЧНОСТЬ ..45 через пятый резистор 12 от третьей шины 3 питания поступает сигнал также уровнем логиеской единицы, что обеспечивает формирование сигналов сброса на всех выходах формирователя. Снятие сигналов сброса в этом режиме обеспечивается лодачей на вход 9 сигнала уровнем логического нуля, что позволяет организовывать проверку блока элементов при отсутствии напряжения на первой шине 1 питания.

При работе во втором отладочном режиме на одном из входов элемента

НЕРАВНОЗНАЧНОСТЬ !5 всегда присутствует сигнал уровнем логического нуля. Сигналы сброса на выходах формирователя отсутствуют. Формирование сигналов сброса в .этом отладочном режиме обеспечивается подачей на вход 9 сигнала уровнем логического нуля.

Таким образом, формирователь обеспечивает формирование сигналов сброса в различных режимах работы и от питающих напряж ний различных номинальных значений.

Технико-экономическое преимущест<0 во предлагаемого формирователя сигналов сброса в запоминающих устройствах по сравнению с известным заключается в том, что оно позволяет производить автоматическую установку !

5 устройств в исходное состояние в момент включения источника питания независимо от номинального значения питающего напряжения, а также обеспечивать различные отладочные режимы

20 запоминающего устройства и режим хранения информации в ОЗУ при сравнительно малых затратах оборудования е 8