Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

АНАЛОГОВОЕ ЗАПОМИНМЩЕЕ УСТРОЙСТВО, содержащее компараторы с памятью, первые входы которых являются входом устройства, вторые входыI компараторов соединены с шиной управ ления , формирователь опорных напряжений , выходы которого соединены с третьими вхадами компараторов, усилитель , выход которого является выходом устройства, блок памяти, о тл и ч а ю щ е е с я тем,, что, с целью повышения точности устройства, в него введен сумматор, входа группы которого соединены с выходами компараторов , выход сумматора соединен с инвертирующим входом усилителя, меинвертирующий вход которого соединен с выходом блока памяти, первый вход памяти соединен с выходом усилителя , второй вход блока памяти является входом устройства, а третий вход блока памяти соединен с шиной управления, вход сумматора соединен с последним выходом формирователя опорных напряжений.

СОО3 СОВЕТСКИХ . CNNII5

РЕСПУБЛИК

0% 61) gyp,С 11 С 27/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

8 (21) 3508150/18-24 (22) 03.11.82 (46) 15.08.84.Бюл. Ф 30 (72) А.А.Данилов (71) Ордена Ленина институт проблем управления

1 (53) 681.327.66(088.8) (56) 1. Бахтиаров Г.Д. и др.Аналогоцифровые преобразователи. М., "Советское радио", 1980, с. 129.

2. Там же, с.130-131 (прототип). (54) (57) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО, содержащее компараторы с памятью, первые входы которых являются входом устройства, вторые входы компараторов соединены с шиной управления, формирователь опорных напряжений, выходы которого соединены с третьими входами компараторов, усилитель, выход которого является выходом устройства, блок памяти, о тл и ч а ю щ е е с я тем, что, с целью повышения точности устройства, в него введен сумматор,. входы группы которого соединены с выходами компараторов, выход сумматора соединен с инвертирующим входом усилителя, неинвертирующий вход которого соединен с выходом блока памяти, первый вход памяти соединен с выходом усилителя,второй вход блока памяти является входом устройства, а третий вход блока памяти соединен с шиной Я управления, вход сумматора соединен с последним выходом формирователя опорных напряжений.

09

1 1 1085

Изобретение относится к вычислительной технике, в частности к тгх1 нике аналоговых запоминающих устройств, и может быть использовано при построении аналого-цифровых пре- 5 обраэователей (АЦП).

Известно аналоговое запоминающее устройство, содержащее компаратор, цифро-аналоговый преобразователь, элементы И, счетчик и усилитель C1).

Недостатком устройства является сравнительно большое время выборки входного сигнала, обусловленное временем отслеживания входного сигнала через цепь отрицательной обратной 15 связи (ООС), содержащую компаратор напряжения, реверсивный счетчик и цифро-.аналоговый преобразователь (ЦАП). Кроме того, точность выборки в этих устройствах принципиально 20 ограничена шагом квантования (разрядностью) ЦАП.

Наиболее близким к предлагаемому по технической сущности является аналоговое запоминающее устройство, реа-25 лизованное на основе АЦП параллельного типа и содержащее компараторы, инвертирующие входы которых объединены и являются входом устройства, а неинвертирующие подключены соответ-50 ственно к выходам формирователя опор" ных напряжений, выходы компараторов через схемы стробирования подключены . к блоку памяти, в котором происходит запоминание выбранного значения входного сигнала в виде унитарного цифро.— вого кода. Состояние блока памяти считывается посредством кодирующей логики и далее поступает на ЦАП, на выходе которого уже образуется выбран- 0 ное значение входного сигнала в аналоговой форме -2I

Недостатком данного устройства является низкая точность, обусловленная, ограниченной точностью и разряднос" тью АЦП.

Целью изобретения является повыше,ние точности устройства.

Поставленная цель достигается тем, что в аналоговое запоминающее уст- 50 ройство, содержащее компараторы с памятью, первые входы которых являются входом устройства, вторые входы компараторов соединены с шиной управления,формирователь опорных напряжений 55 выходы которого соединены с третьими входами компараторов, усилитель, выход которого является выходом устройства, блок памяти, введен сумматор, входы группы которого соединены с выходами компарато;;ов, выход сумматора соединен с инвертирующим входом усилителя, неинвертирующий вход которого соединен с выходом блока памяти, первый вход блока памяти соединен с выходом усилителя, второй вход блока памяти является входом устройства, а третий вход блока памяти соединен с шиной управления, вход сумматора соединен с последним выходом формирователя опорных напряжений.

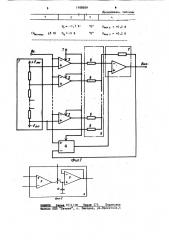

На фиг. 1 представлена функциональная схема предложенного устройства; на фиг. 2 — блок памяти, вариант.

Устройство содержит формирователь

1 опорных напряжений, усилитель 2, компараторы 3, блок 4 памяти, сумматор 5, резисторы б, шина 7 управления. Блок 4 памяти содержит повторитель 8 направления, ключ 9, накопительный элемент на конденсаторе 10, дифференциальный усилитель 11.

Устройство работает следующим. образом.

На шину 7 управления поступает цифровой управляющий сигнал, например логическая "единица", и устройство переходит в режим выборки входного сигнала. При этом компараторы 3 начинают сравнивать уровни сигналов на своих входах в соответствие с раз- решением, поступившим на их входы стробирования. Если, например, уровень входного .сигнала превышает уровень соответствующего бпорного напряжения то компаратор 3 формирует (или оставляет) на своем выходе стандартный логический уровень, близкий к потенциалу нуля, Так как входной сигнал поступает на первые входы сразу всех компараторов 3, то на их выходах формируется цифровой унитарный код, соответствующий равномерно квантованному в пределах шкалы входному сигналу.

В таблице показано соответствие кода входному и опорным напряжениям для N=4, где И вЂ” число разрядов.

Сформированный код в конечном счете соответствует определенному набору аналоговых сигналов на выходах компараторов 3, которые затем преобразуются в ток резисторами 6 сумматора 5 и поступают на инвертирующий вход усилителя 11, где происходит суммирование. Так как сумма токов

1108509

Аналоговый сигнал, соответствующий цифровому (ТТЛ) Состояние на выИгновенный уро- Опорное напрявень входного жение на входах компараторов напряжения ходах компараторов

Ъ»Ф

U „, -"+40в

U = +4,0 В

U»- +5 В

U - +1,7 В

»»1»

V, = +3 В в точке суммирования в идеальном случае должна быть равна нулю, то компенсирующий ток поступает через резистор обратной связи, при этом на, выходе устройства появляется напряжение, примерно соответствующее напряжению на входе резисторов 6. С увеличением числа компараторов N это .соответствие будет все более точным, но при N)10 устройство становится сложным, Для -.îãî, чтобы повысить точность без существенного усложнения схемы, в устройстве имеется блок 4 памяти, в задачу которого . входит полная отработка разности между входным и выходным напряженияЪ. ми и последующее запоминание этой разности в режиме хранения. Блок 4 памяти с точностью до собственного смещения нуля уравнивает эти напряже- >О ния за счет измерения напряжения на неинвертирующем входе усилителя 2 в силу того, что образуется контур (ООС1через вход блока 4, неинвертирующий вход усилителя 2,, выход устройства, к которому присоединен. один из входов блока 4. Таким образом,. компараторы 3 производят быструю, но "грубую" выборку входного сигнала не давая в то же время за счет своего высокого быстродействия перегружаться по входу блока 4 памяти, который, в свою очередь, производит точную подстройку уровня выходного напряжения посредством контура ООС.

Резистор 6„ присоединенный одним из выводов к минусовому выходу формиро вателя опорных напряжений 1, служит для создания постоянного отрицательного тока смещения в суммирующей точ- 40 ке усилителя 2, так как выходные напряжения компараторов 3 могут принимать только положительные значе.ния и соответствующие токи через остальные резисторы 6 будут положитель- 45

I ными. Введение отрицательного тока смещения позволяет также производить выборку биполярных входных сигналов.

Переход устройства в режим хранения происходит после поступления на шину

7 цифрового управляющего сигнала другого логического уровня, например логического »нуля».,При этом компараторы 3 запоминают сформированный код до следующей выборки, поддерживая соответствующие токи в цепи резисторов 6, а блок 4 памяти запоминает отслеженную им разность, поддерживая в режиме хранения соответствующий потенциал на неинвертирующем входе усилителя 2. Следовательно,, на выходе устройства в режиме хранения поддерживается выбранный уровень входного аналогового сигнала.

Предложенное устройство реализовано в виде макета с применением ин" тегральных компараторов типа 597CA?, интегрального операционного усилителя типа 154УДЗ и резистивного формирователя опорных напряжений. В качестве блока памяти использована интегральная микросхема, аналогичная микросхеме НА2420. При шкале входного сигнала + 5 В время выборки с точностью 0,02% не превышает 500 нс и ограничивается в основном временем установления выходного напряжения операционного усилителя 154УДЗ.

Технико-экономическая эффективность предложенного устройства определяет- . ся повышением точности выборки входного аналогового сигнала при сохранении малого времени выборки и значительном упрощении устройства, возможностью реализовать устройство на допустимой элементной базе, а также по интегральной технологии, относитель/ ной простотой устройства при высоких качественных показателях.

1 1088509

Ц,-1,7 В1 фиг.

3588835 3оеее 5874/58 ТврЩ 575 По88353Ре филиал IIIIII 1патент, г. уапц ород3 ул.Проектная,4 (Уьм t5 В) 0 }=-5 В б

Йродол7кеии4 табл ицй

"0" 0 8 х.З +0,2 В

"0" О„„= +0,2 В