Устройство для получения квадратичной зависимости

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПОЛУЧЕНИЯ КВАДРАТИЧНОЙ ЗАВИСИМОСТИ, содержащее первый и второй двоичные делители частоты, первую и вторую группы элементов И, первый и второй элементы ИЛИ, сумматор-вычитатель, формирователь импульсов, регистр, счетчик результата, разрядные выходы которого соединены соответственно с разрядными входами регистра, вход записи которого соединен с выходом формирователя импульсов, вход которого соединен с выходом первого двоичного делителя частоты и входом записи числа сумматора-вычитателя, разрядные ВЫХОДЫ которого соединены соответственно с первыми входами элементов И первой группы, вторые входы которых соединены соответственно с разрядными выходами первого двоичного делителя частоты, вход -которого соединен с входом.элемента НЕ, выход которого соединен с входом второго ДВОИЧНОГО делителя частоты, разрядные ВЫХОДЫ которого соединены соответственно с первыми входами элементов И второй группы, вторые входы которых соединены соответственно с разрядными выходами регистра, выходы элементов И первой и второй групп соединены соответственно с входами первого и второго элементов ИЛИ, выход второго элемента ИЖ является ВЫХОДОМ устройства, отличающееся тем, что, с целью расширения области применения путем получения возможности изменения параметров квадратичной зависимости, в него введены управляемый делитель частоты, блок памяти, первый и второй распределители импульсов, элемент И, первый ВХОД которого соединен с первым ВЫХОДОМ первого распределителя импульсов , второй ВЫХОД которого соединен с ВХОДОМ второго распределителя импульсов,первый выход которого соединен с входом записи счетчика результата, второй выход второго распределителя импульсов соединен с ВХОДОМ установки коэффициента деления управляемого делителя частоты, ВХОД которого соединен с выходом первого элемента ИЛИ, выход управляемого делителя частоты соединен со О счетным ВХОДОМ счетчика результата, разрядные входы которого соединены соответственно с первыми выходами блока памяти, вход считывания кото4 рого соединен с третьим выходом втои рого распределителя импульсов, второй и третий ВЫХОДЫ блока памяти соединены соответственно с входами первого и второго слагаемых сумматоравычитателя , ВХОД задания режима ко торого соединен с четвертым выходом второго распределителя импульсов, ВХОД первого распределителя импульсов соединен с шийой пуска устройства , информационный вход устройства соединен с входом элемента И.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН, SU„„1 9744

А 1бц С 06 F 7/552

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3574412/18-24 (22) 07.04.83 (46) 23.08.84. Бюл. Р 31 (72) Ю.Л.Востяков и В.P.Òoëoêíîâñêèé (53) 681.325(088.8) (5e) 1. Авторское свидетельство СССР

У 642705, кл. G 06 F 7/552, 1976.

2. Авторское свидетельство СССР

У 993257, кл. G 06 F 7/552, 1981 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ПОЛУЧЕНИЯ

КВАДРАТИЧНОЙ ЗАВИСИМОСТИ, содержащее первый и второй двоичные делители частоты, первую и вторую группы элементов И, первый и второй элементы ИЛИ, сумматор-вычитатель, формирователь импульсов, регистр, счетчик результата, разрядные выходы которого соединены соответственно с разрядными входами регистра, вход записи которого соединен с выходом формирователя импульсов, вход которого соединен с выходом первого двоич" ного делителя частоты и входом записи числа сумматора-вычитателя, разрядные выходы которого соединены соответственно с первыми входами элементов И первой группы, вторые входы которых соединены соответственно с разрядными выходами первого двоич.ного делителя частоты, вход .которого соединен с входом элемента НЕ, выход которого соединен с входом второго двоичного делителя частоты, разрядные выходы которого соединены соответственно с первыми входами элементов И второй группы, вторые входы которых соединены соответственно с разрядными выходами регистра, выходы элементов И первой и второй групп соединены соответственно с входами первого и второго элементов ИЛИ, выход второго элемента ИЛИ является вьмодом устройства, о т л и ч а ю— щ е е с я тем, что, с целью расширения области применения путем получения возможности изменения параметров квадратичной зависимости, в него введены управляемый делитель частоты, блок памяти, первый и второй распределители импульсов, элемент И, первый вход которого соединен с первым вьмодом первого распределителя импульсов, второй выход которого соединен с входом второго распределителя импульсов, первый выход которого соединен с входом записи счетчика результата, второй выход второго распределителя импульсов соединен с входом установки коэффициента деления управляемого делителя частоты, вход которого соединен с выходом первого элемента ИЛИ, выход управляе- фаа мого делителя частоты соединен со фиы счетным входом счетчика результата, разрядные входы которого соединены цр соответственно с первыми выходами блока памяти, вход считывания которого соединен с третьим выходом второго распределителя импульсов, второй и третий выходы блока памяти соединены соответственно с входами первого и второго слагаемых сумматоравычитателя, вход задания режима которого соединен с четвертым выходом второго распределителя импульсов, вход первого распределителя импульсов соединен с шийой пуска устройства, информационный вход устройства соединен с входом элемента И.

1 1109

Изобретение относится к вычислительной технике и может найти применение в специализированных вычислителях информационно-измерительных систем линеаризации частотных измери5 тельных преобразователей при обработке информации с частотных датчиков.

Известно устройство для получения квадратичной зависимости, содержащее группу элементов И, элемент ИЛИ, 1О счетчик результата, элемент И и регистр Р1 3.

Недостаток данного устройства невозможность изменения параметров квадратичной зависимости. 15

Наиболее близким к предлагаемому по технической сущности является устройство для получения квадратичной зависимости, содержащее два делителя частоты, первый и второй двоичные делители частоты, первую и вторую группы элементов И, первый и второй элементы ИЛИ, сумматор-вычитатель, формирователь импульсов, регистр, счетчик. результата, разрядные д5 выходы которого соединены соответственно с разрядными входами регистра, вход записи которого соединен с выходом Формирователя импульсов, вход которого соединен с выходом первого двоичного делитепя частоты и входом записи числа сумматора вычитателя, разрядные выходы которого соединены соответственно с входами элементов И первой группы, вторые входы которых соединены соответственно с разрядны35 ми выходами первого двоичного делителя частоты, вход которого соединен с входом элемента НЕ, выход которого соединен с входом второго двоичного

40 делителя частоты, разрядные выходы которого соединены соответственно с первыми входами элементов И второй группы, вторые входы которых соединены соответственно с разрядными выходами регистра, выходы элементов И первой и второй групп. соединены со-, ответственно с входами первого и второго элементов ИЛИ, выход второго элемента ИЛИ является выходом устройства (21.

Однако известное устройство не позволяет изменять параметры квадратичной зависимости.

Цель изобретения — расширение об- 55 ласти применения путем получения возможности изменения параметров квадратичной зависимости.

744 2

Поставленная цель достигается тем, что в устройство для получения квадратичной завис 1мости, содержащее первый и второй двоичные делители частоты, первую и вторую группы элементов И, первый и второй элементы ИЛИ, сумматор-вычитатель, формирователь импульсов, регистр., счетчик результата, разрядные выходы которого соединены соответственно с разрядными входами регистра, вход записи которого соединен с выходом формирователя импульсов, вход которого соединен с выходом первого двоичного. делителя и входом записи числа, сумматора-вычитателя разрядные выходы которого соединены соответственно с первыми входами элементов И первой группы, вторые входы которых соединены с разрядными выходами первого двоичного делителя частоты, вход которого соединен с входом элемента НЕ, выход которого соединен с входом второго двоичного делителя частоты, разрядные входы которого соединены соответственно с первыми выходами элементов И второй группы, вторые входы которых соединены соответственно с разрядными выходами регистра выходы элементов И первой и второй групп соединены соответственно с входами первого и второго элементов ИЛИ, выход второго элемента ИЛИ является выходом устройства, введены управ: ляс-.мый делитель частоты, блок памяти, первый и второй распределители импульсов, элемент И, первый вход которого соединен с первым выходом первого распределителя импульсов, второй выход которого соединен с входом второго распределителя импульсов, первый выход которого соединен с входом записи счетчика результата, второй выход второго распределителя импульсов соединен с входом установки коэффициента деления управляемого депителя частоты, вход которогб соепинен с выходом первого элемента ИЛИ выход

Э управляемого делителя частоты соединен со счетным входом счетчика результата, разрядные входы которого соединены соответственно с первыми выходами блока памяти, вход считывания которого соединен с третьим выхоо дом второго распределителя импульсов, второй и третий выходы блока памяти соединены соответственно с входами первого и второго слагаемых сумматора-вычитателя, вход задания режима ко3 .110974 торого соединен с четвертым выходом второго распределителя импульсов, вход первого распределителя импульсов соединен с шиной пуска устройства, информационный вход устройства соеди5 нен с входом элемента И.

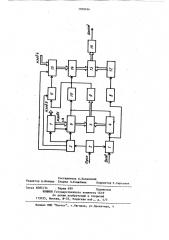

На чертеже приведена блок-схема предлагаемого устройства..

Устройство содержит элемент И 1, первый 2 и второй 3 распределители импульсов, первый двоичный делитель 4 частоты, первую группу элементов И 5, сумматор-вычитатель 6, блок 7 памяти, элемент НЕ 8, первый элемент ИЛИ 9, формирователь 10 импульсов, управляе- 15 мый делитель 11, второй двоичный делитель 12 частоты, вторую группу элементов И/ 13, регистр 14, счетчик 15 результата и второй элемент ИЛИ 16.

Устройство работает следующим

20 образом.

В исходном состоянии двоичные делители 4 и 12 частоты, сумматор-вычитатель 6, управляемый делитель 11, регистр 14 и счетчик 15 результата находятся в состоянии "О". По команде с шины пуска запускается первый распределитель 2 импульсов, который своим разрешающим сигналом с первого выхода открывает элемент И 1 для прохождения входной частоты на первый двоичный делитель 4 частоты и через элемент НЕ 8 на второй двоичный дели тель 12 частоты. Элемент НЕ 8 служит

;для согласования работы обоих двоич ных делителей частоты. Одновременно по переднему фронту разрешающего сигнала с второго выхода первого распределителя 2 импульсов во втором распределителе 3 импульсов вырабатывают40 ся сигналы для считывания из блока 7 хранения параметров начальных кодов

9 „И З„д ! вычитатель 6 и счетчик 15 результата, а также для установки коэффициента

45 передачи управляемого делителя 11 и. вырабатывается сигнал для перевода сумматора-вычитателя 6 на суммирование или вычитание кода ЬН по каждому импульсу переполнения первого двоич50 ного делителя 4 частоты.

4 4

На выходе первого элемента ИЛИ 9 проходит линейная последовательность импульсов (на первом участке проходит И9цд g — d N импульсов на втором

N „„„ +-26N импульсов и т.д.) и через уйравляемый делитель 11 поступает на вход счетчика 15 результата, в котором в зависимости от номера участка накапливается код квадратичной зависимости . Номер участка определяется количеством переполнений первого двоичного делителя 4 частоты. В счетчике 15 результата за и участков накопится

i(i+1)

+> i и +-- — -- аМ

За* 2 „3oA1 2 пульсов, где К вЂ . коэффициент передачи управляемого делителя 11.

Одновременно сигнал переполнения первого двоичного делителя 4 частоты поступает на вход формирователя 10 импульсов, который формирует импульс по переднему фронту сигнала переполнения и служит для записи кода счетчика 15 результата в регистр 14. На выходе второго элемента ИЛИ 16 получают квадратичную зависимость в последовательном коде в зависимости от номера участка или, что то же самое, от времени.

Таким образом, предлагаемое устройство позволяет в зависимости от номера участка или времени получить в параллельном коде в счетчике результат и в последовательном коде с выхода второго элемента ИЛИ или, что то же самое, с выхода устройства с любым углом наклона ветви параболы и с различными начальными условиями.

Одновременно с этим с выхода первого элемента ИЛИ можно получать линейную зависимость в последовательном коде и с выхода сумматора-вычитателя в параллельном коде с любым углом наклона прямой и с различными начальными условиями.

1109744

Составитель А. Казанский Редактор А.Мотыль Техред Л.Коцюбняк Корректор Е.Сирохман

Заказ 6085/34 . Тираж 699 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1130359 Москва, Ж-35, Раушская наб ., д. 4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4