Устройство для синхронизации воспроизведения оптоэлектронного запоминающего устройства

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ВОСПРОИЗВЕДЕНИЯ ОПТОЭЛЕКТРОЙНОГО ЗАПОМИНШВДЗГО УСТРОЙСТВА, содержащее пЬследовательно соединенные фазовый детектор, интегратор и управляемый генератор, первый блок фазовой автоподстройки частоты и диффёренцируюгдай йдок, вход которого является входом устройства, о т личающееся тем, что, с целью повышения точности синхронйэсщииг в него введены второй блок фазовой автоподстройки частоты , регистр сдвига, D-триггер и первый и второй мультиплексоры, причем выходы дифференцирующего блока подключены через первый и второй блоки фазовой автоподстройки частоты к информационному и синхронизирующему входам D-триггера, подсоединенного выходами к первым входам первого и второго мультиплексоров, информацион .ный вход регистра сдвига .соединен с выходом первого мультиплексора, первый и второй входы фазового детектора подключены к выходу второго мультиплексора и к выходу последнего разряда регистра сдвига, выход одного , из разрядов кото1юго является выходом устройства, при этом выход управляемого генератора подключен к синхро- § низирующему входу регистра сдвига, (Л . нулевые входы соответственно первого . и второго мультиплексоров подсоединены к синхронизирующему входу D-триг гера, информационный вход которого соединен с единичными входами перво- g го и второго мультиплексоров. со 00 о Од

СОЮЗ СОВЕТСНИ)(СОЦИАЛИСТИЧЕСКИ)(РЕСПУБЛИК

3(Ю 6 11 С 11 42

Т"

Ъ,!

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСРДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИИ И О ПОКРЫТИЙ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3611528/18-10 (22) 27.06. 83 (46) 23.08.84. Вюл. Р 31 (72) О.Ф.Вузин, A.À.Èèõàéëoâ, Т.Л.Нефедова и В.А.Чулков (5.3) 681. 327.66 (088. 8) (56) 1. Авторское свидетельство СССР

Р 832593, кл. G ll В 7/00, 1979.

2. Авторское свидетельство СССР

Р 841046, кл. G 11 С 11/42, 1979 (прототип) . (54) (57) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ВОСПРОИЗВЕДЕНИЯ ОПТОЭЛЕКТРОННОГО

ЗАПОИИНИОЩЕГО УСТРОЙСТВА, содержащее последовательно соединенные фазовый детектор, интегратор и управляемый генератор, первый блок фазовой автоподстройки частоты и дифференцирующий блок, вход которого является входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности синхронизации, в него введены вто рой блок фазовой автоподстройки частоты, регистр сдвига, D-триггер и

as> 0(ш . A. первый и второй мультиплексоры, причем выходы дифференцирующего блока подключены через первый и второй блоки фазовой автоподстройки частоты к информационному и синхронизирующему входам Р-триггера, подсоединенного выходамн к первым входам первого и второго мультиплексоров, информацион,ный вход регистра сдвига .соединен с выходом первого мультиплексора, первый и второй входы фазового детектора подключены к выходу второго мультиплексора и к выходу последнего разряда регистра сдвига, выход одного ,из разрядов которого является выходом устройства при этом выход управляеI

O мого генератора подключен к синхро- Е низнрующему входу регистра сдвига,,нулевые входы соответственно первого .и второго мультиплексоров подсоединены к синхронизирующему входу Р-триг

repa, информационный вход которого соединен с единичными входами перво- Я го и второго мультиплексоров °

1109806

Изобретение относится к области на

Э копчения информации, а именно к устройствам.дчя синхронизации воспроизведения оптоэлектронного запоминающего устройства.

Известно устройство для синхрони- 5 зации воспроизведения оптоэлектронного запоминающего устройства, содержащее блок Фазовой автоподстройки частоты j l 3.

Недостаток этого устройства состоит в недостаточной точности синхро низации, приводящей к срыву режима синхрониэма.

Известно также устройство для синхронизации воспроизведения оптоэлектронного запоминающего устройства, содержащее .последовательно соединенные делитель частоты, фазовый де.тектор, интегратор и управляемый генератор, дифференцирующий блок, сое". диненный с компаратором и детектором нуля j23.

Недостаток известного устройства недостаточная точность синхронизации при потенциальной записи сигналов .. 25

Цель изобретения — повышение точности синхронизации оптоэлектронного запоминающего устройства.

С этой целью в устройство для синхронизации воспроизведения оптоэлект- -ЗО ронного запоминающего устройства, содержащее последовательно соединенные фазовый детектор, интегратор и управляемый генератор, первый блок фаэовой автоподстройки частоты и диф" ференцнрующий блок, вход которого является входом устройства, введены второй блок фазовой автоподстройки частоты, регистр сдвига, 0-триггер и первый и второй мультиплексоры, причем к ходы Ежфференцирующего бло- 46 ка подключен через первый и второй блоки фазовой автоподстроки частоты к информационному и синхрониэирующему входам D-триггера, подсоединенного выходами к первым входам первого и 45 второго мультиплексоров, информационный вход регистра сдвига соединен с выходом первого мультиплексора, первый и второй входы фазового детектора подключены к выходу второго муль-56 типлексора и к выходу последнего разряда регистра сдвига, выход одного из разрядов которого является выходом устройства, при этом выход управляемого генератора подключен к синхронизирующему входу регистра сдвига, нулевые входы соответственно первбго и второго мультиплексоров подсоединены к синхронизирующему входу

0-триггера, информационный вход которого соединен с единичными входами ао первого и второго мультиплексоров.

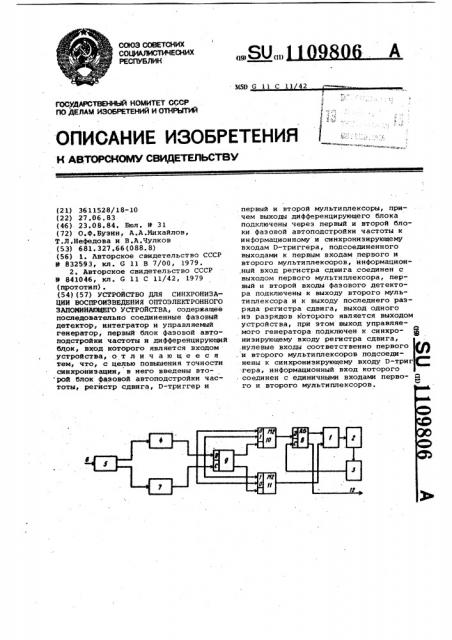

На чертеже приведен один из возможных вариантов устройства для синхронизации воспроизведения оптоэлектронного запоминающего устройства. 65

Устройство для синхронизации воспроизведения оптоэлектронного запоминающего устройства содержит последовательно соединенные фазовый детектор .

1, интегратор 2 и управляемый генератор 3, первый блок 4 .Фазовой автоподстройки частоты и дифференцирующий блок 5, вход которого является входом 6 устройства, а также второй блок

7 фазовой автоподстройки частоты, регистр 8 сдвига, 0-триггер 9 и первый и второй мультиплексоры 10 и 11 причем выходы дифференцирующего блока 5 подключены через первый и второй блоки 4 и 7 фазовой автоподстройки частоты к информационному и син" хронизирующему входам D-триггера 9, подсоединенного выходами к первым входам первого и второго мультиплексоров 10 и 11.

Информационный вход регистра 8 сдвига соединен с выходом первого мультиплексора 10, первый и второй входы фазового детектора 1 подключены к выходу второго мультиплексора и к выходу последнего разряда регистра

8 сдвига, выход одного из разрядов! которого является выходом 12 устройства, прн этом выход управляемого генератора 3 подключен к синхронизирующему входу регистра 8 сдвига, нулевой и единичный входы соответственно первого и второго мультиплексоров 10 и 11 — к синхронизирующему входу D-триггера 9, инФормационный вход которого соединен с единичным и нулевым входим первого и второго мультиплексоров 10 и 11.

Сигналы первого 4 и второго 7 блоков фазовой автоподстройки частоты с помощью дифференцирующего блока 5 отслеживают позиции соответственно фронта и спада воспроизведенного сиг" нала на входе 6. При отсутствии искажающих сдвигов фронта с спада входного сигнала сигналы обоих блоков 4 и 7 фазовой автоподстройки частоты совпадают по фазе, такую же фазу имеет и сигнал на выходе 12.

При наличии сдвигов Фронта и спада входного сигнала, которые при потенциальной оптической записи равны по величине и ориентированы противоположно, Фазы сигналов блоков 4 и 7 фазоной автоподстройки частоты. изменяются в противоположных направлениях относительно ноьивнальной позиции.

Мультиплексоры 10 и 11 с помощью

D-триггера 9 передают сигналы с блоков 4 и 7 фазовой автоподстройки частоты на входы фазового детектора 1, причем отстающий по фазе сигнал непосредственно, а опережающий - с задержкой, равной времени его прохождения через регистр 8 сдвига. Фазовый детектор 1 выявляет рассогласование по

Фазе между указанными сигналами и с помощью интегратора 2 корректирует

1109806

Составитель В.Добровольский

Редактор В.Данко Техред Л.Иартяшова Корректор О «Луговая

Заказ 609 1/37 Тираж 575 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Косква Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. ужгород, ул. Проектная, 4 частоту управляемого генератора 3 вилоть до полной компенсации рассогласования. Поскольку в установившемся режиме фазы сравниваемых фазовым детектором 1 сигналов совпадают,,а выход 12 берется со среднего разряда регистра 8 сдвига, то, следовательно, фаза сигнала на выходе 12 соответствует номинальной позиции фронта и спа. да входного сигнала, Использование изобретения позволяет значительно повысить точность синхронизации, в результате чего на порядок снижается вероятность срыва синхроннзма.