Интерполирующий фильтр

Иллюстрации

Показать всеРеферат

ИНТЕРПОЛИРУКШЩЙ ФИЛЬТР,- содержащий последовательно соединенные элемент сравнения, первый вход которого является входом интерполирующего фильтра, ограничитель, первьй интегратор, блок задержки и сумматор , а также четыре блока вычитания, пять масштабирующих элементов и блок памяти, при этом второй вход элемента сравнения подключен к выходу первого интегратора, отличающ и и с я тем, что,, с целью повьш1ения точности фильтрования в него введены второй, третий, четвертый и пятый интеграторы, четыре блока умножения и задатчик, при этом последовательно соединенные второй интегратор, первый блок вычитания и первьй блок умножения включены между выходом ограничителя и вторым входом .сумматора , последовательно соединенные третий интегратор, второй блок вычитания и второй блок умножения включены между выходом первого блока вычитания и третьим входом сумматора, последовательно соединенные первый масштабирующий элемент, четвертый интегратор, третий блок вычитания и третий блок умножения включены между выходом второго блока вычитания и четвертым входом сумматора, последовательно соединенные второй масштабирую1щй элемент, пятый интегратор , четвертый блок вычитания и четвертый блок умножения включены между выходом третьего блока вычитания и пятым входом сумматора, последовательно соединенные блок памяти, выход которого подключен к второму входу первого блока вычитания, третий масштабирующий элемент, выход которого подключен к второму входу С0 00 второго блока вычитания, четвертый ма штабирукяций элемент, выход которого подключен к второму входу третьесо го блока вьиитания, и пятый масштабиру ощий элемент включены между выходом второго интегратора и вторым входом четвертого блока вычитания, причем выход задатчика подключен к вторым входам первого, второго, третьего и четвертого блоков умножения.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (д) Н 03 Н 17/06

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ соединенные второй интегратор, первый блок вычитания и первый блок умножения включены между выходом ограничителя и вторым входом .сумматора, последовательно соединенные тре-. тий интегратор, второй блок вычитания и второй блок умножения включены между выходом первого блока вычитания и третьим входом сумматора, последовательно соединенные первый масштабирующий элемент, четвертый интегратор, третий блок вычитания и третий блок умножения. включены между выходом второго блока вычитания и четвертым входом сумматора, последовательно соединенные второй масштабирующий элемент, пятый интегратор, четвертый блок вычитания и четвертый блок умножения включены между выходом третьего блока вычитания и пятым входом сумматора, последовательно соединенные блок памяти, выход которого подключен к второму входу первого блока вычитания, третий масштабирующий элемент, выход которого подключен к второму входу второго блока вычитания, четвертый масштабирующий элемент, выход которого подключен к второму входу третьего блока вычитания, и пятый масштабирующий элемент включены между выходом второго интегратора и вторым входом четвертого блока вычитания, причем выход задатчика подключен к вторым входам первого, второго, третьего и четвертого блоков умножения. (21) 3575357/18-09 (22) 07.04.83 (46) 23.08.84. Бюл. Ф 31 (72) В.П.Авдеев, Л.А.Сульман, А.А.Берлин и Л.П.Иышляев .(71) Сибирский ордена Трудового Красного Знамени металлургический институт им. Серго Орджоникидзе и ЦентЕ ральное проектно-конструкторское бюро по системам автоматизации производства (53) 621.396.6 (088.8) (56) 1. Ицкович Э.Л. Контроль производства с помощью вычислительных машин. M. "Энергия", 1975, с. 39.

2. Авторское свидетельство СССР

У 1030958, кл. Н 03 Н 17/06, 1982 (прототип) . (54) (57) ИНТЕРПОЛИРУЮЩИЙ ФИЛЬТР,. содержащий последовательно соединенные элемент сравнения, первый вход которого является входом интерполирующего фильтра, ограничитель, первый интегратор, блок задержки и сумматор, а также четыре блока вычитания, пять масштабиру ющих элементов и блок

1 памяти, при этом второй вход элемента сравнения подключен к выходу первого интегратора, о т л и ч а ю— шийся тем, что с целью повьппения точности фильтрования в него введены второй, третий, четвертый и пятый интеграторы, четыре блока учножения и задатчик, при этом последовательно,SU„„1109 91 А

Ф i 109891 3

Изобретение относится к радиотех- зано с повышением с нике и может быть использовано для ства. запаздывающего выделения полезной Кроме того, упом низкочастотной составляющей измерен- находятся между зна ных сигналов, которая может быть 5 сигнала x(t-8-;), от применена, например, при решении за- ным моментам времен дач запаздывающего моделирования, а временного интервал также в обучающихся по предыстории и только одним зпач системах. тельно сглаженного

Известен интерполирующий фильтр, 10 тем самым не исполь содержащий блоки задержки, выходы к моменту времени которых через масштабирующие блоки ция о значениях пре подключены к блоку суммирования (15, сглаженного сигнала

Недостаток интерполирующего времени lt- c, фильтра заключается в низкой точности1 Целью изобретени фильтрации. шение точности филь

Наиболее близким к изобретению

Цель достигается по технической сущности является полирующий фильтр, интерполирующий фильтр, содержащий довательно соединен последовательно соединенные элемент 20 нения, первый вход сравнения, ограничитель, интегратор, ся входом.интерполи блок задержки и сумматор, и блоков ограничитель, первы памяти (и+1) блоков вычитания, блок задержки и су (и+1) блоков ограничения и (и+1) четыре блока вычита масштабирующих элементов, при этом 2S табирующих элемента выход интегратора подключен к второпри этом второй вхо му входу элемента сравнения, первый нения подключен к в вход которого является входам устинтегратора, введен ройства,i- é блок памяти, i-й блок четвертый и пятый и вычитания, i-й блок ограничения и ре блока умножения -й масштабирующий элемент (1=1,2,. том последовательно ..n) включены последовательно между второй интегратор, входом устройства и (i+1)-ым входом читания и первый бл сумматора, (n+1) -й блок вычитания, включены между выхо (п+1)-й блок ограничения и (п+1)-й и вторым входом сум масш абирующий элемент включены повательно соединенны ва и (a+2)-ым входом сумматора, а блок умножения вклю выход блока задержки соединен с вто рым входом блока вычитания Е23, 30

Недостатком известного интерполирующего фильтра является низкая точность фильтрации, так как уточнение предварительно сглаженного 45 сигнала х" (t- Q производится по конечному числу, равному и+1, разностей между этим сигналом и значениями входного сигнала устройства на интервале времени Ct 2, tj, а не по всем значениям разностей соответствующих непрерывных сигналов внутри указанного отрезка времени.

Повысить точность выделения полезного сигнала с помощью известного 55 интерполирующего фильтра можно путем увеличения количества (и+1) учитываемых разностей, -однако это свяложности устройянутые разности чениями входного носящимися к рази t-8> внутри а tt- ь, tl, ением предварисигнала х "(t- . ), зуется полученная полезиая информадварительно внутри отрезка я является повытрации., тем, что в интерсодержащий посленые элемент сравкоторого являетрующего фильтра., и интегратор, мматор, а также ния, пять масшв и блок памяти, д элемента сравыходу первого

ы второй, третий, нтеграторы, четыи задатчик, при соединенные первый блок вьюк умножения дом ограничителя матора, последое третий интеграиитания и второй чены между выхоычитания и третьим входом сумматора, последовательно соединенные первый масштабирующий элемент, четвертый интегратор, третий блок вычитания и третий блок умножения включены между выходом второго блока вычитания и четвертым входом сумматора, последовательно соединенные второй масштабирующий элемент, пятый интегратор, четвертый блок вычитания и четвертый блок умножения включены между выходом третьего блока вычитания и пятым входом сумматора, последовательно соединенные блок памяти, выход которого подключен к второму входу первого блока вычитания, третий масштабирующий элемент, выход которого подключен к второму входу второго блока вычитания, четвертый масштабирующий

1109891 элемент, выход которого подключен к второму входу третьего блока вычитания, и пятый масштабирующий элемент включены между выходом второго интегратора и вторым входом 5 четвертого блока вычитания, причем выход задатчика подключен к вторым входам первогп, второго, третьего и четвертого блоков умножения.

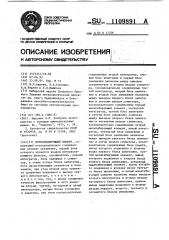

На чертеже представлена структурная электрическая схема интерполирующего фильтра.

Интерполирующий фильтр содержит последовательно соединенные элемент

1 сравнения, ограничитель 2, первый интегратор 3, блок 4 задержки и сум— матор 5, причем выход первого интегратора 3 связан с вторым входом элемента 1 сравнения, первый вход которого является входом фильтра, последовательно соединенные второй интегратор 6, вход которого подключен к выходу ограничителя 2, первый блок 7 вычитания, третий интегратор

8, второй блок 9 вычитания, первый масштабирующий элемент 10, четвертый интегратор 11, третий блок 12 вычитания, второй масштабирующий элемент

13-, пятый интегратор 14 и четвертый блок 15 вычитания, последовательно соединенные блок 16 памяти, третий масштабирующий элемент 17, четвертый масштабирующий элемент 18 и пятый масштабирующий элемент 19, подключенные между выходом второго З интегратора 6 и вторым входом четвертого блока 15 вычитания, входы третьего 17, четвертого 18 и пятого

19 масштабирующих элементов объединены с вторыми входами соответствен — 40 но первого, второго и третьего блоков 7, 9 и 12 вычитания, задатчик

20, первый, второй, третий и четвертый блоки 21-24 умножения, первые входы которых соединены с выходами 45 соответствующих блоков 7, 9, 12 и 15 вычитания, вторые входы соединены с выходом задатчика 20, а выходы подключены к второму, третьему, четвертому и пятому входам сумматора 5. у) На чертеже обозначены x(t) — входной сигнал устройства; x(t- ) сглаженный сигнал на выходе устройства.

- Интерполирующий фильтр работает следующим образом .

Входной сигнал x(t) предварительно сглаживается фильтром низкой частоты, состоящим из элемента 1 сравнения, ограничителя 2 и первого интегратора 3. С этой целью сигнал

x(t) поступает на первый вход элемента 1 сравнения, где из него вычитается выходной сигнал фильтра низкой частоты x (t), — ïoñòóïàþùèé с выхода первого интегратора 3 ° Полученная разность поступает на вход ограничителя 2, который может быть реализован, например, в виде усилителя с насыщением. Если сигнал Е"(t) превышает ве.личину ограничивающего напряжения то в ограничителе 2 он ограничивается до этой величины. Это можно представить выражением где о () — выходной сигнал ограничителя 2;

Сигнал 3() поступает на вход первого интегратора 3 и интегрируется в нем. С выхода первого интегратора 3 предварительно сглаженный фильтром низкой частоты сигнал х"(t) подается на вход блока 4 задержки, где запоминается на интервал времени Ъ . Сигнал х"(t- 7) с выхода блока 4 задержки поступает на первый вход сумматора 5.

Выходной сигнал интерполирующего фильтра формируется путем уточнения предварительно сглаженного сигнала х"(t- ь ) по разностям между значе-,, ниями этого сигнала и входного сигнала устройства на интервале времеLt tэ

С этой целью сигнал &(й) с выхода ограничителя 2 поступает на вход второго интегратора 6, в котором он интегрируется. Сигнал с выхода второго интегратора 6 поступает на вход блока t6 памяти, в котором он задерживается на интервал времени и далее на вход первого блока 7 вычитания, в котором он вычитается из сигнала с выхода второго интегратора 6, Сигнал с выхода первого блока 7 вычитания поступает на вход третьего интегратора 8, в котором он интегрируется. Сигнал с выхода блока 16 па1109891 мяти подается на вход третьего масш- табирующего элемента 17, умножается в нем на коэффициент,= и поступает далее на вход второго блока 9 вычитания, в котором он вычитается S из сигнала с выхода третьего интегратора 8.

Сигнал с выхода второго блока 9 вычитания поступает на вход первого. масштабирующего элемента 10, умножа- 10 ется в нем на коэффициент »,= 2 и подается далее на. вход четвертого интегратора I 1, в котором он интегрируется. Сигнал с выхода третьего масштабирующего элемента 17 подается на вход четвертого масштабирующего элемента 18, умножается в нем на коэффициент gt,- и поступает далее на вход третьего блока 12 вычитания, в котором он вычитается из сигнала с выхода четвертого интегратора 11.

Сигнал с выхода третьего блока

12 вычитания поступает на вход второго масштабирующего элемента 13, умнсжается в нем на коэффициент IIg 3 и пддается далее на вход пятого интегратора 14, s котором он интегрируется. Сигнал с выхода четвертого масштабирующего элемента 18 подается на вход пятого масштабирующего 30 элемента 19, умножается в нем на коэффициент ф 7, и поступает далее на вход четвертого блока 15 вычитания, в котором он вычитается из сигнала с выхода пятого интегратора 14.

Коэффициенты усиления второго, третьего, четвертого и пятого интеграторов 6, 8, 11 и 14 устанавливаются равными единице. 40

Передаточная функция схемы, состоящей из блоков 6, 7 и 16 имеет вид

%,(Р).-"Й-е ), где — — передаточная функция ин- 45

P тегратора, — передаточная функция блока

16 памяти, а соответствующая импульсная характерис50 тика (3) (4) (5) (М=м.(w,е<м-ц ю ж(а) =

«И,4фЦ 6А-Ь Э, если 0 6 ; О еаа б>, а выходной дх(-E ) сигнал этой схемы формируется в соответствии с выражением

R(t-tl.e "Ы) af(e -eÈÛÌI-««(<-g)gy(g о (2) Коэффициенты 1о, 8 62, Устанавливаются на выходе задатчика 20 таким образом, чтобы обеспечить ю®.f4 е Ойюй Е

L0, ест ОЛ;

Передаточная функция схемы, состоящей из блоков 6, 7, 8, 9, 16 и

17, имеет вид

Ф4{р1-ф,(4-eg-ô å а соответствующая импульсная характеристика (6) 8, если Ойб<4 0, Фс4м фЛ

Передаточная функция схемы, состоящей из блоков 6, 7, 8, 9, 10, 11, 12, 16, 17 и 18, имеет вид

% (р1 -тй-e ) ф e -4 Ф е а соответствующая импульсная характеристика

«(Ф если О» Э ® (O ли Ъ

Передаточная функция схемы, состоящей из блоков 6-19, имеет вид

Ф,ф) P(i-е")--ф е -ф&а - Уф@.e- а соответствующая импульсная характеристика

Щ ясли 0@8<7., +gOA (ц, если а>

Сигналы с выходов блоков 7, 9, 12 и 15 вычитания поступают- на первые входы соответствующих блоков

21-24 умножения, умножаются в них на коэффициенты 4, f„, К и f> задаваемые с выхода задатчика 20 на вторые входы блоков 21-24 умножения, и подаются далее на второй, третий, четвертый и пятый входы сумматора 5; в котором они суммируются, в результате чего получается сигнал ax(t- С).

Импульсная характеристика схемы, входом которой является входной сигнал Р (й) второго интегратора 6, а выходом — результат суммирования

a,õ(t- ), имеет вид

10

7 11098 желаемую весовую функцию, например, спадающую в будущее по экспоненте где а и ot. — постоянные коэффициенты

Сигнал дх(-ь ) с учетом (6) и (7) формируется в соответствии с выражением, ьх(1-2). а(е"1М"(1 6)сЖ о

Сигнал дх(с- ь ) в первом сумматоре 5 суммируется с предварительно л сглаженным сигналом X(t- ь ), в результате чего получается выходной сигнал интерполирующего фильтра

"С" " 9 Й " 4 I- "Ct-eggs (8) где Ц1(х®-б)-х1 (Щ) определяется в соответствии с выражением (1) .

ВНИИПИ Заказ 6100/41

Тираж 862 Подписное

- Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Уточнение предварительно сглаженного сигнала х (t-i ) в предлагае"н мом устройстве производится по всем значениям разностей между входным сигналом фильтра и предварительно сглаженным сигналом внутри интервала времени (t- 5, t3, а не по конечному числу этих разностей как в известном устройстве. Кроме того в

Ф пр едл ar аемом фильтр е в отличие от известного определяются разности между значениями входного и предварительно сглаженного сигналов, относящихся к одному и тому же моменту времени, тем самым используется полученная к моменту времени t полезная информация о значениях предварительно сглаженного сигнала внутри отрезка времени ?t-, tJ. Bce это обеспечивает повышение точности выделения полезного сигнала.

Таким образом, предлагаемый интерполирующий фильтр позволяет повысить точность запаздывающего выделения полезного сигнала.